引言

數據中心運維人員總是不斷在尋求更高的服務器性能。目前,他們主要是通過易于編程的多核CPU 和GPU 來開發應用,但CPU 和GPU 都遇到了單位功耗性能的瓶頸壁壘。從事海量數據中心應用開發(如密鑰加速、圖像識別、語音轉錄、加密和文本搜索等)的設計人員既希望GPU 易于編程,同時又希望硬件具有低功耗、高吞吐量和最低時延功能。然而,多核CPU和GPU 加速器在可擴展性上存在嚴重的問題:客戶希望用簡單的全高度插入式PCIe開發板作為數據中心服務器的應用加速器。這種開發板經配置可運行高功率圖形卡,但客戶同時希望功耗不超過25W,以便最大化可擴展性并最小化總功耗。

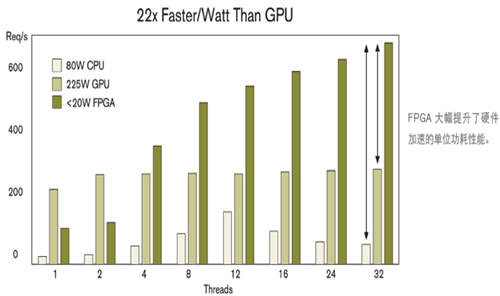

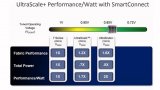

最近賽靈思同瑞士蘇黎世聯邦理工學院(ETH Zurich)聯合開展的一系列研究發現,基于FPGA 的應用加速想比CPU/GPU實現方案,單位功耗性能可提升25 倍,而時延則縮短了50 到75 倍,與此同時還能實現出色的I/O 集成(PCIe、DDR4SDRAM 接口、高速以太網等)。換言之,FPGA 能在單芯片上提供高能效硬件應用加速所需的核心功能,并同時提供每個開發板目標功耗低于25W 的的解決方案。

中國網絡服務領先企業百度公司在美國加州圣何塞舉行的2014年熱門芯片研討會上介紹了支持性調查結果。百度的結論如下:

? 中端FPGA 能夠實現375 GFLOPS 的性能,功耗僅為10-20W

? 基于FPGA 的加速器可部署在所有類型的服務器中。

? 和CPU 和GPU 相比, FPGA 在深度神經網絡(DNN)預測系統中性能更加出色。DNN 系統用于語言識別、圖像搜索、OCR、面部識別、網頁搜索以及自然語言處理等各種不同應用。

FPGA 用于應用加速的最大問題在于編程。數據中心應用開發人員不希望采用以硬件為中心的RTL 流程,也就是傳統FPGA的開發路徑。他們所需要的是:

? 單位功耗性能更高

? 完全軟件的開發環境

? 易于升級的設計

推出全新賽靈思SDAccel 環境

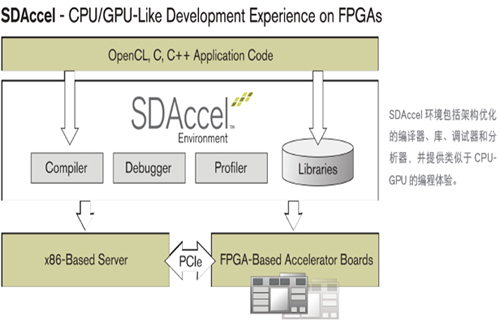

全新的賽靈思SDAccel 開發環境為數據中心應用開發人員提供了他們所需要的完整的FPGA 軟硬件解決方案。SDAccel 包括可高效利用片上FPGA 資源的快速的、架構優化的編譯器;熟悉的軟件開發流程—— 其帶有用于代碼開發、特性分析與調試的Eclipse 集成設計環境(IDE),可提供類似于CPU/GPU 的工作環境;以及針對不同數據中心應用而優化的動態可重配置加速器,能在類似CPU/GPU 運行時間環境中即時更換。運行過程中應用能讓不同處理模塊在FPGA 中即時替換,且不會干擾服務器CPU 和FPGA 之間的連接,實現不間斷的應用加速。

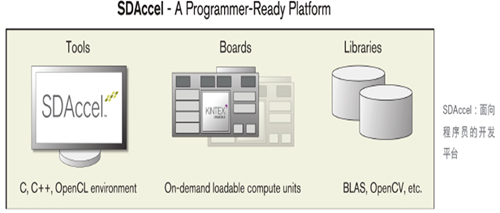

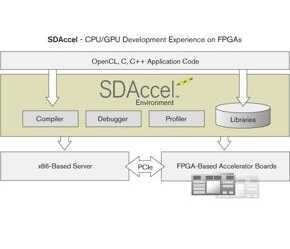

SDAccel 結合業界首款架構優化編譯器、庫和開發板,是唯一能在FPGA 上提供類似于CPU/GPU 的開發和運行時間體驗。SDAccel 開發環境面向基于X86 服務器處理器的主機系統,并可提供現成的商用(COTS)PCIe 插卡,用于添加FPGA 功能。

行業首款面向C、C++ 和OpenCL 的架構優化編譯器

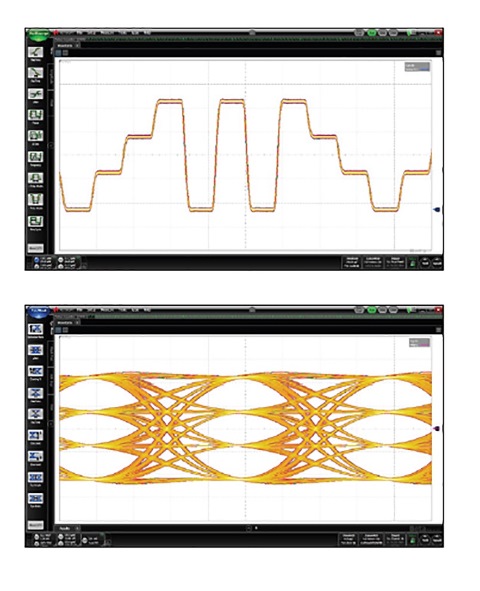

SDAccel 的架構優化編譯器使軟件開發者能夠優化并編譯流媒體、低時延以及定制數據路徑應用。SDAccel 編譯器主要針對高性能賽靈思FPGA 并支持OpenCL,C 和C++ 任意組合的源代碼。SDAccel 編譯器相比高端CPU 性能提高達10 倍,而功耗僅為GPU 的1/10,同時能保持代碼的兼容性和一個傳統的軟件編程模式,以便于應用移植并節約成本。根據客戶基準,SDAccel 編譯器相比同類競爭FPGA 解決方案,性能和資源效率均提升了3 倍。SDAccel 編譯器自動生成的設計甚至比手動編碼的RTL 設計方案的性能還高,在某些情況下可高出20% 之多。

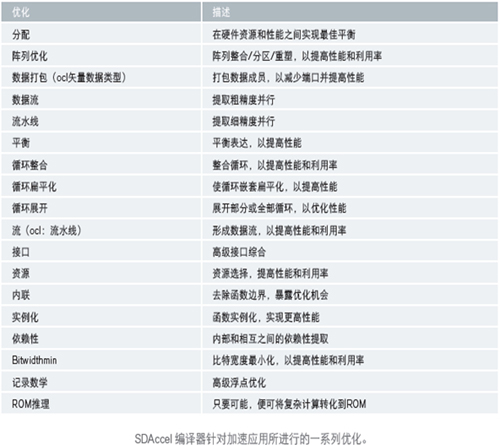

架構優化的SDAccel 編譯器可以自動對應用源代碼實施一系列基礎甚至高級的優化方案。下表列出了SDAccel 編譯器針對加速應用所進行的一系列優化。

其中一些自動優化能大幅提升整體應用的效率。舉例來說,SDAccel 編譯器的數據流流水線功能可對多個功能進行流水線化,而不會局限于僅能對單一功能進行優化。該編譯器的存儲器優化功能能極大地提升功效,從而讓你能夠在FPGA 中添加更多功能。SDAccel 是首款面向FPGA 平臺的完全軟件的開發環境,可實現類似于CPU/GPU 的開發體驗。開發人員能用熟悉的工作流程優化應用,而且即便很少或者沒有FPGA 使用經驗,也能獲益于FPGA 的平臺優勢。集成設計環境(IDE)不僅可提供編碼模板和軟件庫,而且還支持在x86 平臺上進行編譯、調試、特性分析和FPGA 仿真。準備好部署后,IDE 能在配有自動儀器插入功能的數據中心用現成的商用 FPGA 平臺上實現算法。

SDAccel 還經過精心構建,使CPU/GPU 開發人員能夠輕松將其應用移植到FPGA 上,同時還可在熟悉的工作流程中維護和復用OpenCL、C 和C++ 代碼。大量代碼和庫采用C 和C++ 格式。對于希望采用其現有代碼庫中的不同代碼,或者采用第三方代碼庫,甚至繼續組合使用C、C++ 或OpenCL 進行開發的開發者來說,能用C、C++ 或OpenCL 工作是最大的便利。

SDAccel 環境配套提供面向程序員的Eclipse IDE 以及一系列基于C 語言的FPGA 優化庫和數據中心用現成商用平臺。Convey Computer、Alpha Data Parallel Systems 和Pico Computing 公司可提供數據中心用加速板卡。2015 年年初還將增加更多商用現貨(COTS)合作伙伴。SDAccel 庫包括內置OpenCL 函數、DSP、視頻和線性代數庫,能支持高性能低功耗實現方案。針對特定領域加速,賽靈思聯盟合作成員Auviz Systems 公司還提供優化的 OpenCV 和BLAS SDAccel 兼容庫。

應用開發人員完全能在X86 仿真空間開始使用SDAccel 使其代碼開始工作。一旦其確信其算法開發人員就能對代碼進行特性分析,找到受益于加速的代碼片段。然后開發人員就可以利用這些有針對性的片段,無縫采用快速自動生成的周期精確內核仿真,從而實現加速。這些快速仿真可用來調試和優化加速量,同時能在架構層面工作。業經驗證的應用能方便地移植到主機/FPGA 系統。SDAccel 開發環境可支持所有這些來自同一控制中心(cockpit)的活動。

SDAccel 庫對SDAccel 類似CPU/GPU 的開發體驗發揮了重要作用。這些庫包含底層數學庫以及BLAS、OpenCV 和DSP 等高生產力庫。這些庫用C++(而不是用RTL)編寫,因此在所有開發和調試階段都能完全像編寫一樣使用。在項目早期階段,所有開發工作都在CPU 主機上進行。由于SDAccel 庫用C++ 語言編寫,因此能與CPU 目標的應用代碼一起編譯,創建虛擬設計原型,讓所有測試、調試和初始特性分析工作在主機上進行。在此階段無需FPGA。

一旦應用經過初始調試和特性分析,需要硬件加速的關鍵功能可通過編譯實現協同仿真,加速功能運行在基于CPU 的RTL仿真器上。這時,軟件開發團隊可觀察所得的性能,確定應用能否滿足性能目標要求。RTL 仿真能準確給出FPGA 硬件加速的性能情況,這就能讓開發團隊得到很好的性能估算,而且能高度確保所得的FPGA 配置能精確重現應用源代碼的行為和結果。

加速功能隨后可遷移到FPGA 上,生成最后的加速應用,可用于部署。SDAccel 編譯器不是創建通用FPGA 配置,而是在編譯時針對特定的賽靈思FPGA,包括器件速度等級,這樣所得的加速功能就能針對FPGA 上的可用資源以及器件時序進行優化。在這時我們甚至還能測試功能,這對性能不會造成影響,硬件開銷極低,而且還能在同樣熟悉的SDAccel 開發環境中進行更多后期特性分析,以便充分利用FPGA 硬件,全面最大化應用加速效果。

CPU 級特性分析能發現應用瓶頸。協同仿真將告訴您這些瓶頸是否已經被加速特定功能消除掉。在FPGA 上對硬件加速功能進行特性分析能實現更多優化,進一步優化應用代碼和加速功能。在任何時間以及各個階段中,SDAccel 編譯器都可選擇性地檢測應用代碼,包括加速功能,這就意味著調試和特性分析能夠以相同方式進行,而且無論開發工作進入到哪個階段,都可用使用同一軟件開發工具。

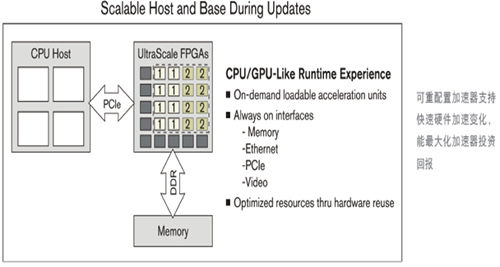

在FPGA 上首次帶來類似CPU/GPU 的運行時間和升級體驗

SDAccel 可提供支持實時類似CPU/GPU 運行時間升級的唯一FPGA 動態可重配置加速器。SDAccel 對于FPGA 解決方案的獨特之處在于其利用唯一的FPGA 動態重配置功能可在內核升級時保持系統繼續運行,這不僅可加載新的硬件加速器內核(這一點與CPU/GPU 加速器的功能類似),同時還能保持關鍵的系統接口和功能(如存儲器、以太網、PCIe 和性能監控器)繼續發揮作用。這種即時的系統重配置功能理想適用于數據中心計算需求及負載的立即更新。這種應用的一個實例就是圖像搜索、視頻轉碼和圖像處理等功能的即時切換,從而帶來戰略性優勢。

所有這些都能通過硬件重用轉換為資源優化,這在數據中心環境中是一大優勢。簡而言之,基于SDAccel 的系統現在能加速應用,而如果未來需要另外一種類型的加速,系統能快速順利地實現升級。

開發者可以管理和運行基于SDAccel 的系統就像在CPU/GPU 系統一樣。利用SDAccel 和硬件快速動態重配置功能,我們甚至能在應用運行中重用FPGA。這種功能使得我們能用相同的FPGA 板卡執行不同的內核加速,硬件可針對不同的算法進行重新優化,且不會限制或中斷應用流程。通過支持動態重配置,SDAccel 能讓數據中心運維人員最大限度地發揮硬件加速投資價值。

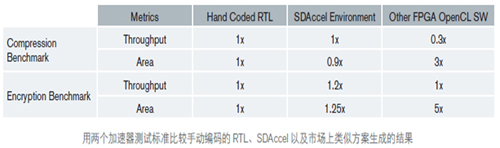

實實在在的標準測試可證明SDAccel 的性能和價值

SDAccel 經過了具有實際標準測試的業界驗證。舉例來說,在壓縮標準測試中,SDAccel 生成的硬件加速器比同類競爭工具生成的加速器速度高3 倍多,尺寸小3 倍。占位面積及吞吐量與手動優化的RTL 實現方案旗鼓相當甚至更優秀。

在上述的加密標準測試中,SDAccel 生成的硬件加速器比同類競爭工具生成的加速器速度快1.2 倍,而面積小4 倍。更棒的是,SDAccel 自動生成的加速器比用RTL 手動編碼生成的加速器還快20%。SDAccel 開箱即用,可直接編加速器,而且QOR(結果質量)與手動編碼結果質量旗鼓相當,甚至更勝一籌。

結論

SDAccel 可滿足數據中心應用開發人員的需求,包括提供類似CPU/GPU 的工作環境,其生成的高效硬件加速器可實現最佳單位功耗性能,遠勝于運行在CPU/GPU 上的加速器。SDAccel 通過帶有系統內即時可重配置功能的單個控制中心環境(cockpit environment)支持軟件工作流程,最大化數據中心硬件加速投資回報。因此,SDAccel 是一種獨特而完整的FPGA解決方案,其易用性和功能遠超同類競爭性工具。這些同類競爭性工具不能提供高生產力工作流程,也不能提供熟悉的環境,加速器性能更不能與SDAccel 自動生成的硬件加速器相提并論。

電子發燒友App

電子發燒友App

評論