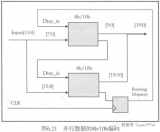

為了在USB 3.0中實(shí)現(xiàn)數(shù)據(jù)的8 b/10 b編解碼,把8b/10b編解碼分解成5 b/6 b編解碼和3 b/4 b編解碼,然后在FPGA上實(shí)現(xiàn)了具體的硬件電路。

2011-11-30 11:38:18 2803

2803

以下是筆者一些關(guān)于FPGA功耗估計(jì)和如何進(jìn)行低功耗設(shè)計(jì)的知識(shí)。##關(guān)于FPGA低功耗設(shè)計(jì),可從兩方面著手:1)算法優(yōu)化;2)FPGA資源使用效率優(yōu)化。

2014-12-17 09:27:28 9177

9177 這里將介紹SERDES的基本概念,并介紹SERDES相關(guān)的專有名詞:眼圖(Eye-diagram)、眼圖模板、抖動(dòng)(Jitter)、容忍度(tolerance)、功耗(Power Consumption)、預(yù)加重(Pre-emphasis)、均衡(Equalization)、8B/10B編碼等。

2018-01-30 08:55:54 22436

22436

看準(zhǔn)FPGA高集成度、可重構(gòu)和低功耗的發(fā)展趨勢(shì),一直致力于提供能滿足不同應(yīng)用場(chǎng)合“可定制可重構(gòu)可編程”設(shè)計(jì)需求的產(chǎn)品,并向FPGA的SoC化逐步邁進(jìn)。 京微雅格從中低端市場(chǎng)切入,逐步發(fā)力高端市場(chǎng)

2013-08-22 14:46:48

8b/10b編碼用的控制字是K28.5,但是解碼時(shí)用非K28.5的控制字能把數(shù)據(jù)解碼出來嗎?

2019-01-02 14:47:15

串行接口常用于芯片至芯片和電路板至電路板之間的數(shù)據(jù)傳輸。隨著系統(tǒng)帶寬不斷增加至多吉比特范圍,并行接口已經(jīng)被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨(dú)立

2019-10-23 07:16:35

FPGA的功耗高度依賴于用戶的設(shè)計(jì),沒有哪種單一的方法能夠?qū)崿F(xiàn)這種功耗的降低,如同其它多數(shù)事物一樣,降低功耗的設(shè)計(jì)就是一種協(xié)調(diào)和平衡藝術(shù),在進(jìn)行低功耗器件的設(shè)計(jì)時(shí),人們必須仔細(xì)權(quán)衡性能、易用性、成本

2015-02-09 14:58:01

FPGA的功耗高度依賴于用戶的設(shè)計(jì),沒有哪種單一的方法能夠?qū)崿F(xiàn)這種功耗的降低,在進(jìn)行低功耗器件的設(shè)計(jì)時(shí),人們必須仔細(xì)權(quán)衡性能、易用性、成本、密度以及功率等諸多指標(biāo)。

2019-08-29 07:52:29

目前許多終端市場(chǎng)對(duì)可編程邏輯器件設(shè)計(jì)的低功耗要求越來越苛刻。工程師們?cè)谠O(shè)計(jì)如路由器、交換機(jī)、基站及存儲(chǔ)服務(wù)器等通信產(chǎn)品時(shí),需要密度更大、性能更好的FPGA,但滿足功耗要求已成為非常緊迫的任務(wù)。而在

2019-07-15 08:16:56

到至少4個(gè)無錯(cuò)誤的連續(xù)/K28.5/符號(hào)時(shí),RX同步,然后將SYNC~引腳拉高。d、RX必須接收到至少4個(gè)無錯(cuò)誤8B/10B字符,否則同步將失敗,鏈路留在CGS階段。e、CGS階段結(jié)束,ILAS階段開始

2019-12-03 17:32:13

接收到至少4個(gè)無錯(cuò)誤8B/10B字符,否則同步將失敗,鏈路留在CGS階段。e、CGS階段結(jié)束,ILAS階段開始。注意:a、串行數(shù)據(jù)傳輸沒有接口時(shí)鐘,因此RX必須將其數(shù)位及字邊界與TX串行輸出對(duì)齊。RX

2019-12-04 10:11:26

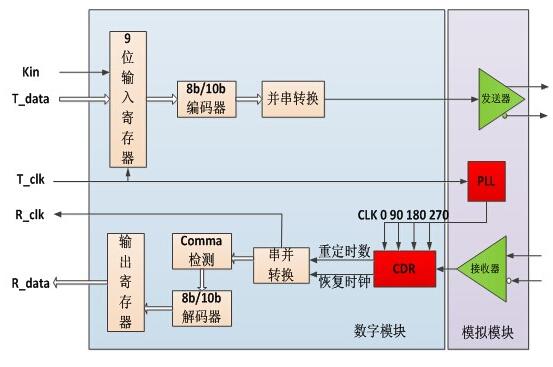

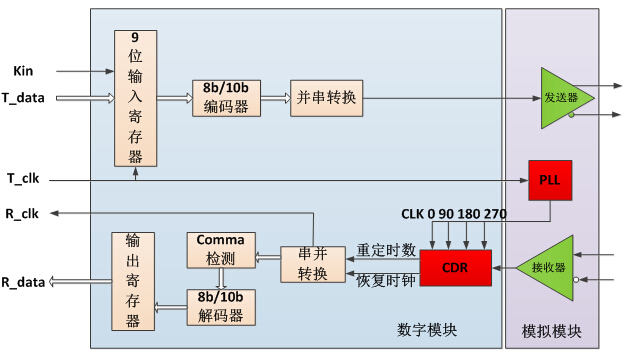

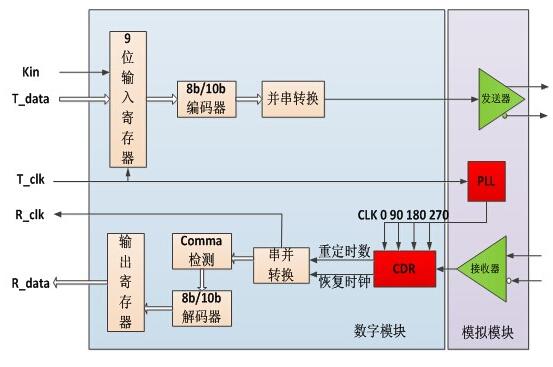

通信,該SERDES接口方案具有成本低、靈活性高、研發(fā)周期短等特點(diǎn)。 1 硬件接口: 硬件的接口如上圖所示,主要包括發(fā)送與接收模塊。 發(fā)送模塊包括8b/10b編碼器,并串轉(zhuǎn)換器,鎖相環(huán)(PLL

2019-05-29 17:52:03

`京微雅格 (Capital-Micro) - CME-HR(黃河)開發(fā)板資料感謝京微雅格提供大賽用開發(fā)板數(shù)據(jù)下載亮點(diǎn)低功耗,高性價(jià)比FPGA40nm UMC低功耗工藝768到15360個(gè)4輸入查找

2015-05-04 14:45:36

`CME-M7(華山)開發(fā)板資料感謝京微雅格提供大賽用開發(fā)板數(shù)據(jù)下載CME-M7(華山)集成了主流的ARM Cortex-M3內(nèi)核和高性能FPGA。其中FPGA部分采用高達(dá)12K容量的新型LP

2015-05-04 14:38:02

京微雅格(廠商資料):AstroII-EVB-F1K(A)-L144開發(fā)板用戶指南 有需要的可以下載

2012-08-01 20:24:47

京微雅格(廠商資料):AstroII數(shù)據(jù)手冊(cè)1.0有需要的可以下載

2012-08-01 20:48:25

小弟最近在調(diào)用Aurora 8b/10b IP模塊時(shí),在用modelsim功能仿真時(shí),一切正常。 但是直接使用了例化后的example,并將Tx和Rx形成了回路下到FPGA板子上

2015-03-09 10:58:03

什么是8b/10b編碼,為什么JESD204B接口需使用這種編碼?怎么消除影響JESD204B鏈路傳輸?shù)囊蛩兀縅ESD204B中的確定延遲到底是什么? 它是否就是轉(zhuǎn)換器的總延遲?JESD204B如何使用結(jié)束位?結(jié)束位存在的意義是什么?如何計(jì)算轉(zhuǎn)換器的通道速率?什么是應(yīng)用層,它能做什么?

2021-04-13 06:39:06

問:什么是8b/10b編碼,為什么JESD204B接口需使用這種編碼?

答:無法確保差分通道上的直流平衡信號(hào)不受隨機(jī)非編碼串行數(shù)據(jù)干擾,因?yàn)楹苡锌赡軙?huì)傳輸大量相反的1或0數(shù)據(jù)。通過串行鏈路傳輸

2024-01-03 06:35:04

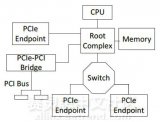

中,都要保證每個(gè)Dword的正確性和完整性,否則將導(dǎo)致數(shù)據(jù)出錯(cuò)或原語流失。另外,目前高速數(shù)據(jù)傳輸接口或總線常用8B/10B編碼來編碼,其根本目的是實(shí)現(xiàn)直流平衡(DC Balance)。當(dāng)高速串行流

2018-12-11 11:04:22

【STM32L15xx6/8/B-】本文檔是關(guān)于ARM? Cortex?-M3內(nèi)核的超低功耗單片機(jī)STM32L151x6/8/B-A,STM32L152x6/8/B-A的數(shù)據(jù)手冊(cè)。特征:超低功率平臺(tái)

2022-11-28 08:06:54

大家好,我正在使用帶有8B / 10B的Spartan-6 GTP傳輸32位數(shù)據(jù),并使用光纖外部FPGA,當(dāng)我將代碼下載到芯片時(shí),它是正確的,但在IPull輸出光纖后立即插入電源(我稱之為熱插拔

2020-03-18 10:02:58

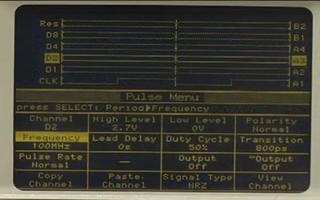

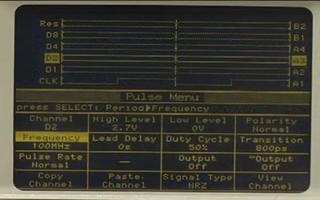

通道上最大記錄長度為 32 M樣點(diǎn)- 在所有四條通道上實(shí)時(shí)取樣速率為 20 GS/s- 高達(dá) 3.125 Gb/s的串行碼流觸發(fā)功能,支持 8b/10b 協(xié)議觸發(fā) - 串行數(shù)據(jù)分析和一致性測(cè)試,提供 Windows XP操作系統(tǒng)的內(nèi)置聯(lián)網(wǎng)- 速率可達(dá) 6.25 Gb/s 及更高 OpenChoice?軟件

2022-03-09 14:51:57

數(shù)進(jìn)行權(quán)衡。支持 8b/10b 和 64b/66b 數(shù)據(jù)編碼方案。64b/66b 編碼支持前向糾錯(cuò) (FEC),可改進(jìn)誤碼率。此接口向后兼容 JESD204B 接收器。

無噪聲孔徑延遲調(diào)節(jié)

2024-01-31 15:22:55

,技術(shù)支持,價(jià)格最具優(yōu)勢(shì)!Y10-2VK2C23A/B概述:VK2C23A/B是一個(gè)點(diǎn)陣式存儲(chǔ)映射的LCD驅(qū)動(dòng)器,可支持最大224點(diǎn)(56SEGx4COM)或者最大416點(diǎn)(52SEGx8

2022-02-21 09:57:43

嗨,我試圖在Zynq 7015中使用GTX來制作一個(gè)簡單的傳輸僅使用8B10B編碼的serdes。我有Vivado 2014.4,我在PicoZed SOM上測(cè)試。我有一個(gè)200Mhz LVDS信號(hào)

2020-07-31 09:10:30

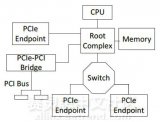

PCI Express increases data transport efficiency and data quality. It uses an 8b/10b encoding methodology to embed the clock signal ...

2019-09-23 11:01:40

JC-16接口技術(shù)委員會(huì)建立,目標(biāo)是提供速率更高的串行接口、提升帶寬并降低高速數(shù)據(jù)轉(zhuǎn)換器和其他器件之間的數(shù)字輸入和輸出通道數(shù)。該標(biāo)準(zhǔn)的基礎(chǔ)是IBM開發(fā)的8b/10b編碼技術(shù),它無需幀時(shí)鐘和數(shù)據(jù)時(shí)鐘,支持以

2019-05-29 05:00:04

CAP系統(tǒng)是京微雅格將純硬件的MCU處理器與可編程邏輯器件的有機(jī)結(jié)合,即能提供高性能處理器(增 強(qiáng)型8051)又提供了靈活的邏輯資源,客戶可以在一個(gè)平臺(tái)上完成FPGA與MCU的結(jié)合,能夠節(jié)省系統(tǒng)電路板面積并減少系統(tǒng)的芯片數(shù)量。

2019-09-17 06:38:00

世界上量產(chǎn)FPGA的公司有來自美國硅谷的四大巨頭Xilinx、Altera、Lattice、Microsemi,以及唯一一家非美國FPGA公司——京微雅格。作為FPGA俱樂部的新秀,京微雅格的國產(chǎn)FPGA發(fā)展之途雖然充滿挑戰(zhàn),但前途似錦。

2019-10-11 06:44:41

。此外,可通過8B/10B解碼錯(cuò)誤狀態(tài)實(shí)時(shí)確定SERDES鏈路質(zhì)量。偽隨機(jī)位序列(PRBS)提供了一個(gè)測(cè)量高速鏈路中信號(hào)質(zhì)量和抖動(dòng)容差的有用資源。大部分FPGA 中的SERDES收發(fā)器都內(nèi)置了PRBS

2018-10-16 06:02:44

數(shù)據(jù)的8b/10b編解碼、高速串并轉(zhuǎn)換,以及CPRI協(xié)議的成幀、解幀、同步、傳輸數(shù)據(jù)復(fù)/分解等操作。FPGA的控制作用主要是針對(duì)光接口模塊和PHY模塊。對(duì)于光接口模塊,由于XFP提供一個(gè)兩線的串行接口

2019-06-04 05:00:18

Gb/s傳輸給FPGA。在該數(shù)據(jù)流傳輸中,由于FPGA對(duì)數(shù)據(jù)進(jìn)行8b/10b編解碼,因此有效碼率是10 Gb/s,能夠滿足本文的設(shè)計(jì)要求,可以實(shí)現(xiàn)10G以太網(wǎng)的數(shù)據(jù)流傳輸。時(shí)鐘模塊:時(shí)鐘模塊內(nèi)采用

2019-05-31 05:00:06

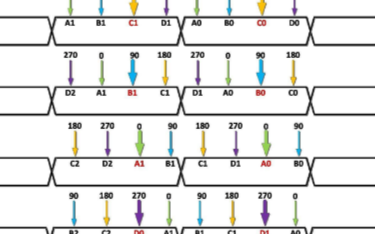

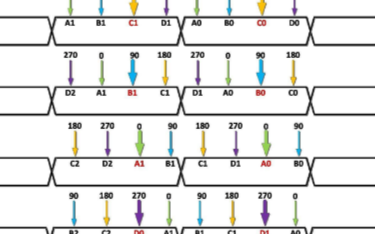

的協(xié)議會(huì)定義特殊的碼型(常見的碼型如8B/10B編碼中的K28.5)用于字對(duì)齊處理。另一些帶源同步時(shí)鐘的LVDS接口,通常會(huì)利用低頻的源同步時(shí)鐘來攜帶字對(duì)齊信息,用于接收端的正確恢復(fù)。FPGA對(duì)上述兩種

2019-07-29 07:03:50

高速LVDS數(shù)據(jù)傳輸方案和協(xié)議基于FPGA的高速LVDS數(shù)據(jù)傳輸本人在北京工作6年,從事FPGA外圍接口設(shè)計(jì),非常熟悉高速LVDS數(shù)據(jù)傳輸,8B/10B編碼等,設(shè)計(jì)調(diào)試了多個(gè)FPGA與FPGA以及

2014-03-01 18:47:47

串行接口常用于芯片至芯片和電路板至電路板之間的數(shù)據(jù)傳輸。隨著系統(tǒng)帶寬不斷增加至多吉比特范圍,并行接口已經(jīng)被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨(dú)立的ASSP 或ASIC 器件。

2019-10-14 06:39:42

芯片設(shè)計(jì)解決方案供應(yīng)公司微捷碼(Magma)設(shè)計(jì)自動(dòng)化有限公司近日宣布,已和專為消費(fèi)性應(yīng)用提供超低功耗65納米FPGA(現(xiàn)場(chǎng)可編程門陣列)技術(shù)的先驅(qū)者SiliconBlue科技公司正式簽定技術(shù)合作

2019-07-26 07:29:40

你好,我正在嘗試使用Aurora 8B / 10B建立僅傳輸(流媒體)。現(xiàn)在使用Vivado 2014.4進(jìn)行模擬階段。我知道GTXE2_COMMON原語需要在設(shè)計(jì)中使用以包含一個(gè)QUAD PLL

2020-08-14 08:49:13

如何利用Freeze技術(shù)的FPGA實(shí)現(xiàn)低功耗設(shè)計(jì)?

2021-04-29 06:27:52

Serdes向?qū)е惺褂昧瞬徽_的設(shè)置嗎?我在Comma Alignment上附上了Wizard頁面的屏幕截圖。作為附件。注意:我們?cè)?b class="flag-6" style="color: red">Serdes之外做8b / 10b,所以我們?cè)跊]有解碼的情況下查看原始數(shù)據(jù)。查克王爾德NEOTECH

2020-08-21 11:05:45

的模數(shù)轉(zhuǎn)換器(ADC)和數(shù)模轉(zhuǎn)換器(DAC)支持最新的JESD204B串行接口標(biāo)準(zhǔn),出現(xiàn)了FPGA與這些模擬產(chǎn)品的最佳接口方式問題。FPGA一直支持千兆串行/解串(SERDES)收發(fā)器。然而在過去,大多數(shù)ADC

2021-04-06 09:46:23

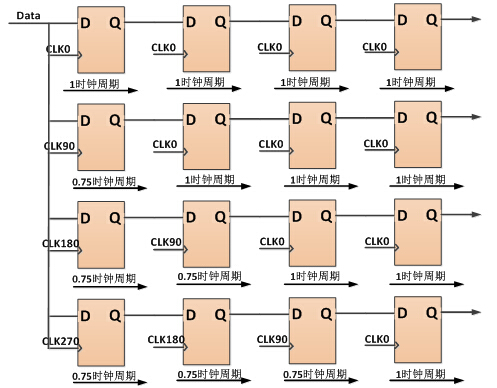

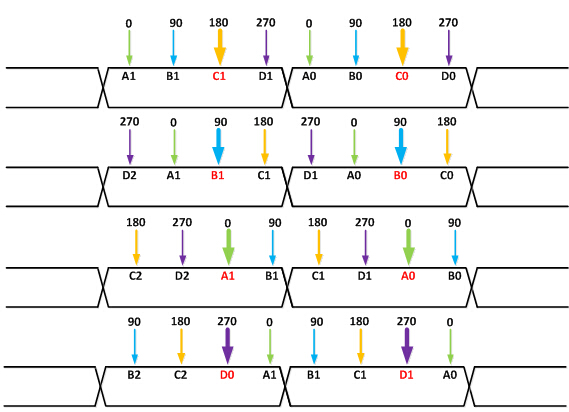

本方案是以CME最新的低功耗系列FPGA的HR03為平臺(tái),實(shí)現(xiàn)8/10b的SerDes接口,包括SERDES收發(fā)單元,通過完全數(shù)字化的方法實(shí)現(xiàn)SERDES的CDR(Clock Data

2019-10-21 07:09:44

and other devices. The standard builds on 8b/10b encoding technology developed by IBM

2021-11-03 07:00:00

大家好,我使用的是Vivado 2016.4和Virtex 7 XC7VX485T FPGA。我需要知道是否有一個(gè)選項(xiàng)可以禁用Aurora IP Core 8B / 10B中的時(shí)鐘補(bǔ)償功能。我可以看到IP核心文件,但它們都是只讀的。謝謝,馬諾

2020-08-18 09:43:40

以及所針對(duì)的最終應(yīng)用。并行數(shù)據(jù)通常將編碼為標(biāo)準(zhǔn)編碼方案(例如 8B/10B 編碼),因而適用于串行化。原始應(yīng)用數(shù)據(jù)可能包含病態(tài)模式、長期運(yùn)行的 1 和 0,這會(huì)使串行解串器難以捕捉位跳變。對(duì)數(shù)據(jù)進(jìn)行

2018-09-13 09:54:18

親愛的先生,我正在使用Vivado 2015.4。我想在收發(fā)器向?qū)е惺褂猛ǖ澜壎ǎ獵B在手冊(cè)中是灰色的。另外,我找不到在收發(fā)器向?qū)е袉⒂?b class="flag-6" style="color: red">8b / 10b編碼器的方法。如果你能給我一些建議,我將不勝感激。問候,泰迪王

2020-08-04 08:32:57

問:什么是8b/10b編碼,為什么JESD204B接口需使用這種編碼?答:無法確保差分通道上的直流平衡信號(hào)不受隨機(jī)非編碼串行數(shù)據(jù)干擾,因?yàn)楹苡锌赡軙?huì)傳輸大量相反的1或0數(shù)據(jù)。通過串行鏈路傳輸?shù)碾S機(jī)數(shù)

2018-12-10 09:44:59

我想支持下國產(chǎn)fpga,我想問一下國產(chǎn)的那個(gè)京微雅格的fpga怎么樣,這個(gè)片子的資料怎么看不到啊,求高手

2016-08-02 15:26:48

小白提問:泰格7704b自檢故障512具體什么故障?

2021-02-24 09:54:22

作者:黃剛上文說完了8B/10B之后,我們?cè)賮碚f說貌似更復(fù)雜的64B/66B編碼。很多人可能在想,8B/10B編碼主要作用的優(yōu)化直流平衡,從8bit中插2個(gè)bit進(jìn)去,這樣的話最終效果能夠使長0或者

2019-07-19 07:35:57

大家好,Vivado版本:15.2FPGA:Artix 7 xc7a50tAurora 8b / 10b IP v11.0(Rev 1) - 使用VHDL創(chuàng)建車道:1我最近一直面臨著Aurora

2020-08-06 09:34:12

端口 - FPGA RX接口端口-----------------輸出[15:0] gt0_rxdata_out,// ------- ---------接收端口 - RX 8B / 10B解碼器端口

2020-08-10 10:11:17

關(guān)于ARM? Cortex?-M3超低功耗單片機(jī)STM32L15xx6/8/B的數(shù)據(jù)手冊(cè), 介紹了它的主要外設(shè)資源和電特性參數(shù)。特征:超低功率平臺(tái)1.65V至3.6 V電源-40°C至85°C

2022-11-28 07:01:54

后,經(jīng)過8B/10B編碼,并/串變換等處理步驟,以串行差分信號(hào)的形式輸出到光電轉(zhuǎn)換子模塊。為了保證PL4接口達(dá)到十路1Gbps的速率,PM3388的參考時(shí)鐘引腳接160MHz時(shí)鐘晶振,輸入輸出接口

2019-04-29 07:00:07

輔助數(shù)據(jù)。ISL34340中的DC平衡的8b/10b代碼可以實(shí)現(xiàn)交流耦合,同時(shí)具有對(duì)地電位偏移的免疫性。對(duì)共模傳輸效果的改進(jìn)有助于在更長距離的電纜上實(shí)現(xiàn)可靠的信號(hào)傳輸。ISL34340集成的發(fā)射器預(yù)

2019-05-08 07:00:01

(旁路)。 T M D S信號(hào)傳輸使用對(duì)本協(xié)議唯一的四個(gè)對(duì)齊的字符(不同于8B/10B方式)。串行器與SERDES的CDR傳遞10位的原始數(shù)據(jù),FPGA進(jìn)行字節(jié)對(duì)齊。 DVI/HDMI鏈路連接能以多個(gè)

2019-06-06 05:00:34

一、高速

接口8B/

10B的作用? 在數(shù)字通信中編碼和加擾的作用是不同的。編碼通常有信源編碼和信道編碼,

8b/

10b是信道編碼,信道編碼的作用是通過增加冗余(此外冗余為2

b)以提高數(shù)據(jù)傳輸?shù)目煽啃浴<?/div>

2022-01-18 06:16:43

作者:黃剛前面文章說過,在高速鏈路中導(dǎo)致接收端眼圖閉合的原因,很大部分并不是由于高頻的損耗太大了,而是由于高低頻的損耗差異過大,導(dǎo)致碼間干擾嚴(yán)重,因此不能張開眼睛。針對(duì)這種情況,前面有講過可以通過CTLE和FFE(包括DFE)均衡進(jìn)行解決,原理無非就是衰減低頻幅度或者抬高高頻幅度,從而達(dá)到在接收端高低頻均衡的效果。同時(shí)我們?cè)谇拔倪€埋了個(gè)伏筆:

2019-07-19 07:45:29

采用Xilinx 公司Virtex- II Pro 系列FPGA 內(nèi)嵌得SERDES 模塊———RocketIO 作為高速串行協(xié)議的物理層, 利用其8B/10B的編解碼和串化、解串功能, 實(shí)現(xiàn)了兩板間基于數(shù)據(jù)幀的簡單高速串行傳輸

2010-09-22 08:44:28 28

28 具有低功耗意識(shí)的FPGA設(shè)計(jì)方法

ILGOO系列低功耗FPGA產(chǎn)品

Actel公司的ILGOO系列器件是低功耗FPGA產(chǎn)品,是在便攜式產(chǎn)品設(shè)計(jì)中替代ASIC和CPLD的最

2009-11-26 09:41:19 676

676

摘要:為提高8B/10B編解碼的工作速度和簡化邏輯方法,提出一種基于FPGA的8B/10B編解碼系統(tǒng)設(shè)計(jì)方案。與現(xiàn)有的8B/10B編解碼方案相比,該方案是一種利用FPGA實(shí)現(xiàn)8B/lOB編解碼的模塊方

2011-05-26 11:08:20 3364

3364

白皮書 :采用低成本FPGA實(shí)現(xiàn)高效的低功耗PCIe接口 了解一個(gè)基于DDR3存儲(chǔ)器控制器的真實(shí)PCI Express (PCIe) Gen1x4參考設(shè)計(jì)演示高效的Cyclone V FPGA怎樣降低系統(tǒng)總成本,同時(shí)實(shí)現(xiàn)性能和功耗

2013-02-26 10:04:25 72

72 (Pseudo Random Binary Sequence,PRBS)檢測(cè)方法對(duì)該編碼器進(jìn)行驗(yàn)證。FPGA綜合結(jié)果表明,該設(shè)計(jì)占用的LUT為32,占用較少的邏輯資源。采用PIU3S-7測(cè)試結(jié)果表明,該8B/10B編碼電路誤碼率為O,表明了該8B/10B編碼器傳輸信息的可靠性。

2017-11-06 17:04:21 7

7 針對(duì)較為常用的Aurora 8B/10B和PCI Express 2.0,Serial RapidIO 2.0三種協(xié)議進(jìn)行了測(cè)試及對(duì)比分析。首先搭建了基于Virtex-6 FPGA的高速串行協(xié)議測(cè)試

2017-11-18 01:00:06 11255

11255

Microsemi公司的SmartFusion2 SoC FPGA是低功耗FPGA器件,集成了第四代基于閃存FPGA架構(gòu),166MHz ARM Cortex-M3處理器和高性能通信接口,是業(yè)界最低功耗

2018-05-14 14:20:00 6839

6839

看看LatticeECP3 FPGA的功耗是多么的低,無論是在實(shí)驗(yàn)室中測(cè)量,還是利用萊迪思的功耗計(jì)算器軟件計(jì)算。 LatticeECP3是業(yè)界最低功耗的配備SERDES的FPGA。

2018-06-15 13:36:00 4990

4990

本方案是以CME最新的低功耗系列FPGA的HR03為平臺(tái),實(shí)現(xiàn)8/10b的SerDes接口,包括SERDES收發(fā)單元,通過完全數(shù)字化的方法實(shí)現(xiàn)SERDES的CDR(Clock Data

2019-05-24 15:33:25 4073

4073

8b/10b編碼器用于將從上層協(xié)議芯片發(fā)送過來的字節(jié)信號(hào)映射成直流平衡的 10 位8b/10b 編碼,并串轉(zhuǎn)換用于將 10 位編碼結(jié)果串行化,并串轉(zhuǎn)換所需的高速、低抖動(dòng)時(shí)鐘由鎖相環(huán)提供,發(fā)送器用于將 CMOS 電平的高速串行碼流轉(zhuǎn)換成抗噪聲能力較強(qiáng)的差分信號(hào),經(jīng)背板連接或光纖信道發(fā)送到接收機(jī)。

2019-05-27 14:31:09 4988

4988

串行接口常用于芯片至芯片和電路板至電路板之間的數(shù)據(jù)傳輸。隨著系統(tǒng)帶寬不斷增加至多吉比特范圍,并行接口已經(jīng)被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。

2020-05-18 10:51:18 2964

2964

總線而成為高速接口設(shè)計(jì)的主流。 如今,隨著SerDes接口的廣泛應(yīng)用,許多高端的FPGA都內(nèi)嵌有SerDes接口硬核。在FPGA中內(nèi)嵌的SERDES的硬核,可以大大地?cái)U(kuò)張FPGA的數(shù)據(jù)吞吐量,節(jié)約功耗,提高性能,使FPGA在高速系統(tǒng)設(shè)計(jì)中扮演著日益重要的角色。 國產(chǎn)

2020-07-28 12:05:16 1128

1128 功耗是各大設(shè)計(jì)不可繞過的話題,在各大設(shè)計(jì)中,我們應(yīng)當(dāng)追求低功耗。為增進(jìn)大家對(duì)低功耗的認(rèn)識(shí),本文將對(duì)FPGA低功耗設(shè)計(jì)予以介紹。如果你對(duì)FPGA低功耗相關(guān)內(nèi)容具有興趣,不妨繼續(xù)往下閱讀哦。 FPGA

2020-10-28 15:02:13 2498

2498 功耗是各大設(shè)計(jì)不可繞過的話題,在各大設(shè)計(jì)中,我們應(yīng)當(dāng)追求低功耗。為增進(jìn)大家對(duì)低功耗的認(rèn)識(shí),本文將對(duì)FPGA低功耗設(shè)計(jì)予以介紹。如果你對(duì)FPGA低功耗相關(guān)內(nèi)容具有興趣,不妨繼續(xù)往下閱讀哦。 FPGA

2020-10-26 18:51:16 2583

2583 因?yàn)閿z像頭輸出的LVDS信號(hào)速率會(huì)達(dá)到600Mbps,我們將不能夠通過FPGA的I/O接口直接去讀取這么高速率的信號(hào)。因此,需要使用Xilinx FPGA內(nèi)的SerDes去實(shí)現(xiàn)高速數(shù)據(jù)的串并轉(zhuǎn)換。

2020-12-30 17:24:00 39

39 我在2015年底到2016年初的時(shí)候,使用7 Series FPGA Transceivers完成了TS流數(shù)據(jù)的傳輸,當(dāng)時(shí)使用的傳輸速度為3.125G,SerDes選取的是8b/10b編碼方式

2020-12-30 17:24:00 31

31 功耗是我們關(guān)注的設(shè)計(jì)焦點(diǎn)之一,優(yōu)秀的器件設(shè)計(jì)往往具備低功耗特點(diǎn)。在前兩篇文章中,小編對(duì)基于Freez技術(shù)的低功耗設(shè)計(jì)以及FPGA低功耗設(shè)計(jì)有所介紹。為增進(jìn)大家對(duì)低功耗的了解,以及方便大家更好的實(shí)現(xiàn)低功耗設(shè)計(jì),本文將對(duì)FPGA具備的功耗加以詳細(xì)闡述。如果你對(duì)低功耗具有興趣,不妨繼續(xù)往下閱讀哦。

2021-02-14 17:50:00 6072

6072 ? 論序 8b/10b編碼/解碼是高速串行通信,如PCle SATA(串行ATA),以及Fiber Channel中常用的編解碼方式。在發(fā)送端,編碼電路將串行輸入的8比特一組的數(shù)據(jù)轉(zhuǎn)變成10比特一組

2021-09-26 09:56:22 7402

7402

8b/10b最常見的是應(yīng)用于光纖通訊和LVDS信號(hào)的。由于光模塊光模塊只能發(fā)送亮或者不亮,也就是0或者1這兩種狀態(tài)這種單極性碼,那么這會(huì)存在一個(gè)問題,如果傳輸中出現(xiàn)較長的連0或者連1(例如

2022-11-12 15:47:27 7711

7711 與現(xiàn)有的中端FPGA相比,得益于專為低功耗設(shè)計(jì)的可編程結(jié)構(gòu)、功耗優(yōu)化的嵌入式存儲(chǔ)器和DSP、低功耗高性能SERDES與I/O設(shè)計(jì)、內(nèi)置協(xié)議邏輯等全方位優(yōu)化措施,Avant系列產(chǎn)品的功耗比同類競(jìng)品器件低2.5倍。

2023-01-04 11:32:11 342

342 摘要:萊迪思(Lattice )半導(dǎo)體公司在這應(yīng)用領(lǐng)域已經(jīng)推出兩款低成本帶有SERDES的 FPGA器件系列基礎(chǔ)上,日前又推出采用富士通公司先進(jìn)的低功耗工藝,目前業(yè)界首款最低功耗與價(jià)格并擁有SERDES 功能的FPGA器件――中檔的、采用65nm工藝技術(shù)的 LatticeECP3系列。

2023-10-27 16:54:24 237

237 的ASSP 或ASIC 器件。在過去幾年中已經(jīng)看到有內(nèi)置SERDES 的FPGA 器件系列,但多見于高端FPGA芯片中,而且價(jià)格昂貴。 本方案是以CME的低功耗系列FPGA的HR03為平臺(tái),實(shí)現(xiàn)

2023-07-27 16:10:01 1566

1566

已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論