的Zynq 7000, 找了一個HLS的教程,就開始了如下入門實驗,體驗高級語言綜合設計IP。Vivado HLS是Xilinx 推出的高層次綜合工具,采用C/C++語言進行FPGA設計。HLS提供了一些

2020-10-14 15:17:19 2881

2881

卡,一個4.0代PCle交換機,由您選擇的外部主機CPU管理。HL-205符合oCP OAM(開放式計算項目加速器模塊)規范。Eachcard包含Gaudi HL-2000處理器,該處理器集成

2023-08-04 06:06:14

利用所有可能的數據通信方式-沒有功能概述,也沒有對用戶代碼進行優化轉換-支持代碼報告得太晚了-在某些情況下,工具的高效實施是不可能的,例如當必須將太多的加速器映射到硬件部分時。HLS工具無法預先檢測

2021-07-10 08:00:00

不同類型的DMAHigh performance w/DMA幾種DMA的總結ZYNQ中不同應用的DMA幾個常用的 AXI 接口 IP 的功能(上面已經提到):AXI-DMA:實現從 PS 內存

2022-03-31 11:39:10

壇友們,誰用過Zynq7000的處理,交流一些問題!

2017-08-14 20:53:12

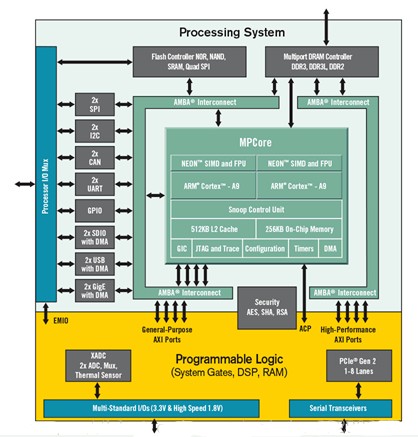

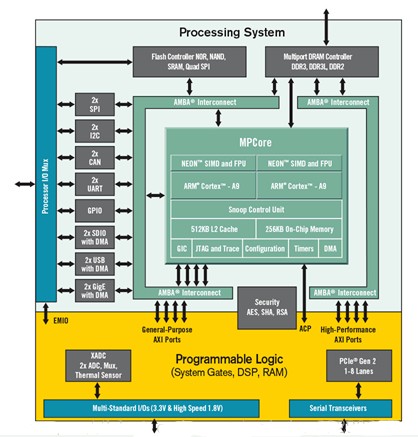

關于Zynq的理論部分,文大部分截圖摘抄自《zynqbook》ZYNQ架構雙核ARM Cortex-A9 處理器:ARM Cortex-A9 是一個應用級的處理器,能運行完整的像Linux 這樣

2021-07-23 10:11:25

目前正在做關于圖像處理--測量疲勞裂紋長度的畢設,由于裂紋長度太細小,我先編了一個讀取圖像-中值濾波-圖像增強-提取邊緣,發現除了邊緣被測器件表面還有大量的噪點,如果采用設置閾值,有些邊緣會和噪點一起被除去,定位就搞不定了 大神們有沒有什么好的建議?

2014-04-26 17:45:32

各位大蝦好,我現在正在做關于fpga的課題。想問問大家用fpga處圖像,圖片以怎么的方式輸入fpga再進行處理。

2013-04-12 11:00:17

大家好,我要做一個基于labview的圖像處理的一個畢業設計,需要實現圖像求反、二值化、灰度處理等功能。輸入圖像的功能要怎么實現呢。我現在對于整體的設計沒有大概的思路。請求大神幫忙提供下思路。謝謝了。

2017-02-04 15:25:50

哪位大神知道如何實時的采集圖像并進行圖像處理(比如我用grab.vi實時采集圖像,在這個過程中我能對實時采集到的圖像進行處理如濾波,邊緣檢測等),求大神告知

2017-06-06 21:10:40

序:原先最初是沒打算寫電機選型總結的,而是準備寫一些關于數字信號處理相關的東西,但是我的一個朋友提醒了我。他說,現在網上關于數字信號處理的東西寫的太多了,特別是基礎的知識都寫爛了,你再寫也沒人看

2021-08-31 07:00:13

算法加速圖像處理目標跟蹤 產品規格芯片型號ZYNQ 7010+ADAPIVE DSP(16)ARM核CORTEX-A7 DUAL 800MHZDRAM1GBYTE(4GB MAX)EMMC1G外圍

2017-06-08 10:33:07

各位大神有沒有圖像處理中關于圖像的邊緣檢測方面的例子。就是測量圖像邊緣的圓、圓弧、長度、夾角之類的。還有就是有沒有曲線擬合方面的資料。

2014-03-18 09:45:57

輕松實現OpenCV C++視頻處理設計到RTL代碼的轉換,輸出硬件加速器或者直接在FPGA上實現實時視頻處理功能。同時,Zynq All-programmable SOC是實現嵌入式計算機視覺

2021-07-08 08:30:00

Vivado HLS視頻庫加速Zynq-7000 All Programmable SoC OpenCV應用加入賽靈思免費在線研討會,了解如何在Zynq?-7000 All Programmable

2013-12-30 16:09:34

今天給大俠帶來簡談Xilinx Zynq-7000嵌入式系統設計與實現,話不多說,上貨。Xilinx的ZYNQ系列FPGA是二種看上去對立面的思想的融合,ARM處理器的串行執行+FPGA的并行執行

2021-11-09 06:43:27

vivado可以正常使用,但是HLS總是出現圖片中的錯誤。請問該如何解決?謝謝!

2020-08-12 01:36:19

利用所有可能的數據通信方式-沒有功能概述,也沒有對用戶代碼進行優化轉換-支持代碼報告得太晚了-在某些情況下,工具的高效實施是不可能的,例如當必須將太多的加速器映射到硬件部分時。HLS工具無法預先檢測

2021-07-06 08:00:00

三、硬件加速之—使用PL加速FFT運算(Vivado)

前四期測評計劃:

一、開箱報告,KV260通過網線共享PC網絡

二、Zynq超強輔助-PYNQ配置,并使用XVC(Xilinx Virtual

2023-10-02 22:03:13

四、硬件加速之—使用PL加速矩陣乘法運算(Vitis HLS)

前四期測評計劃:

一、開箱報告,KV260通過網線共享PC網絡

二、Zynq超強輔助-PYNQ配置,并使用XVC(Xilinx

2023-10-13 20:11:51

項目名稱:基于ZYNQ的圖像算法加速試用計劃:本人在FPGA設計有三年多的工作經驗,對zynq,做過petalinux移植、非petalinux的Ubuntu移植、基于lwip的數據處理系統、ps

2019-09-18 14:17:42

庫函數,當中的HLS OpenCV library可應用于Zynq系列中ARM處理器的任務中。HLS OpenCV Library是可綜合的圖像處理庫,本算法中的OpenCV功能函數被HLS OpenCV

2015-07-07 20:41:34

Detection模塊就設計的硬件加速模塊,旨在利用FPGA的并行處理能力加速圖像的處理效率。PL處理完的數據,將以同樣的路徑返回到PS部分,處理結束的消息可以通過中斷方式進行告知PS部分,以同步PS與PL的工作。本系統的組成架構如下

2015-07-07 20:41:04

的“HLS視頻庫”中的函數,來進行基于HLS的視頻圖像處理。對于上面列出的各個庫,我們同樣會在后續章節中用到時候再進行介紹。

2020-10-10 16:44:42

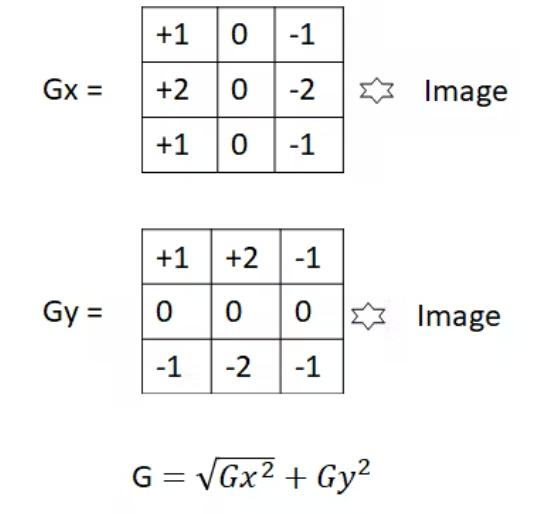

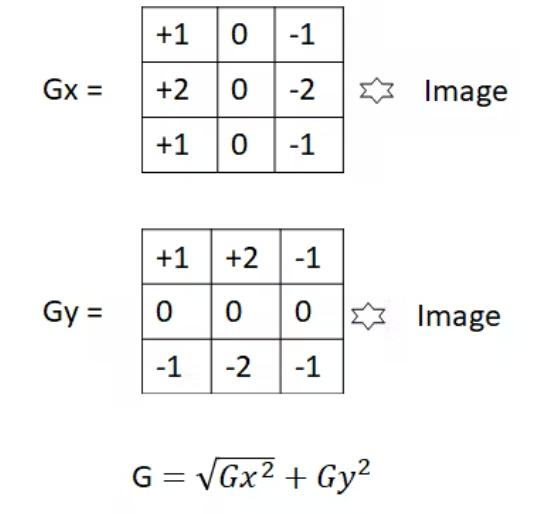

原子公眾號,獲取最新資料第七章OV5640攝像頭Sobel邊緣檢測邊緣檢測是圖像處理和計算機視覺中的基本問題,邊緣檢測的目的是標識數字圖像中亮度變化明顯的點。在本章我們將通過OV5640攝像頭Sobel

2020-10-13 17:05:04

就是加速開發的周期。加速策略可以從兩個方面考慮:(一)設計的重用和(二)抽象層次的提升。Xilinx Vivado開發套件中的IP集成功能可以實現設計的重用,而Vivado HLS工具則能夠實現對高層次

2020-10-10 16:48:25

“Start of frame”是幀傳輸開始信號。它在一幀圖像像素傳輸開始的時候拉高一個時鐘周期。5.2實驗任務本節的實驗任務是使用Vivado HLS設計彩條顯示的IP核,并在Vivado中

2020-10-13 16:56:47

、醫學成像等方面應用越來越廣。本章節我們將使用Vivado HLS生成一個圖像彩條疊加的IP核,來進行基于OV5640的視頻圖像疊加實驗。本章包括以下幾個部分:88.1簡介8.2實驗任務8.3HLS

2020-10-13 17:06:26

實現的圖像處理模塊已經被綜合成FPGA中的硬件模塊,可以實時地處理FPGA中的視頻流。Vivado HLS所綜合出來的視頻處理模塊同樣可以部署在ZYNQ器件的PL端,其常用的架構如下圖所示:圖

2020-10-13 16:58:56

是灰度圖做了自適應二值化算法處理后的圖像,可以發現圖像經過自適應二值化計算出來的閾值比手動指定閾值二值化的效果更好。11.2實驗任務本節的實驗任務是使用Vivado HLS設計OTSU自適應二值化

2020-10-14 16:04:34

簡介13.2實驗任務13.3HLS設計13.4IP驗證13.5下載驗證13.1簡介空間濾波是圖像處理領域應用非常廣泛的工具之一,它可以改善圖像質量,包括去除高頻噪聲與干擾、圖像平滑等。我們常見的空間濾波

2020-10-16 16:22:38

和抗干擾性,是直線檢測中效果最好的算法之一。霍夫變換也可用來檢測任意幾何形狀(比如圓),在圖像處理和模式識別領域得到了廣泛的應用。本章我們將在HLS中實現基于霍夫變換的直線檢測。本章包括以下幾個部分

2020-10-14 16:06:47

。由于直方圖統計在軟件中計算簡單,有助于商用硬件實現,因此已經成為一種流行的實時圖像處理工具。本章我們將在HLS中實現圖像的直方圖均衡算法。本章包括以下幾個部分:1010.1簡介10.2實驗任務

2020-10-14 16:02:01

漸滅,并且PS可以通過AXI接口來控制呼吸燈的開關和呼吸的頻率。4.3HLS設計我們在電腦中的“F:\ZYNQ\High_Level_Synthesis”目錄下新建一個名為breath_led的文件夾

2020-10-10 17:01:29

手把手教你設計人工智能芯片及系統(全階設計教程+AI芯片FPGA實現+開發板)詳情鏈接:http://url.elecfans.com/u/c422a4bd15項目名稱:基于zynq的監控視頻圖像

2019-10-30 17:03:31

` ZYNQ系列是Xilinx推出的高端嵌入式SoC,其在片上集成了ARM處理器和FPGA。ZYNQ與傳統的嵌入式CPU相比,具有強大的并行處理能力。開發人員利用FPGA強大的并行處理能力,不僅

2021-01-15 17:09:15

Vivado項目中使用以下IP塊。Xilinx I2S接收器 - 設置16位數據Xilinx I2S發送器 - 設置16位數據Zynq處理系統HLS IP核 - 一旦我們有初始音頻鏈傳遞數據,這將

2019-07-31 05:30:00

,一路用于邊緣檢測處理(Sobel算法),另一路直接回顯。利用Video Mixer IP核將圖像疊加,通過HDMI輸出原始圖像或者算法處理后的圖像。本案例支持CameraLink Base/Full

2020-09-17 09:48:13

FPGA的HLS案例開發|基于Kintex-7、Zynq-7045_7100開發板前 言本文主要介紹HLS案例的使用說明,適用開發環境:Windows 7/10 64bit、Xilinx

2021-02-19 18:36:48

你好我有Zynq 7z020板,我想訪問它的GPIO,但我找不到Zynq處理器文檔,所以我知道如何訪問Zynq GPIO?問候

2019-09-11 10:48:04

Vivado HLS 2017.4 、Xilinx SDK 2017.4。

測試板卡是基于創龍科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗處理器設計的異構多核SoC

2023-08-24 14:44:10

Vivado HLS 2017.4 、Xilinx SDK 2017.4。測試板卡是基于創龍科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗處理器設計的異構多核SoC工業

2023-01-01 23:51:35

是基于創龍科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗處理器設計的異構多核SoC工業級核心板。HLS 案例位于產品資料“4-軟件資料\Demo

2023-08-24 14:40:42

龍科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗處理器設計的異構多核SoC工業級核心板。HLS 案例位于產品資料“4-軟件資料\Demo\FPGA-HLS

2023-01-01 23:52:54

Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗處理器設計的異構多核SoC工業級核心板。4 matrix_demo 案例案例功能: 實現 32*32 浮點矩陣乘法運算功能

2023-01-01 23:50:04

龍科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗處理器設計的異構多核SoC工業級核心板。

4 matrix_demo 案例案例功能: 實現 32*32 浮點矩陣乘法

2023-08-24 14:52:17

opencv_image_filter()處理結果圖 80 原始圖像5.3 IP 核測試請參考本文檔 HLS 開發流程說明章節,完成 IP 核測試前的準備工作。HLS 工程生成的 IP 核為

2023-01-01 23:46:20

_image_filter()處理結果圖 79 opencv_image_filter()處理結果圖 80 原始圖像

5.3 IP 核測試請參考本文檔 HLS 開發流程說明章節,完成 IP 核測試前的準備工作。HLS 工程生成

2023-08-24 14:54:01

。圖 75 hls_image_filter()處理結果圖 76 opencv_image_filter()處理結果圖 77 原始圖像IP核測試請參考本文檔HLS開發流程說明章節,完成IP核測試前

2021-11-11 16:02:09

是video in to AXI4-Stream,接到DMA,而HLS生成的算法IP是AXI4-Stream in and out。我想把AXI-Stream信號輸出接到HLS輸出的IP,IP經過圖像處理后

2017-01-16 09:22:25

您好我有一個關于vivado hls的問題。RTL是否來自xivix FPGA的vivado hls onyl?我們可以在Design Compiler上使用它進行綜合嗎?謝謝

2020-04-13 09:12:32

您好Xilinx的用戶和員工,我們正在考慮購買Zynq 7000用于機器視覺任務。我們沒有編程FPGA的經驗,并希望使用Vivado HLS來指導和加速我們的工作。關于這種方法的一些問題:您對

2020-03-25 09:04:39

的請求,并驅動液晶顯示器顯示視頻圖像。本實例除了前面提到對原始圖像做DDR3緩存和顯示,還會在原始圖像緩存到DDR3之前,另外做圖像的多行緩存和平滑處理運算,獲得新的平滑后的圖像流,這個圖像流通

2019-12-12 16:47:28

、提取和跟蹤? 圖像分割與擬合? 攝像頭校準、立體化和3D處理? 機器學習:檢測、識別 圖3 OpenCV算法庫開發的運動檢測應用實例用HLS加速OPENCV函數 一旦完成了嵌入式視覺系統架構的分區

2014-04-21 15:49:33

對Xilinx可編程邏輯器件進行開發,可加速算法開發的進程,縮短產品上市時間。本次案例用到的是創龍科技的TLZ7x-EasyEVM-S開發板,它是一款基于Xilinx Zynq-7000系列XC7Z010

2021-11-11 15:54:48

為性能加速的空間圖像處理開發FPGA協處理器快速、精確的圖像數據的板上分類是現代衛星圖像處理的關鍵部分。對于地球科學和其它應用而言,空間智能有效載荷利用智能機器

2010-04-27 08:30:31 15

15 高層次綜合設計最常見的的使用就是為CPU創建一個加速器,將在CPU中執行的代碼移動到FPGA可編程邏輯去提高性能。本文展示了如何在Zynq AP SoC設計中使用HLS IP。 在Zynq器件

2017-02-07 18:08:11 3207

3207

IP那節用過)。這些模塊是連接到HP0的AXI4從端口,使得zynq7處理系統的數據通過AXI DMA IP核。硬件加速模塊是免費的運行,并不需要驅動,只要數據被CPU推送(通常簡稱為處理系統或PS)。

2017-02-07 18:13:35 3135

3135 在之前HLS的基本概念1里有提及,HLS會把c的參數映射成rtl的端口實現。本章開始總結下HLS端口綜合的一些知識。 1.HLS綜合后的rtl端口大體可以分成2類: Clock Reset端口

2017-02-08 03:29:11 544

544

7010的硬核是兩個Cortex-A9,主頻666M(233333….),硬浮點+neon協處理器,性能不是很好,因為xilinx SDK可以生成底層IP的driver,所以PS裸跑起來很簡單,通過

2017-02-08 06:42:11 1029

1029 源碼是官方的2014.4 TRD工程里的,整個工程是基于zc702板子的,但手里只有塊小zybo >_ 里面的硬件設計很有參考價值,最近想用FPGA加速surf算法,先在這分析下TRD工程

2017-02-08 10:12:11 458

458 大,我是否能夠利用Vivado HLS完成這項要求較高的運算呢? 我開始從軟件方面考慮這個轉換,我開始關注軟件界面。畢竟,HLS創建專用于處理硬件接口的硬件。幸好Vivado HLS支持創建AXI slave的想法,同時工作量較少。 我發現Vivado HLS編碼限制相當合理。它支持大多數C + +語言

2017-02-09 02:15:11 310

310 為期 ?1? 天的加速器開發流程介紹主要講解如何測量系統性能、確定什么軟件功能應該移至硬件,如何使用 ?Vivado? HLS? 工具裝配一款定制加速器,如何將該定制加速器添加至 ?Zynq SoC? 設計,以及如何測量加速性能。 了解更多 ??

2017-02-09 06:23:11 286

286 Missing Link Electronics? 基于德國弗朗霍夫海因里希赫茲研究所 ?(HHI)? 的加速技術提供 2015.02a? 修訂版 ?Zynq SoC? 評估參考設計。支持

2017-02-09 08:17:06 212

212 在特定圖像處理硬件設計中成功運用 High-Level Synthesis (HLS) 和 High-Level Verification (HLV) 數年之后, Qualcomm 認識到了 HLS

2017-09-11 11:37:38 9

9 的FPGA架構使得Xilinx Zynq-7000更加強悍,應用領域更加廣泛。下面將從以下方面介紹Zynq-7000的應用領域:汽車、通信系統、機器人、控制和儀器 、圖像和視頻處理 、醫藥、工業控制和許多其他領域。

2018-05-18 07:07:00 2584

2584 IP那節用過)。這些模塊是連接到HP0的AXI4從端口,使得zynq7處理系統的數據通過AXI DMA IP核。硬件加速模塊是免費的運行,并不需要驅動,只要數據被CPU推送(通常簡稱為處理系統或PS

2018-10-02 07:25:11 394

394 OPENCV(Open Source Computer Vision)被廣泛的使用在計算機視覺開發上。使用Vivado HLS視頻庫在zynq-7000全可編程soc上加速OPENCV 應用的開發,將大大提升我們的計算機視覺開發。

2018-11-10 10:47:49 1323

1323 了解協處理的價值,Zynq-7000加速器一致性端口,使用協處理器加速器的方法以及協處理器設計實例的概述。

2018-11-30 06:15:00 3960

3960 ADI公司在Embedded World 2015上展示了采用Zynq SDR套件的DDS HLS IP

2018-11-30 06:44:00 3026

3026 Adam Taylor討論了使用Zynq?和Zynq UltraScale +?SoC開發圖像處理應用程序時學到的一些技巧

2018-11-30 06:37:00 2023

2023 行業抓取式演示視頻重點介紹了Zynq UltraScale + MPSoC裝有專用處理引擎,面向圖像處理,實時處理和功能安全性。

2018-11-23 06:59:00 2723

2723 RTL代碼),也可以在某些場合加速設計與驗證(例如在FPGA上實現OpenCV函數),但個人還是喜歡直接從RTL入手,這樣可以更好的把握硬件結構。Xilinx官方文檔表示利用HLS進行設計可以大大加速設計進度:

2019-07-31 09:45:17 6232

6232

ZYNQ系列是Xilinx推出的高端嵌入式SoC,其在片上集成了ARM處理器和FPGA。ZYNQ與傳統的嵌入式CPU相比,具有強大的并行處理能力。開發人員利用FPGA強大的并行處理能力,不僅

2019-10-27 10:43:12 3225

3225

ThunderImage 是深維科技(DeePoly)的旗艦級產品,基于賽靈思 Alveo 加速器卡進行圖像處理加速。隨著目前高清圖片內容越來越多,大家需要對圖片的尺寸/壓縮率做進一步提升,這其中比較流行的一種格式是 Google從VP8 編碼提取出來的一套標準 WebP。

2020-04-30 15:58:42 2917

2917 近日,元腦生態伙伴深維科技與浪潮聯合發布業內首個基于FPGA的HEIF圖像處理加速方案。

2020-10-23 11:16:53 2201

2201

的是VivadoIP,用于支持Vivado IP 設計流程。后者用于Vitis應用加速流程,此時,Vitis HLS會自動推斷接口,無需在代碼里通過Pragma或Directive的方式定義Interface,最終會輸出.xo文件。 User Control Settings還有其他的一些變化,如下表

2020-11-05 17:43:16 37066

37066 這是一篇關于圖像分割損失函數的總結,具體包括:Binary Cross EntropyWeighted Cross EntropyBalanced Cross EntropyDice LossFocal lo...

2020-12-15 00:11:01 874

874 Vitis Vision庫是OpenCV和Vision功能的加速庫,可在Vitis環境中使用,這些庫的L1目錄是示例設計。為了適應各種用戶環境,從2020.1版本開始,Xilinx不再

2022-02-16 16:21:38 2016

2016

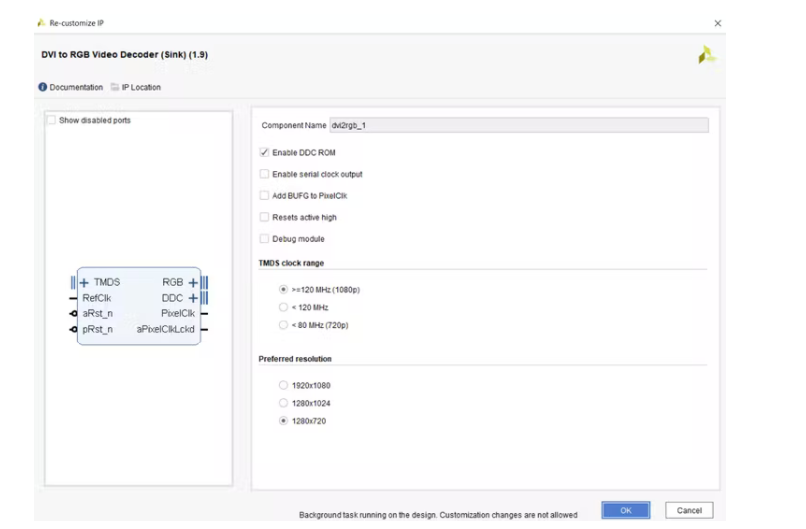

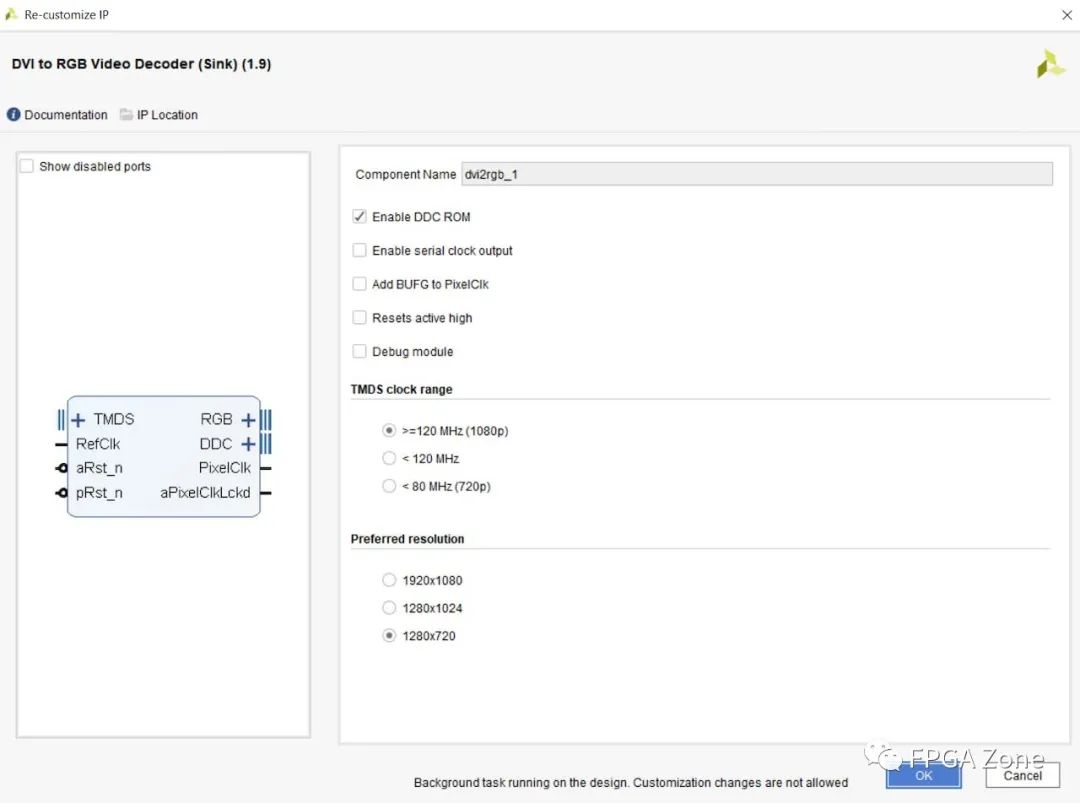

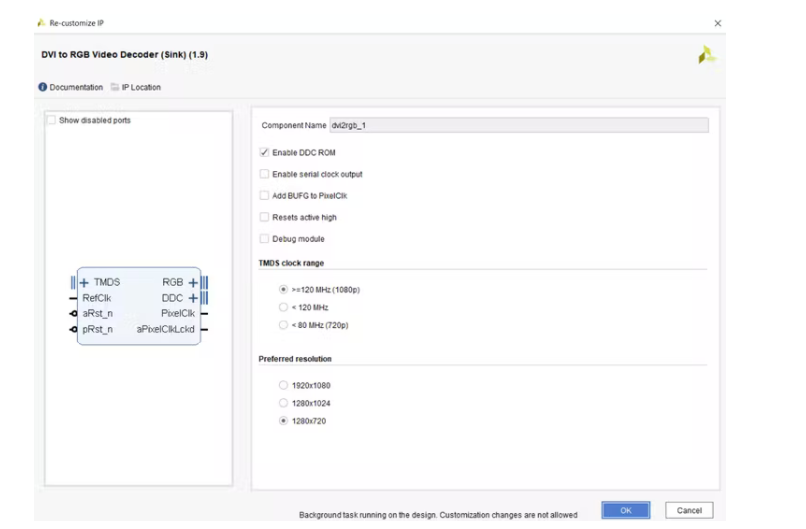

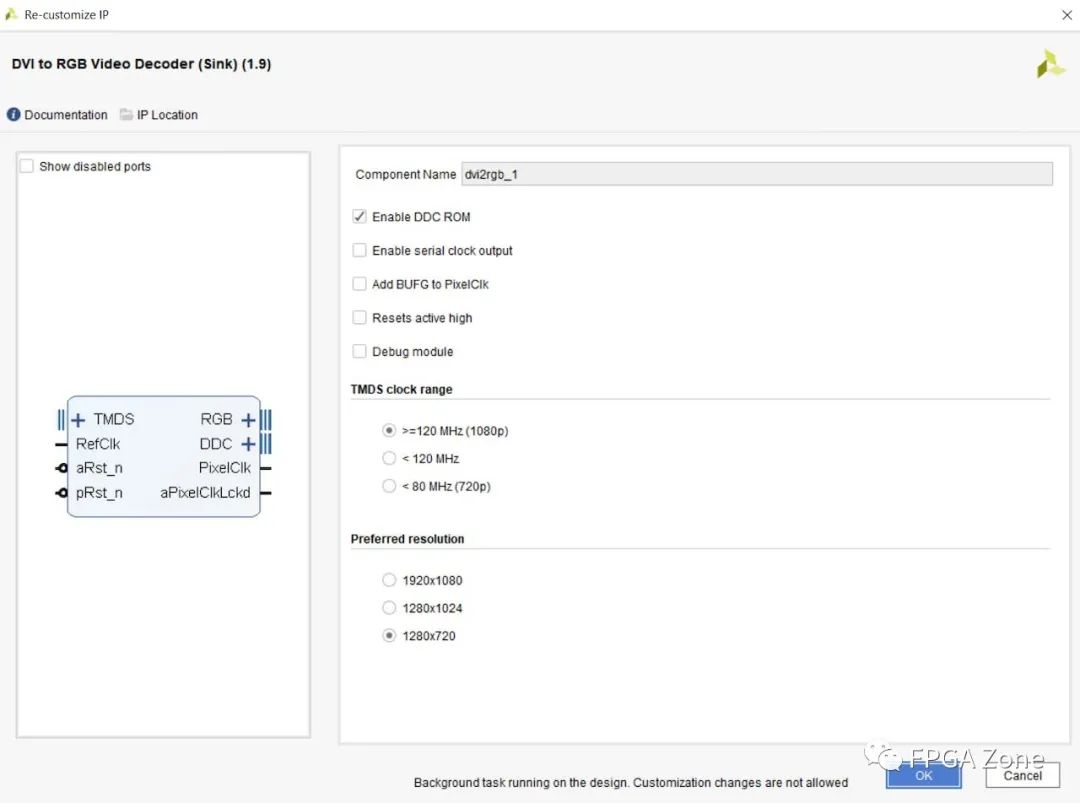

本文將介紹如何創建一個支持HDMI輸入到輸出的圖像處理平臺。這可以用作基于HLS的圖像處理演示的基礎。

2022-03-31 10:22:46 2400

2400

本方案利用 HLS 功能創建圖像處理解決方案,在可編程邏輯中實現邊緣檢測 (Sobel)。

2022-05-13 17:47:17 2597

2597

Vitis HLS 是一種高層次綜合工具,支持將 C、C++ 和 OpenCL 函數硬連線到器件邏輯互連結構和 RAM/DSP 塊上。Vitis HLS 可在Vitis 應用加速開發流程中實現硬件

2022-05-25 09:43:36 1930

1930 對于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統一將HLS集成到Vitis里了,集成之后增加了一些功能,同時將這部分開源出來了。Vitis HLS是Vitis AI重要組成部分,所以我們將重點介紹Vitis HLS。

2022-09-02 09:06:23 2857

2857 這里向大家介紹使用HLS封裝的縮放IP來實現視頻圖像縮放功能。將HLS封裝的縮放IP加入到OV5640圖像傳輸系統,驗證圖像放大和縮小功能。

2022-10-11 14:21:50 1517

1517 電子發燒友網站提供《ThunderGP:基于HLS的FPGA圖形處理框架.zip》資料免費下載

2022-10-27 16:49:59 0

0 電子發燒友網站提供《帶有PYNQ和Vitis HLS的SHA256加密加速器.zip》資料免費下載

2023-02-09 10:32:49 2

2 電子發燒友網站提供《如何使用HLS加速FPGA上的FIR濾波器.zip》資料免費下載

2023-06-14 15:28:49 1

1 最近有人問我圖像處理怎么研究,怎么入門,怎么應用,我竟一時語塞。仔細想想,自己也搞了兩年圖像方面的研究,做個兩個創新項目,發過兩篇論文,也算是有點心得,于是總結總結和大家分享,希望能對大家有所幫助

2023-06-16 10:00:29 617

617 Xilinx平臺的Vivado HLS 和 Vitis HLS 使用的 export_ip 命令會無法導出 IP

2023-07-07 14:14:57 338

338

本文介紹如何搭建一個通用的圖像處理平臺,采用HDMI接口進行輸入、輸出,可用于測試基于HLS的FPGA圖像處理項目。

2023-09-04 18:20:19 1050

1050

電子發燒友網站提供《CTAccel圖像處理(CIP)加速器.pdf》資料免費下載

2023-09-15 14:21:36 0

0 Zynq器件將arm和FPGA結合,利用了兩者各自的優勢,arm可以實現靈活的控制,而FPGA部分可以實現算法加速,這大大擴展了zynq的應用。比如深度學習加速,圖像處理等等。PL側表示FPGA的邏輯部分,PS側為arm端以及一些AXI接口控制部分,二者實際上通過AXI接口實現通信和互聯。

2023-11-09 11:28:04 1460

1460

電子發燒友App

電子發燒友App

評論