1、不熟悉FPGA的內(nèi)部結(jié)構(gòu),不了解可編程邏輯器件的基本原理。

FPGA為什么是可以編程的?恐怕很多菜鳥不知道,他們也不想知道。因?yàn)樗麄冇X得這是無(wú)關(guān)緊要的。他們潛意識(shí)的認(rèn)為可編程嘛,肯定就是像寫軟件一樣啦。軟件編程的思想根深蒂固,看到Verilog或者VHDL就像看到C語(yǔ)言或者其它軟件編程語(yǔ)言一樣。一條條的讀,一條條的分析。如果這些菜鳥們始終拒絕去了解為什么FPGA是可以編程的,不去了解FPGA的內(nèi)部結(jié)構(gòu),要想學(xué)會(huì)FPGA恐怕是天方夜譚。雖然現(xiàn)在EDA軟件已經(jīng)非常先進(jìn),像寫軟件那樣照貓畫虎也能綜合出點(diǎn)東西,但也許只有天知道EDA軟件最后綜合出來(lái)的到底是什么。也許點(diǎn)個(gè)燈,跑個(gè)馬還行。這樣就是為什么很多菜鳥學(xué)了N久以后依然是一個(gè)菜鳥的原因。那么FPGA為什么是可以“編程”的呢?首先來(lái)了解一下什么叫“程”。

啟示“程”只不過(guò)是一堆具有一定含義的01編碼而已。

編程,其實(shí)就是編寫這些01編碼。只不過(guò)我們現(xiàn)在有了很多開發(fā)工具,通常都不是直接編寫這些01編碼,而是以高級(jí)語(yǔ)言的形式來(lái)編寫,最后由開發(fā)工具轉(zhuǎn)換為這種01編碼而已。對(duì)于軟件編程而言,處理器會(huì)有一個(gè)專門的譯碼電路逐條把這些01編碼翻譯為各種控制信號(hào),然后控制其內(nèi)部的電路完成一個(gè)個(gè)的運(yùn)算或者是其它操作。所以軟件是一條一條的讀,因?yàn)檐浖牟僮魇且徊揭徊酵瓿傻摹6鳩PGA的可編程,本質(zhì)也是依靠這些01編碼實(shí)現(xiàn)其功能的改變,但不同的是FPGA之所以可以完成不同的功能,不是依靠像軟件那樣將01編碼翻譯出來(lái)再去控制一個(gè)運(yùn)算電路,F(xiàn)PGA里面沒有這些東西。

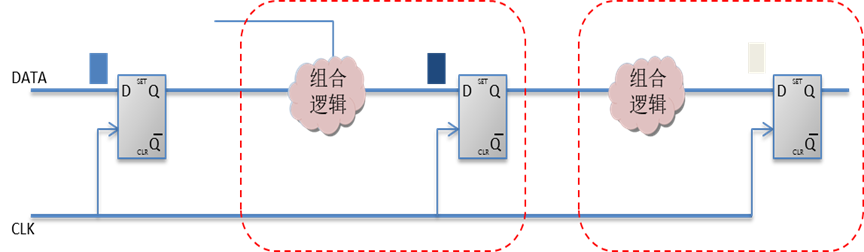

FPGA內(nèi)部主要三塊:可編程的邏輯單元、可編程的連線和可編程的IO模塊。可編程的邏輯單元是什么?其基本結(jié)構(gòu)某種存儲(chǔ)器(SRAM、FLASH等)制成的4輸入或6輸入1輸出地“真值表”加上一個(gè)D觸發(fā)器構(gòu)成。任何一個(gè)4輸入1輸出組合邏輯電路,都有一張對(duì)應(yīng)的“真值表”,同樣的如果用這么一個(gè)存儲(chǔ)器制成的4輸入1輸出地“真值表”,只需要修改其“真值表”內(nèi)部值就可以等效出任意4輸入1輸出的組合邏輯。這些“真值表”內(nèi)部值是什么?就是那些01編碼而已。如果要實(shí)現(xiàn)時(shí)序邏輯電路怎么辦?這不又D觸發(fā)器嘛,任何的時(shí)序邏輯都可以轉(zhuǎn)換為組合邏輯+D觸發(fā)器來(lái)完成。但這畢竟只實(shí)現(xiàn)了4輸入1輸出的邏輯電路而已,通常邏輯電路的規(guī)模那是相當(dāng)?shù)拇笈丁D窃趺崔k呢?這個(gè)時(shí)候就需要用到可編程連線了。在這些連線上有很多用存儲(chǔ)器控制的鏈接點(diǎn),通過(guò)改寫對(duì)應(yīng)存儲(chǔ)器的值就可以確定哪些線是連上的而哪些線是斷開的。這就可以把很多可編程邏輯單元組合起來(lái)形成大型的邏輯電路。最后就是可編程的IO,這其實(shí)是FPGA作為芯片級(jí)使用必須要注意的。任何芯片都必然有輸入引腳和輸出引腳。有可編程的IO可以任意的定義某個(gè)非專用引腳(FPGA中有專門的非用戶可使用的測(cè)試、下載用引腳)為輸入還是輸出,還可以對(duì)IO的電平標(biāo)準(zhǔn)進(jìn)行設(shè)置。總歸一句話,F(xiàn)PGA之所以可編程是因?yàn)榭梢酝ㄟ^(guò)特殊的01代碼制作成一張張“真值表”,并將這些“真值表”組合起來(lái)以實(shí)現(xiàn)大規(guī)模的邏輯功能。不了解FPGA內(nèi)部結(jié)構(gòu),就不能明白最終代碼如何變到FPGA里面去的。也就無(wú)法深入的了解如何能夠充分運(yùn)用FPGA。現(xiàn)在的FPGA,不單單是有前面講的那三塊,還有很多專用的硬件功能單元,如何利用好這些單元實(shí)現(xiàn)復(fù)雜的邏輯電路設(shè)計(jì),是從菜鳥邁向高手的路上必須要克服的障礙。而這一切,還是必須先從了解FPGA內(nèi)部邏輯及其工作原理做起。

2、錯(cuò)誤理解HDL語(yǔ)言,怎么看都看不出硬件結(jié)構(gòu)。

HDL語(yǔ)言的英語(yǔ)全稱是:Hardware Deion Language,注意這個(gè)單詞Deion,而不是Design。老外為什么要用Deion這個(gè)詞而不是Design呢?因?yàn)镠DL確實(shí)不是用用來(lái)設(shè)計(jì)硬件的,而僅僅是用來(lái)描述硬件的。

描述這個(gè)詞精確地反映了HDL語(yǔ)言的本質(zhì),HDL語(yǔ)言不過(guò)是已知硬件電路的文本表現(xiàn)形式而已,只是將以后的電路用文本的形式描述出來(lái)而已。而在編寫語(yǔ)言之前,硬件電路應(yīng)該已經(jīng)被設(shè)計(jì)出來(lái)了。語(yǔ)言只不過(guò)是將這種設(shè)計(jì)轉(zhuǎn)化為文字表達(dá)形式而已。但是很多人就不理解了,既然硬件都已經(jīng)被設(shè)計(jì)出來(lái)了,直接拿去制作部就完了,為什么還要轉(zhuǎn)化為文字表達(dá)形式再通過(guò)EDA工具這些麻煩的流程呢?其實(shí)這就是很多菜鳥沒有了解設(shè)計(jì)的抽象層次的問(wèn)題,任何設(shè)計(jì)包括什么服裝、機(jī)械、廣告設(shè)計(jì)都有一個(gè)抽象層次的問(wèn)題。就拿廣告設(shè)計(jì)來(lái)說(shuō)吧,最初的設(shè)計(jì)也許就是一個(gè)概念,設(shè)計(jì)出這個(gè)概念也是就是一個(gè)點(diǎn)子而已,離最終拍成廣告還差得很遠(yuǎn)。硬件設(shè)計(jì)也是有不同的抽象層次,每一個(gè)層次都需要設(shè)計(jì)。

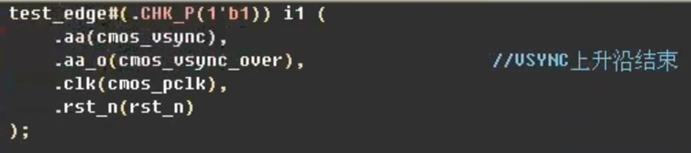

最高的抽象層次為算法級(jí)、然后依次是體系結(jié)構(gòu)級(jí)、寄存器傳輸級(jí)、門級(jí)、物理版圖級(jí)。使用HDL的好處在于我們已經(jīng)設(shè)計(jì)好了一個(gè)寄存器傳輸級(jí)的電路,那么用HDL描述以后轉(zhuǎn)化為文本的形式,剩下的向更低層次的轉(zhuǎn)換就可以讓EDA工具去做了,這就大大的降低了工作量。這就是可綜合的概念,也就是說(shuō)在對(duì)這一抽象層次上硬件單元進(jìn)行描述可以被EDA工具理解并轉(zhuǎn)化為底層的門級(jí)電路或其他結(jié)構(gòu)的電路。在FPGA設(shè)計(jì)中,就是在將這以抽象層級(jí)的意見描述成HDL語(yǔ)言,就可以通過(guò)FPGA開發(fā)軟件轉(zhuǎn)化為問(wèn)題1中所述的FPGA內(nèi)部邏輯功能實(shí)現(xiàn)形式。HDL也可以描述更高的抽象層級(jí)如算法級(jí)或者是體系結(jié)構(gòu)級(jí),但目前受限于EDA軟件的發(fā)展,EDA軟件還無(wú)法理解這么高的抽象層次,所以HDL描述這樣抽象層級(jí)是無(wú)法被轉(zhuǎn)化為較低的抽象層級(jí)的,這也就是所謂的不可綜合。所以在閱讀或編寫HDL語(yǔ)言,尤其是可綜合的HDL,不應(yīng)該看到的是語(yǔ)言本身,而是要看到語(yǔ)言背后所對(duì)應(yīng)的硬件電路結(jié)構(gòu)。如果看到的HDL始終是一條條的代碼,那么這種人永遠(yuǎn)擺脫不了菜鳥的宿命。假如哪一天看到的代碼不再是一行行的代碼而是一塊一塊的硬件模塊,那么恭喜脫離了菜鳥的級(jí)別,進(jìn)入不那么菜的鳥級(jí)別。

3、FPGA本身不算什么,一切皆在FPGA之外這一點(diǎn)恐怕也是很多學(xué)FPGA的菜鳥最難理解的地方。

FPGA是給誰(shuí)用的?很多學(xué)校解釋為給學(xué)微電子專業(yè)或者集成電路設(shè)計(jì)專業(yè)的學(xué)生用的,其實(shí)這不過(guò)是很多學(xué)校受資金限制,賣不起專業(yè)的集成電路設(shè)計(jì)工具而用FPGA工具替代而已。其實(shí)FPGA是給設(shè)計(jì)電子系統(tǒng)的工程師使用的。這些工程師通常是使用已有的芯片搭配在一起完成一個(gè)電子設(shè)備,如基站、機(jī)頂盒、視頻監(jiān)控設(shè)備等。當(dāng)現(xiàn)有芯片無(wú)法滿足系統(tǒng)的需求時(shí),就需要用FPGA來(lái)快速的定義一個(gè)能用的芯片。前面說(shuō)了,F(xiàn)PGA里面無(wú)法就是一些“真值表”、觸發(fā)器、各種連線以及一些硬件資源,電子系統(tǒng)工程師使用FPGA進(jìn)行設(shè)計(jì)時(shí)無(wú)非就是考慮如何將這些以后資源組合起來(lái)實(shí)現(xiàn)一定的邏輯功能而已,而不必像IC設(shè)計(jì)工程師那樣一直要關(guān)注到最后芯片是不是能夠被制造出來(lái)。本質(zhì)上和利用現(xiàn)有芯片組合成不同的電子系統(tǒng)沒有區(qū)別,只是需要關(guān)注更底層的資源而已。要想把FPGA用起來(lái)還是簡(jiǎn)單的,因?yàn)闊o(wú)非就是那些資源,在理解了前面兩點(diǎn)再搞個(gè)實(shí)驗(yàn)板,跑跑實(shí)驗(yàn),做點(diǎn)簡(jiǎn)單的東西是可以的。而真正要把FPGA用好,那光懂點(diǎn)FPGA知識(shí)就遠(yuǎn)遠(yuǎn)不夠了。因?yàn)樽罱K要讓FPGA里面的資源如何組合,實(shí)現(xiàn)何種功能才能滿足系統(tǒng)的需要,那就需要懂得更多更廣泛的知識(shí)。

目前FPGA的應(yīng)用主要是三個(gè)方向:

第一個(gè)方向,也是傳統(tǒng)方向主要用于通信設(shè)備的高速接口電路設(shè)計(jì),這一方向主要是用FPGA處理高速接口的協(xié)議,并完成高速的數(shù)據(jù)收發(fā)和交換。這類應(yīng)用通常要求采用具備高速收發(fā)接口的FPGA,同時(shí)要求設(shè)計(jì)者懂得高速接口電路設(shè)計(jì)和高速數(shù)字電路板級(jí)設(shè)計(jì),具備EMC/EMI設(shè)計(jì)知識(shí),以及較好的模擬電路基礎(chǔ),需要解決在高速收發(fā)過(guò)程中產(chǎn)生的信號(hào)完整性問(wèn)題。FPGA最初以及到目前最廣的應(yīng)用就是在通信領(lǐng)域,一方面通信領(lǐng)域需要高速的通信協(xié)議處理方式,另一方面通信協(xié)議隨時(shí)在修改,非常不適合做成專門的芯片。因此能夠靈活改變功能的FPGA就成為首選。到目前為止FPGA的一半以上的應(yīng)用也是在通信行業(yè)。

第二個(gè)方向,可以稱為數(shù)字信號(hào)處理方向或者數(shù)學(xué)計(jì)算方向,因?yàn)楹艽蟪潭壬线@一方向已經(jīng)大大超出了信號(hào)處理的范疇。例如早就在2006年就聽說(shuō)老美將FPGA用于金融數(shù)據(jù)分析,后來(lái)又見到有將FPGA用于醫(yī)學(xué)數(shù)據(jù)分析的案例。在這一方向要求FPGA設(shè)計(jì)者有一定的數(shù)學(xué)功底,能夠理解并改進(jìn)較為復(fù)雜的數(shù)學(xué)算法,并利用FPGA內(nèi)部的各種資源使之能夠變?yōu)閷?shí)際的運(yùn)算電路。目前真正投入實(shí)用的還是在通信領(lǐng)域的無(wú)線信號(hào)處理、信道編解碼以及圖像信號(hào)處理等領(lǐng)域,其它領(lǐng)域的研究正在開展中,之所以沒有大量實(shí)用的主要原因還是因?yàn)閷W(xué)金融的、學(xué)醫(yī)學(xué)的不了解這玩意。不過(guò)最近發(fā)現(xiàn)歐美有很多電子工程、計(jì)算機(jī)類的博士轉(zhuǎn)入到金融行業(yè),開展金融信號(hào)處理,相信隨著轉(zhuǎn)入的人增加,F(xiàn)PGA在其它領(lǐng)域的數(shù)學(xué)計(jì)算功能會(huì)更好的發(fā)揮出來(lái),而我也有意做一些這些方面的研究。不過(guò)國(guó)內(nèi)學(xué)金融的、學(xué)醫(yī)的恐怕連數(shù)學(xué)都很少用到,就不用說(shuō)用FPGA來(lái)幫助他們完成數(shù)學(xué)_運(yùn)算了,這個(gè)問(wèn)題只有再議了。

第三個(gè)方向就是所謂的SOPC方向,其實(shí)嚴(yán)格意義上來(lái)說(shuō)這個(gè)已經(jīng)在FPGA設(shè)計(jì)的范疇之內(nèi),只不過(guò)是利用FPGA這個(gè)平臺(tái)搭建的一個(gè)嵌入式系統(tǒng)的底層硬件環(huán)境,然后設(shè)計(jì)者主要是在上面進(jìn)行嵌入式軟件開發(fā)而已。設(shè)計(jì)對(duì)于FPGA本身的設(shè)計(jì)時(shí)相當(dāng)少的。但如果涉及到需要在FPGA做專門的算法加速,實(shí)際上需要用到第二個(gè)方向的知識(shí),而如果需要設(shè)計(jì)專用的接口電路則需要用到第一個(gè)方向的知識(shí)。

就目前SOPC方向發(fā)展其實(shí)遠(yuǎn)不如第一和第二個(gè)方向,其主要原因是因?yàn)镾OPC以FPGA為主,或者是在FPGA內(nèi)部的資源實(shí)現(xiàn)一個(gè)“軟”的處理器,或者是在FPGA內(nèi)部嵌入一個(gè)處理器核。但大多數(shù)的嵌入式設(shè)計(jì)卻是以軟件為核心,以現(xiàn)有的硬件發(fā)展情況來(lái)看,多數(shù)情況下的接口都已經(jīng)標(biāo)準(zhǔn)化,并不需要那么大的FPGA邏輯資源去設(shè)計(jì)太過(guò)復(fù)雜的接口。而且就目前看來(lái)SOPC相關(guān)的開發(fā)工具還非常的不完善,以ARM為代表的各類嵌入式處理器開發(fā)工具卻早已深入人心,大多數(shù)以ARM為核心的SOC芯片提供了大多數(shù)標(biāo)準(zhǔn)的接口,大量成系列的單片機(jī)/嵌入式處理器提供了相關(guān)行業(yè)所需要的硬件加速電路,需要專門定制硬件場(chǎng)合確實(shí)很少。通常是在一些特種行業(yè)才會(huì)在這方面有非常迫切的需求。目前Xilinx已經(jīng)將ARMcortex- A9的硬核嵌入到FPGA里面,未來(lái)對(duì)嵌入式的發(fā)展有很大推動(dòng),不過(guò),不要忘了很多老掉牙的8位單片機(jī)還在嵌入式領(lǐng)域混呢,嵌入式主要不是靠硬件的差異而更多的是靠軟件的差異來(lái)體現(xiàn)價(jià)值的。

我曾經(jīng)看好的是cypress的Psoc這一想法。和SOPC系列不同,Psoc的思想史載SOC芯片里面去嵌入那么一小塊FPGA,那這樣其實(shí)可以滿足嵌入式的那些微小的硬件接口差異,比如某個(gè)運(yùn)用需要4個(gè)USB,而通常的處理器不會(huì)提供那么多,就可以用這么一塊FPGA來(lái)提供多的USB接口。而另一種運(yùn)用需要6個(gè)UART,也可以用同樣的方法完成。對(duì)于嵌入式設(shè)計(jì)公司來(lái)說(shuō)他們只需要備貨一種芯片,就可以滿足這些設(shè)計(jì)中各種微小的差異變化。其主要的差異化仍然是通過(guò)軟件來(lái)完成。但目前cypress過(guò)于封閉,如果其采用ARM作為處理器內(nèi)核,借助其完整的工具鏈。同時(shí)開放IP合作,讓大量的第三方為它提供IP設(shè)計(jì),其實(shí)是很有希望的。但目前cypress的日子怕不太好過(guò),Psoc的思想也不知道何時(shí)能夠發(fā)光。

4、數(shù)字邏輯知識(shí)是根本。

無(wú)論是FPGA的哪個(gè)方向,都離不開數(shù)字邏輯知識(shí)的支撐。FPGA說(shuō)白了是一種實(shí)現(xiàn)數(shù)字邏輯的方式而已。如果連最基本的數(shù)字邏輯的知識(shí)都有問(wèn)題,學(xué)習(xí)FPGA的愿望只是空中樓閣而已。而這,恰恰是很多菜鳥最不愿意去面對(duì)的問(wèn)題。數(shù)字邏輯是任何電子電氣類專業(yè)的專業(yè)基礎(chǔ)知識(shí),也是必須要學(xué)好的一門課。很多人無(wú)非是學(xué)習(xí)了,考個(gè)試,完了。如果不能將數(shù)字邏輯知識(shí)爛熟于心,養(yǎng)成良好的設(shè)計(jì)習(xí)慣,學(xué)FPGA到最后仍然是霧里看花水中望月,始終是一場(chǎng)空的。以上四條只是我目前總結(jié)菜鳥們?cè)趯W(xué)習(xí)FPGA時(shí)所最容易跑偏的地方,F(xiàn)PGA的學(xué)習(xí)其實(shí)就像學(xué)習(xí)圍棋一樣,學(xué)會(huì)如何在棋盤上落子很容易,成為一位高手卻是難上加難。要真成為李昌鎬那樣的神一般的選手,除了靠刻苦專研,恐怕還確實(shí)得要一點(diǎn)天賦。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論