2.6.3 多級邏輯時鐘

當產生門控時鐘的組合邏輯超過一級(即超過單個的“與”門或“或”門)時,證設計項目的可靠性變得很困難。即使樣機或仿真結果沒有顯示出靜態險象,但實際上仍然可能存在著危險。通常,我們不應該用多級組合邏輯去鐘控PLD設計中的觸發器。

圖7給出一個含有險象的多級時鐘的例子。時鐘是由SEL引腳控制的多路選擇器輸出的。多路選擇器的輸入是時鐘(CLK)和該時鐘的2分頻(DIV2)。由圖7 的定時波形圖看出,在兩個時鐘均為邏輯1的情況下,當SEL線的狀態改變時,存在靜態險象。險象的程度取決于工作的條件。 多級邏輯的險象是可以去除的。例如,你可以插入“冗余邏輯”到設計項目中。然而,PLD/FPGA編譯器在邏輯綜合時會去掉這些冗余邏輯,使得驗證險象是否真正被去除變得困難了。為此,必須應尋求其它方法來實現電路的功能。

圖7 有靜態險象的多級時鐘

圖8給出圖7電路的一種單級時鐘的替代方案。圖中SEL引腳和DIV2信號用于使能D觸發器的使能輸入端,而不是用于該觸發器的時鐘引腳。采用這個電路并不需要附加PLD的邏輯單元,工作卻可靠多了。 不同的系統需要采用不同的方法去除多級時鐘,并沒有固定的模式。

圖8 無靜態險象的多級時鐘(這個電路邏輯上等效于圖7,但卻可靠的多)

2.6.4 行波時鐘

另一種流行的時鐘電路是采用行波時鐘,即一個觸發器的輸出用作另一個觸發器的時鐘輸入。如果仔細地設計,行波時鐘可以象全局時鐘一樣地可靠工作。然而,行波時鐘使得與電路有關的定時計算變得很復雜。行波時鐘在行波鏈上各觸發器的時鐘之間產生較大的時間偏移,并且會超出最壞情況下的建立時間、保持時間和電路中時鐘到輸出的延時,使系統的實際速度下降。

用計數翻轉型觸發器構成異步計數器時常采用行波時鐘,一個觸發器的輸出鐘控下一個觸發器的輸入,參看圖9同步計數器通常是代替異步計數器的更好方案,這是因為兩者需要同樣多的宏單元而同步計數器有較快的時鐘到輸出的時間。圖10給出具有全局時鐘的同步計數器,它和圖9功能相同,用了同樣多的邏輯單元實現,卻有較快的時鐘到輸出的時間。幾乎所有PLD開發軟件都提供多種多樣的同步計數器。

圖9 行波時鐘

圖10 行波時鐘轉換成全局時鐘

(這個3位計數器是圖9異步計數器的替代電路,它用了同樣的3個宏單元,但有更短的時鐘到輸出的延時)

2.6.5 多時鐘系統

許多系統要求在同一個PLD內采用多時鐘。最常見的例子是兩個異步微處理器器之間的接口,或微處理器和異步通信通道的接口。由于兩個時鐘信號之間要求一定的建立和保持時間,所以,上述應用引進了附加的定時約束條件。它們也會要求將某些異步信號同步化。

圖11給出一個多時鐘系統的實例。CLK_A用以鐘控REG_A,CLK_B用于鐘控REG_B,由于REG_A驅動著進入REG_B的組合邏輯,故CLK_A的上升沿相對于CLK_B的上升沿有建立時間和保持時間的要求。由于REG_B不驅動饋到REG_A的邏輯,CLK_B的上升沿相對于CLK_A沒有建立時間的要求。此外,由于時鐘的下降沿不影響觸發器的狀態,所以CLK_A和CLK_B的下降沿之間沒有時間上的要求。如圖4,2.II所示,電路中有兩個獨立的時鐘,可是,在它們之間的建立時間和保持時間的要求是不能保證的。在這種情況下,必須將電路同步化。圖12 給出REG_A的值(如何在使用前)同CLK_B同步化。新的觸發器REG_C由GLK_B觸控,保證REG_G的輸出符合REG_B的建立時間。然而,這個方法使輸出延時了一個時鐘周期。

?

圖ll 多時鐘系統 (定時波形示出CLK_A的上升沿相對于CLK_B的上升沿有建立時間和保持時間的約束條件)

圖12 具有同步寄存器輸出的多時鐘系統 (如果CLK_A和CLK_B是相互獨立的,則REG—A的輸出必須在它饋送到1REG_B之前,用REG_C同步化)

在許多應用中只將異步信號同步化還是不夠的,當系統中有兩個或兩個以上非同源時鐘的時候,數據的建立和保持時間很難得到保證,我們將面臨復雜的時間問題。最好的方法是將所有非同源時鐘同步化。使用PLD內部的鎖項環(PLL或DLL)是一個效果很好的方法,但不是所有PLD都帶有PLL、DLL,而且帶有PLL功能的芯片大多價格昂貴,所以除非有特殊要求,一般場合可以不使用帶PLL的PLD。 這時我們需要使用帶使能端的D觸發器,并引入一個高頻時鐘。

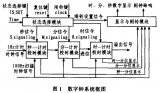

圖13 不同源時鐘

如圖13所示,系統有兩個不同源時鐘,一個為3MHz,一個為5MHz,不同的觸發器使用不同的時鐘。為了系統穩定,我們引入一個20MHz時鐘,將3M和5M時鐘同步化,如圖15所示。 20M的高頻時鐘將作為系統時鐘,輸入到所有觸發器的的時鐘端。3M_EN 和5M_EN將控制所有觸發器的使能端。即原來接3M時鐘的觸發器,接20M時鐘,同時3M_EN 將控制該觸發器使能 ,原接5M時鐘的觸發器,也接20M時鐘,同時5M_EN 將控制該觸發器使能。 這樣我們就可以將任何非同源時鐘同步化。

圖14 同步化任意非同源時鐘

(一個DFF和后面非門,與門構成時鐘上升沿檢測電路)

另外,異步信號輸入總是無法滿足數據的建立保持時間,容易使系統進入亞穩態,所以也建議設計者把所有異步輸入都先經過雙觸發器進行同步化.

小結:穩定可靠的時鐘是系統穩定可靠的重要條件,我們不能夠將任何可能含有毛刺的輸出作為時鐘信號,并且盡可能只使用一個全局時鐘,對多時鐘系統要注意同步異步信號和非同源時鐘。

2.6.6 多時鐘系統設計的一些方法:

如果時鐘間存在著固定的頻率倍數,這種情況下它們的相位一般具有固定關系,可以采用下述方法處理;

使用高頻時鐘作為工作時鐘,使用低頻時鐘作為使能信號,當功耗不作為首要因素時建議使用這種方式;

在仔細分析時序的基礎上描述兩個時鐘轉換處的電路;

如果電路中存在兩個不同頻率的時鐘,并且頻率無關,可以采用如下策略:

利用高頻時鐘采樣兩個時鐘,在電路中使用高頻時鐘作為電路的工作時鐘,經采樣后的低頻時鐘作為使能;

在時鐘同步單元中采用兩次同步法

使用握手信號

使用雙時鐘FIFO進行數據緩沖

時鐘同步化,如果系統中存在兩個時鐘clk_a和clk_b,設計者可以使用頻率高于max(clk_a,clk_b)兩倍的時鐘來作為采樣時鐘,兩個低頻時鐘經過處理后可以作為觸發器的使能信號,采用這種方案的好處是整個電路采用單時鐘工作,但需要一個額外的高頻時鐘,當電路有功耗要求時,設計者應該仔細考慮;

使用20M采樣3M和5M,syn_5M作為原來5M信號驅動寄存器的使能信號;

使用高頻時鐘采樣2個低頻時鐘原理圖

使用高頻時鐘采樣2個低頻時鐘波形圖

在構件由兩個不同系統時鐘控制工作的模塊之間的同步模塊時,應該遵守下面原則:兩個采用不同時鐘工作的寄存器之間不應該再出現邏輯電路,而應該僅僅是一種連接關系,具體如下圖所示,這種方法有利于控制建立保持時間的滿足。

握手信號機制是異步系統之間通信的基本方式,我們在處理不同時鐘之間的接口時,也可以采用這種方式,但需要注意的是設計者應該仔細分析握手和應答信號有效持續的時間,確保采樣數據的正確性。

目前各種器件中提供的雙時鐘FIFO宏單元很好的提供了對異步雙時鐘的訪問,單元的內部有協調兩個時鐘的電路,確保讀寫的正確性。可以利用這個器件完成數據的同步。

1. 采用全局時鐘,不要將時鐘參與運算。系統提供一定數量的全局時鐘線,在布局布線時,盡量滿足這些信號的要求以減小時鐘偏移和傾斜。如果時序安排不合理使用了較多gated clock,那么這些時鐘的偏斜就會較大,不能保障建立時間和保持時間,導致電路工作頻率降低或無法工作。

2. 以寄存器為邊界劃分工作模塊。在設計較大規模的電路時,分模塊設計是必不可少的,在各模塊通過之后再進行系統的聯調。但由于在單模塊調試和聯調時布線資源的占用緊張程度不同,使得每個模塊的輸出無法保持與單獨布線時相同,在聯調時造成困難。如果每一個模塊的輸出端口都采用寄存器輸出,那么即使在整體布局布線后,各模塊的輸出依然可以保證原來的時序,這使得聯調的工作效率大大提高。加入這些寄存器也使得電路的可測性有所提高。

3. 組合邏輯盡量采用并行結構,降低寄存器間組合路徑的延遲是提高系統工作頻率最主要的手段,因此在完成相同功能的前提下應該盡量使用并行邏輯,如圖6所示。

圖6 四輸入比較器的串行和并行實現

如果沒有優先級要求應該盡量采用case語句來描述,這樣綜合出來的電路并行度要大一些,如果采用if-then-else結構,綜合出來的電路都是串行的,增大了時延路徑。

4. 在描述中應該消除鎖存器,如果某個數據需要保存應該合理安排使用寄存器,因為鎖存器在整個工作電平有效期間都對輸入敏感,輸入中的任何毛刺經過鎖存器后都不會消除,這樣使得在其后的組合電路發生競爭冒險的可能性大為提高,影響電路性能。一些不適當的描述也會使得產生不必要的鎖存器,增加了電路的面積。

5. 在設計中應該盡量采用同步設計,信號被時鐘采樣后再參與邏輯運算,這樣可以隔斷組合路徑,也可以消除毛刺。在設計中,組合信號的輸出不允許反饋作為該組合邏輯的輸入,這樣可以避免組合環。

電子發燒友App

電子發燒友App

評論