大家好,我最近自己開(kāi)始進(jìn)行VHDL編程。因?yàn)閹讉€(gè)錯(cuò)誤而陷入困境。我在VHDL的結(jié)構(gòu)代碼中得到3個(gè)錯(cuò)誤。其中一個(gè)錯(cuò)誤是“模型”和“2”在目標(biāo)庫(kù)中具有不同的特征。用戶組件'和2'與庫(kù)原語(yǔ)'和2'沖突請(qǐng)幫幫我。我附上了錯(cuò)誤的屏幕截圖,請(qǐng)檢查它們并幫助我繼續(xù)進(jìn)行

2020-03-30 10:00:12

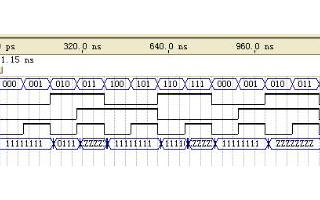

語(yǔ)句第7章 VHDL的描述風(fēng)格7.1 行為描述7.2 數(shù)據(jù)流描述7.3 結(jié)構(gòu)描述第8章 仿真8.1 VHDL仿真8.2 延時(shí)模型8.2.1 固有延時(shí)8.2.2 傳輸延時(shí)8.3 仿真Δ8.4 仿真激勵(lì)信號(hào)

2008-06-04 10:31:29

VHDL語(yǔ)言是一種用于電路設(shè)計(jì)的高級(jí)語(yǔ)言。它在80年代的后期出現(xiàn)。最初是由美國(guó)國(guó)防部開(kāi)發(fā)出來(lái)供美軍用來(lái)提高設(shè)計(jì)的可靠性和縮減開(kāi)發(fā)周期的一種使用范圍較小的設(shè)計(jì)語(yǔ)言 。VHDL翻譯成中文就是

2015-09-30 13:48:29

我在寫VHDL程序的時(shí)候,分成幾個(gè)模塊,可是最后怎么完成頂層設(shè)計(jì)?

2014-09-16 21:23:27

但是寫完語(yǔ)言后創(chuàng)建VHDL測(cè)試臺(tái)顯示,我的vhdl中有實(shí)體與文件名一致,這樣也就無(wú)法通過(guò)vhdl生成原理圖,我使用的是***2004

2015-04-01 21:28:34

我對(duì)運(yùn)放的理解我對(duì)運(yùn)放的理解我對(duì)運(yùn)放的理解我對(duì)運(yùn)放的理解我對(duì)運(yùn)放的理解我對(duì)運(yùn)放的理解我對(duì)運(yùn)放的理解我對(duì)運(yùn)放的理解我對(duì)運(yùn)放的理解我對(duì)運(yùn)放的理解我對(duì)運(yùn)放的理解我對(duì)運(yùn)放的理解我對(duì)運(yùn)放的理解我對(duì)運(yùn)放的理解我對(duì)運(yùn)放的理解我對(duì)運(yùn)放的理解我對(duì)運(yùn)放的理解我對(duì)運(yùn)放的理解我對(duì)運(yùn)放的理解

2012-09-23 15:02:07

我想問(wèn)一下,在STM32外部中斷中我需要用延時(shí),我該怎么延時(shí)?

2017-09-11 18:02:30

`我是FPGA初學(xué)者 ,我想問(wèn)下 ,有vhdl 的程序 ,但是沒(méi)有工程文件 ,我要添加哪些文件才能運(yùn)行vhdl程序。怎么添加程序才能運(yùn)行生成工程文件。`

2015-12-29 21:28:10

大學(xué)的一些學(xué)習(xí)材料。可是最近有點(diǎn)迷茫,是學(xué)VHDL呢?還是學(xué)Verilog HDL。我網(wǎng)上查,有的說(shuō)VHDL和Verilog HDL應(yīng)用情況差不多,可是又有人說(shuō)現(xiàn)在主要是用Verilog HDL。個(gè)人

2013-09-06 15:03:08

我的altium designer 編寫好vhdl后并成功在原理圖中生成了電路,最后進(jìn)行測(cè)試也就是testbeach時(shí)在生成的.VHDTEST文件中進(jìn)行了少量修改是按書上寫的,應(yīng)該是沒(méi)問(wèn)題的,前面

2015-04-02 20:39:30

Verilog與VHDL(特權(quán)同學(xué)版權(quán)所有)本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》(特權(quán)同學(xué)版權(quán)所有)配套例程下載鏈接:http://pan.baidu.com/s

2015-03-16 12:00:54

VHDL 主要用于描述數(shù)字系統(tǒng)的結(jié)構(gòu)、行為、功能和接口。除了含有許多具有硬件特征的語(yǔ)句外,VHDL 在語(yǔ)言形式、描述風(fēng)格和句法上與一般的計(jì)算機(jī)高級(jí)語(yǔ)言十分相似。VHDL 的程序結(jié)構(gòu)特點(diǎn)是將一項(xiàng)

2018-09-07 09:04:45

我在LED程序里用到了一個(gè)延時(shí)程序,用空語(yǔ)句消耗CPU時(shí)間來(lái)延時(shí),如下void Delay(u32 nCount){while(nCount--);}然后咋 main中調(diào)用 Delay

2018-09-03 09:37:00

我是UCOS初學(xué)者,以前也沒(méi)有學(xué)過(guò)任何RTOS,望大神說(shuō)的仔細(xì)些。我所理解的UCOS任務(wù)調(diào)度都是在延時(shí)函數(shù)中實(shí)現(xiàn)的,假設(shè)我定義了三個(gè)函數(shù):1-start_task ; 2-task1

2020-04-07 22:13:19

原子哥,你好,問(wèn)下,使用OSTimeDlyHMSM()或者OSTimeDly()延時(shí)函數(shù),會(huì)引發(fā)幾次調(diào)度?我的理解是兩次,一次是剛進(jìn)入延時(shí)函數(shù)時(shí),另一次是當(dāng)延時(shí)函數(shù)結(jié)束時(shí),不知這樣理解是否正確?

2020-04-21 04:35:55

大家好 ,我想創(chuàng)建一個(gè)自定義的冷杉過(guò)濾器,但我沒(méi)有足夠的知識(shí)來(lái)設(shè)計(jì)它。所以我可以訪問(wèn)vivado的fir編譯器vhdl代碼,這可以幫助我理解流接口和自定義IP塊的方法。我有一個(gè)簡(jiǎn)單的冷杉過(guò)濾器

2020-04-07 08:37:48

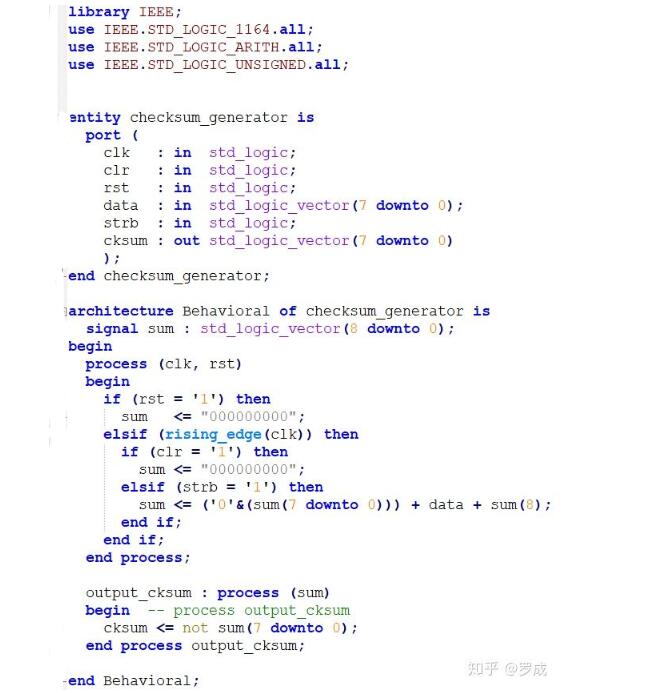

VHDL / verilog并正確地敲出MII接口。后一種方法顯然是一種皇家的痛苦,因?yàn)槟惚仨氂?jì)算校驗(yàn)和,否則操縱TCP / UDP數(shù)據(jù)包的可能性最低......我的問(wèn)題是:我的應(yīng)用程序要求以盡可能低

2019-05-31 03:31:38

嗨,我試圖理解“write_vhdl”和“write_verilog”之間的差異。我有一個(gè)設(shè)計(jì),我想從中創(chuàng)建一個(gè)網(wǎng)表。設(shè)計(jì)是用VERILOG編寫的,我用“write_verilog”命令創(chuàng)建了一個(gè)

2020-03-16 10:29:57

你好!我是FPGA設(shè)計(jì)的新手。我想在我的項(xiàng)目中使用DCM,但是,在我執(zhí)行Xilinx時(shí)鐘向?qū)е螅瑳](méi)有生成響應(yīng)的vhdl文件。我想知道我該怎么生成這個(gè)vhdl文件。我還有其他步驟嗎?謝謝你的考慮

2019-01-15 10:22:23

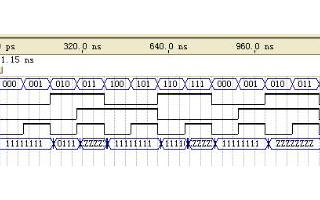

程序如下,這樣的話在num賦給n的時(shí)候,num也同時(shí)被置0吧?怎么延時(shí)執(zhí)行f進(jìn)程呢?想了好久,求解呀!!!g:PROCESS(en)BEGIN IF en'EVENT AND en='0'THEN n0

2012-11-22 17:55:49

各位大神老師好:請(qǐng)教一個(gè)問(wèn)題。據(jù)說(shuō)PIC32單片機(jī)的延時(shí),可以用內(nèi)部計(jì)數(shù)器進(jìn)行延時(shí)。我想延時(shí)2us,但是,死活都不能達(dá)到2us,示波器顯示是40us。示波器用的是虛擬示波器。系統(tǒng)時(shí)鐘是40Mhz下面

2017-10-06 00:23:27

” 定時(shí)器做延時(shí) 比 軟件延時(shí) CPU利用率高 “,在我看過(guò)的一個(gè)按鍵狀態(tài)機(jī)的程序里,覺(jué)得確實(shí)是這樣的;但程序有延時(shí)的地方好像并不能都寫成 狀態(tài)機(jī) 那樣的結(jié)構(gòu)啊,這時(shí)我就不能理解為什么說(shuō) ” 定時(shí)器做延時(shí)

2015-08-03 21:55:23

國(guó)家晶元設(shè)計(jì)中心VHDL內(nèi)部培訓(xùn)資料每個(gè)知識(shí)點(diǎn)都配有例子能幫助大家很好的理解[hide] [/hide]

2012-02-27 14:11:29

掛起之后。1.5ms之后就會(huì)進(jìn)入節(jié)拍的中斷函數(shù)中。然后任務(wù)又會(huì)進(jìn)入就緒狀態(tài)。此時(shí)目標(biāo)延時(shí)應(yīng)該為5ms,但實(shí)際延時(shí)只有1.5ms。這樣延時(shí)函數(shù)就會(huì)產(chǎn)生誤差。不知道我理解的是否正確?如果確實(shí)如我理解的這樣,那又該如何保證實(shí)時(shí)性呢?

2019-09-16 20:58:20

PLZ任何機(jī)構(gòu)都可以建議我如何在vhdl代碼中編寫Expectation maximization algo。我知道理論,但無(wú)法理解編碼的方式.plzzzzz的幫助。以上來(lái)自于谷歌翻譯以下為原文

2019-01-23 07:02:02

作為我項(xiàng)目的一部分,我需要將ADC與7系列FPGA接口,我有一個(gè)SelectIO?接口向?qū)У腎P核。但是,我的整個(gè)項(xiàng)目都在VHDL中,IPi得到的是Verilog。請(qǐng)指出我如何在我的VHDL頂級(jí)模塊中使用該IP核的一些示例。最好的祝福

2020-05-21 12:31:59

我想用DNA(XC6SLX16)加密我的設(shè)計(jì),但我不知道怎么做,有沒(méi)有人可以提供一些VHDL參考?以上來(lái)自于谷歌翻譯以下為原文I want to encryptmy design

2019-07-24 13:19:40

大家好,我想使用IO時(shí)鐘接口對(duì)輸入中的串行信號(hào)進(jìn)行過(guò)采樣。然后,該信號(hào)將由vhdl編程邏輯與全局時(shí)鐘一起使用。我希望使用IO時(shí)鐘以更高的頻率對(duì)這些輸入數(shù)據(jù)進(jìn)行采樣,而不是全局時(shí)鐘提供的數(shù)據(jù),但我

2019-08-07 09:51:55

嗨, 我正在C和MATLAB中實(shí)現(xiàn)圖像比較的代碼。現(xiàn)在我想知道從xilinx上的.c文件中的.m文件(或).vhdl文件創(chuàng)建.vhdl文件的過(guò)程,或者是否有任何可用于此轉(zhuǎn)換的開(kāi)源并且所有.m文件

2019-03-18 13:10:42

將由自定義VHDL代碼寫入。第二個(gè)BRAM地址在Microblaze上為0x00010000。在導(dǎo)出BRAM的第二個(gè)端口以供自定義VHDL代碼使用之后,我對(duì)VHDL端的BRAM地址感到有些困惑

2019-03-04 12:09:00

大家好,我正在嘗試使用VHDL實(shí)現(xiàn)雙曲線tan tan函數(shù),但問(wèn)題是我不知道tanh函數(shù)怎么可以實(shí)現(xiàn)digital所以請(qǐng)如果任何身體可以告訴我這個(gè)想法,以便我可以在VHDL中實(shí)現(xiàn)它會(huì)很好的。非常感謝

2019-02-14 10:20:11

你好我正在處理導(dǎo)入vhdl文件到EDK項(xiàng)目中的pcores-user_logic。我創(chuàng)建了我的系統(tǒng)并將vhdl輸出連接到我的EDK系統(tǒng)。但是當(dāng)我生成比特流時(shí),我得到的錯(cuò)誤就像“無(wú)法在庫(kù)中找到。請(qǐng)確保

2019-03-19 06:11:26

嗨,我喜歡vhdl和fpga。有人告訴我,我們可以使用simulink生成vhdl。我想處理寄存器,查找表和累加器。我只知道simulink上的基本知識(shí)。任何人都可以建議哪種方式最好。如果

2020-03-20 06:16:39

一、VHDL簡(jiǎn)介1.1 VHDL 的歷史VHDL 的 英 文 全 名 是 Very-High-Speed Integrated Circuit Hardware

2020-09-02 19:32:26

或者累減的方法,到一定條件后就退出。好處:好寫,用for循環(huán)或者while循環(huán),不用去理解各種有關(guān)底層硬件的寄存器。壞處:延時(shí)不精準(zhǔn),誤差大,讓CPU持續(xù)空跑,大大浪費(fèi)CPU資源。void delay(uint16 i){#if 0while(i--){}#endiffor(

2022-01-14 06:43:44

用VHDL寫,步進(jìn)延時(shí)電路的設(shè)計(jì),電子設(shè)計(jì)大賽07年C題中關(guān)于步進(jìn)延時(shí)的設(shè)計(jì)

2013-08-05 09:54:45

大家好,我對(duì)VHDL有點(diǎn)新意,我想在你學(xué)習(xí)數(shù)字設(shè)計(jì)的同時(shí),對(duì)你知道對(duì)VHDL有益的書籍有所了解。那么那些真正優(yōu)秀的書籍是什么?

2020-05-22 06:42:27

我看了個(gè)在1602上顯示字符串的代碼,看到要用到延時(shí)程序。我上網(wǎng)查了下,說(shuō)單片機(jī)的速度相對(duì)很多外設(shè)來(lái)說(shuō)已經(jīng)很高了,必須加延時(shí)才能與外設(shè)匹配。我現(xiàn)在有個(gè)疑問(wèn):?jiǎn)纹瑱C(jī)的延時(shí)子程序(比如匯編代碼

2019-11-11 16:32:13

正在學(xué)習(xí)VHDL,有一個(gè)問(wèn)題不知道咋實(shí)現(xiàn),希望大家?guī)兔Α]斎胄盘?hào) I_moen 和I_boen,輸出信號(hào) O_mo 和O_bo。要求:1.I_moen出現(xiàn)上升沿, O_mo轉(zhuǎn)為高電平;同樣

2019-01-25 06:35:20

你能告訴我用戶邏輯是什么嗎?我理解的是user_logic是vhdl模板的主/從ip實(shí)現(xiàn)的?我對(duì)嗎?無(wú)論如何,如果你能詳細(xì)說(shuō)明一下,我會(huì)很高興非常感謝您的幫助!!

2019-11-11 13:54:56

;CTRL=0x01 ;//開(kāi)始倒數(shù)do{ temp=SysTick->CTRL;}while(temp&0x01&&!(temp&(1VAL =0X00; //清空計(jì)數(shù)器//這是延時(shí)多久,怎么實(shí)現(xiàn)的延時(shí)?

2018-11-29 12:28:50

The VHDL Cookbook

好東西哦。網(wǎng)上搜集,希望對(duì)你有用。

2006-03-25 14:37:55 19

19 VHDL基本語(yǔ)法實(shí)例:

2009-05-27 08:57:49 11

11 VHDL基本語(yǔ)法實(shí)例:

2009-05-27 10:32:19 123

123 UART 4 UART參考設(shè)計(jì),Xilinx提供VHDL代碼 uart_vhdl

This zip file contains the following folders

2009-06-14 08:57:14 113

113 VHDL Library of Arithmetic Units fdl

A comprehensive library of arithmetic units written

2009-06-14 09:09:30 17

17 VHDL語(yǔ)言及其應(yīng)用是在作者歷時(shí)七年為通信與信息系統(tǒng)、信號(hào)與信息處理專業(yè)研究生講授VHDL語(yǔ)言及其應(yīng)用課程的教學(xué)實(shí)踐基礎(chǔ)上編寫而成的。全書共分15章,以教授完整的VHDL語(yǔ)言體

2009-07-10 17:21:44 18

18 VHDL語(yǔ)言及其應(yīng)用的主要內(nèi)容:第一章 硬件模型概述第二章 基本的VHDL編程語(yǔ)言第三章 VHDL模型的組織第四章 VHDL綜合工具第五章 VHDL應(yīng)用樣例附錄A VHDL

2009-07-20 12:06:15 0

0 VHDL語(yǔ)言概述:本章主要內(nèi)容:硬件描述語(yǔ)言(HDL)VHDL語(yǔ)言的特點(diǎn)VHDL語(yǔ)言的開(kāi)發(fā)流程

1.1 1.1 硬件描述語(yǔ)言( 硬件描述語(yǔ)言(HDL HDL)H

2009-08-09 23:13:20 47

47 1. INSTANTIATING LPM in VHDLTo promote LPM usage in VHDL design community, this section describes

2009-09-13 14:29:03 26

26 VHDL 語(yǔ)言程序的元素:本章主要內(nèi)容:VHDL語(yǔ)言的對(duì)象VHDL語(yǔ)言的數(shù)據(jù)類型VHDL語(yǔ)言的運(yùn)算符VHDL語(yǔ)言的標(biāo)識(shí)符VHDL語(yǔ)言的詞法單元

2009-09-28 14:32:21 41

41 vhdl數(shù)字系統(tǒng)設(shè)計(jì)是數(shù)字電路自動(dòng)化設(shè)計(jì)(EDA)入門的工具書。其內(nèi)容主要包括:用VHDL語(yǔ)言設(shè)計(jì)的基本組合電路、時(shí)序電路、數(shù)字綜合電路、電路圖輸入法要領(lǐng)概述、實(shí)用VHDL語(yǔ)句

2009-10-08 21:54:01 0

0 VHDL基礎(chǔ)教程:VHDL語(yǔ)言及其應(yīng)用目錄:第1章 VHDL基本概念 1.1 數(shù)字系統(tǒng)建模 1.2 建模的域和級(jí) 1.3 建模語(yǔ)言 1.4 VHDL建模的概念 1.5 一個(gè)VHDL設(shè)計(jì)實(shí)例 1 6

2009-10-16 18:17:58 357

357 VHDL 數(shù)位電子鐘在這個(gè)數(shù)位電子鐘我們使用可支持VHDL 格式的MAX+plusII 軟件開(kāi)發(fā)工具來(lái)做設(shè)計(jì),利用VHDL 硬件描述語(yǔ)言的方式,將一個(gè)復(fù)雜的電路寫成一顆IC,有錯(cuò)誤也不用像以前

2009-11-22 17:50:38 174

174 VHDL深入教程

2009-12-05 16:33:18 199

199 VHDL實(shí)例大全

2010-04-19 13:58:00 239

239 VHDL源程序100例

2010-11-01 17:05:30 319

319 vhdl是什么意思

VHDL 語(yǔ)言的英文全名是 Very High Speed Integrated Circuit Hardware Description Language ,即超高速集

2008-09-02 12:55:59 7732

7732 實(shí)驗(yàn)六、VHDL的基本描述語(yǔ)句設(shè)計(jì)一? 實(shí)驗(yàn)?zāi)康?掌握VHDL語(yǔ)言的基本結(jié)構(gòu)及設(shè)計(jì)的輸入方法。2掌握VHDL語(yǔ)言的基本描述語(yǔ)句的使用方法。二? 實(shí)驗(yàn)設(shè)備

2009-03-13 19:23:57 1998

1998 實(shí)驗(yàn)八、VHDL語(yǔ)言的組合電路設(shè)計(jì)一? 實(shí)驗(yàn)?zāi)康?掌握VHDL語(yǔ)言的基本結(jié)構(gòu)及設(shè)計(jì)的輸入方法。2掌握VHDL語(yǔ)言的組合電路設(shè)計(jì)方法。二? 實(shí)驗(yàn)設(shè)備與儀器

2009-03-13 19:26:58 2368

2368 摘要:為防止電池過(guò)放電,DS2784提供欠壓保護(hù)。本應(yīng)用筆記解釋了欠壓保護(hù)延時(shí)(tUVD)是如何實(shí)現(xiàn)的。

緒論DS2784具有欠壓保護(hù)電路,可防止電池過(guò)放電。當(dāng)檢測(cè)

2009-04-30 11:14:19 1634

1634

帶有延時(shí)的備份電池方案

本應(yīng)用筆記介紹了主電源和備份電池通過(guò)二極管“或”邏輯電路與負(fù)載連接的方案。這一架構(gòu)很容易理解,但當(dāng)電池電壓

2010-01-26 16:30:46 367

367

文章在MAX+PLUS II 開(kāi)發(fā)環(huán)境下采用VHDL 語(yǔ)言設(shè)計(jì)并實(shí)現(xiàn)了電表抄表器討論了系統(tǒng)的四個(gè)組成模塊的設(shè)計(jì)和VHDL 的實(shí)現(xiàn)每個(gè)模塊采用RTL 級(jí)描述整體的生成采用圖形輸入法通過(guò)波形仿真下載芯

2011-09-23 17:56:11 40

40 本文詳細(xì)討論了VHDL語(yǔ)句對(duì)PLD設(shè)計(jì)的影響和設(shè)計(jì)經(jīng)驗(yàn),經(jīng)典文章,值得仔細(xì)閱讀消化。, PLD Programming Using VHDL

2012-01-17 11:20:54 0

0 簡(jiǎn)單介紹了VHDL的實(shí)際應(yīng)用的注意事項(xiàng),比較適合新手入門

2015-11-02 17:32:33 0

0 本書以 VHDL 程序設(shè)計(jì)基礎(chǔ)與工程實(shí)踐為內(nèi)容,全面介紹了 VHDL 程序設(shè)計(jì)的基礎(chǔ)知

識(shí)和基本技術(shù),并結(jié)合工程實(shí)例講解電路設(shè)計(jì)的基本流程和 VHDL技術(shù)的應(yīng)用。本書基本涵

2016-02-17 15:52:13 3

3 平時(shí)在寫關(guān)于時(shí)序的程序時(shí),往往會(huì)見(jiàn)到while的延時(shí)函數(shù),但是延時(shí)時(shí)間往往說(shuō)法不一,這篇文章有助于對(duì)延時(shí)函數(shù)的理解。

2016-07-19 17:34:49 0

0 VHDL語(yǔ)言編程學(xué)習(xí)之VHDL硬件描述語(yǔ)言

2016-09-01 15:27:27 0

0 學(xué)好VHDL的重要性 對(duì)VHDL的 介紹

2016-09-02 16:54:40 17

17 硬件描述語(yǔ)言VHDL的學(xué)習(xí)文檔,詳細(xì)的介紹了VHDL

2016-09-02 17:00:53 12

12 VHDL語(yǔ)言要素,大學(xué)EDA課程必備資料,在實(shí)際的應(yīng)用中,VHDL仿真器講INTEGER類型的數(shù)據(jù)作為有符號(hào)數(shù)處理,而綜合器將INTEGER作為無(wú)符號(hào)數(shù)處理. VHDL綜合器要求利用RANGE子句

2016-11-21 15:40:34 0

0 一篇文章叫你學(xué)會(huì)用VHDL寫TESTBENCH

2016-11-23 11:52:46 11

11 VHDL實(shí)用教程,很好的一本教材,適合初學(xué)者

2016-11-11 15:51:00 15

15 vhdl入門

2016-12-16 16:30:02 23

23 VHDL并行語(yǔ)句

2016-12-11 23:38:39 0

0 vhdl

2017-10-23 08:39:35 10

10 VHDL作為電路的硬件描述語(yǔ)言,并且已經(jīng)在電路中得到了廣泛的運(yùn)用。本文主要介紹了什么是vhdl、vhdl有哪些特點(diǎn)、vhdl的優(yōu)勢(shì)以及詳細(xì)的說(shuō)明了8位移位寄存器vhdl代碼詳情。

2017-12-22 15:11:01 16224

16224 本文檔的主要內(nèi)容詳細(xì)介紹的是VHDL教程之使用VHDL進(jìn)行電子設(shè)計(jì)所需的所有資料包括了:VHDL設(shè)計(jì)基礎(chǔ)知識(shí),VHDL并行語(yǔ)句,VHDL程序?qū)嶓w,VHDL入門,VHDL語(yǔ)言要素,EDA設(shè)計(jì)流程及其工具,IA64 應(yīng)用程序寄存器,LCD液晶顯示漢字字符集表,OCMJ 系列液晶顯示器控制命令集表等

2018-09-25 08:00:00 0

0 本文檔的主要內(nèi)容詳細(xì)介紹的是VHDL教程之VHDL語(yǔ)言元素的詳細(xì)資料概述一內(nèi)容包括了:1. VHDL語(yǔ)言的客體2 VHDL語(yǔ)言的數(shù)據(jù)類型3 VHDL數(shù)據(jù)類型轉(zhuǎn)換4 VHDL詞法規(guī)則與標(biāo)識(shí)符

2018-11-05 08:00:00 0

0 FreeRTOS中相對(duì)延時(shí)和絕對(duì)延時(shí)的區(qū)別

2020-03-12 10:32:09 7831

7831

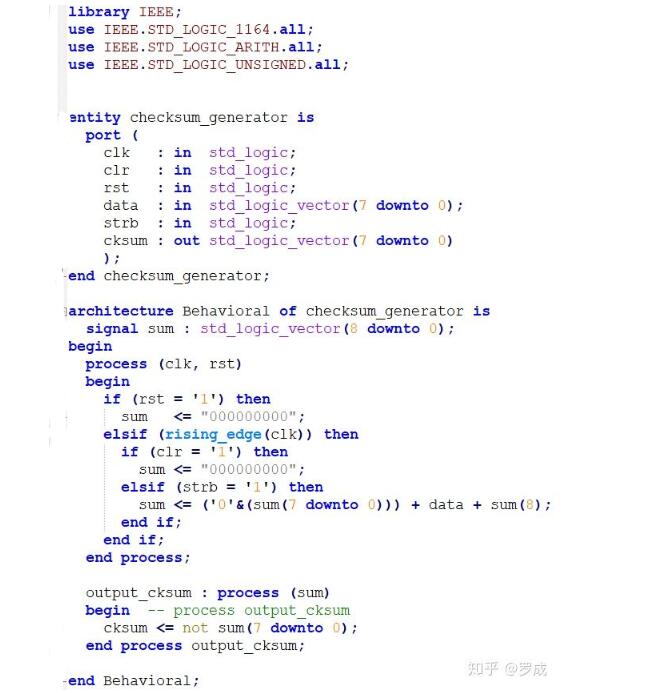

在VHDL程序中,實(shí)體(ENTITY)和結(jié)構(gòu)體(ARCHITECTURE)這兩個(gè)基本結(jié)構(gòu)是必須的,他們可以構(gòu)成最簡(jiǎn)單的VHDL程序。通常,最簡(jiǎn)單的VHDL程序結(jié)構(gòu)中還包含另一個(gè)最重要的部分,即庫(kù)(LIBRARY)和程序包(PACKAGE)。

2020-04-23 15:43:38 4224

4224 VHDL是一種用來(lái)描述數(shù)字邏輯系統(tǒng)的“編程語(yǔ)言”。它通過(guò)對(duì)硬件行為的直接描述來(lái)實(shí)現(xiàn)對(duì)硬件的物理實(shí)現(xiàn),代表了當(dāng)今硬件設(shè)計(jì)的發(fā)展方向。VHDL是為了滿足邏輯設(shè)計(jì)過(guò)程中的各種需求而設(shè)計(jì)的。

2020-04-23 15:51:03 2362

2362

什么是vhdl語(yǔ)言 VHDL 的英文全名是VHSIC Hardware Description Language(VHSIC硬件描述語(yǔ)言)。VHSIC是Very High Speed

2020-04-23 15:58:49 10242

10242 今天給大家分享一個(gè)VHDL和Verilog的工具。很多新手初次學(xué)習(xí)FPGA都曾遇到過(guò)一個(gè)問(wèn)題:是學(xué)Verilog OR VHDL?

2020-08-25 09:22:05 6116

6116

本文概述了VHDL測(cè)試臺(tái)和其他相關(guān)主題。它是為一個(gè)數(shù)字設(shè)計(jì)工程師編寫的,他幾乎沒(méi)有VHDL或編程經(jīng)驗(yàn),以便更好地理解VHDL的編寫和測(cè)試臺(tái)的使用。并對(duì)VHDL的發(fā)展前景進(jìn)行了展望。

2021-01-20 15:17:14 19

19 本手冊(cè)討論VHDL和Synario可編程IColution。本手冊(cè)旨在補(bǔ)充可編程IC入門手冊(cè)中的材料本手冊(cè)中討論了以下主題HDL語(yǔ)言結(jié)構(gòu)如何編寫可合成的VHDL如何控制VHDL設(shè)計(jì)的實(shí)現(xiàn)VHDL數(shù)據(jù)

2021-01-21 16:02:13 32

32 在實(shí)現(xiàn)單片機(jī)功能的時(shí)候,經(jīng)常會(huì)用到延時(shí)函數(shù),那么延時(shí)函數(shù)的原理也是非常有必要了解的。一般我們寫延時(shí)函數(shù)的時(shí)候,默認(rèn)的晶振頻率fosc=12MHZ,而機(jī)器周期T=12/fosc=1us。這里我們來(lái)寫

2021-11-11 09:36:02 94

94 文章目錄中斷延時(shí)通過(guò)在中斷中的計(jì)數(shù)值的不斷遞減來(lái)達(dá)到精確延時(shí),而非中斷則通過(guò)在循環(huán)里不停查詢寄存器數(shù)值來(lái)達(dá)到精確延時(shí)。前者因?yàn)橹袛嗟拇嬖冢焕谠谄渌袛嘀姓{(diào)用延時(shí)函數(shù)。在很多延時(shí)教程中,都喜歡推薦非中斷式的延時(shí)。不過(guò)對(duì)于非特殊情況,兩者的效果是一樣的。反而非中斷延時(shí)需要操作寄存器,反而更難理解。

2021-11-24 19:36:02 0

0 或者累減的方法,到一定條件后就退出。好處:好寫,用for循環(huán)或者while循環(huán),不用去理解各種有關(guān)底層硬件的寄存器。壞處:延時(shí)不精準(zhǔn),誤差大,讓CPU持續(xù)空跑,大大浪費(fèi)CPU資源。void delay(uint16 i){ #if 0 while(i--) {} #endif for(

2022-01-14 12:49:15 5

5 CPU頻率一般為晶振頻率,當(dāng)接入外部晶振時(shí),CPU頻率為外頻乘以內(nèi)頻。延時(shí)函數(shù)通過(guò)運(yùn)行一次計(jì)算CPU所用的時(shí)間來(lái)達(dá)到延時(shí)的延時(shí)的目的,延時(shí)時(shí)間為:計(jì)算次數(shù)/cpu頻率(MHZ)=延時(shí)時(shí)間(us)

2022-01-18 10:26:20 3

3 嵌入式軟件代碼中延時(shí)是很常見(jiàn)的,只是延時(shí)種類有很多,看你用什么延時(shí)。

2022-08-12 08:48:01 1432

1432 vhdl描述半加器

2023-02-24 11:08:31 0

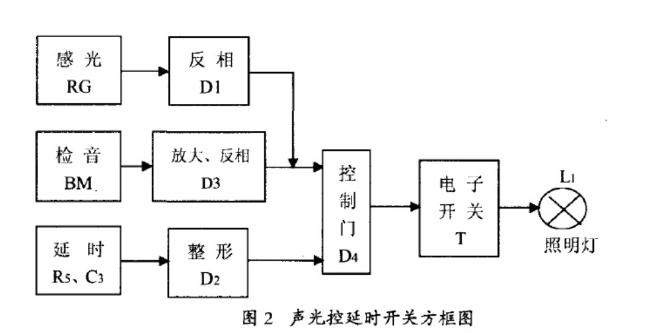

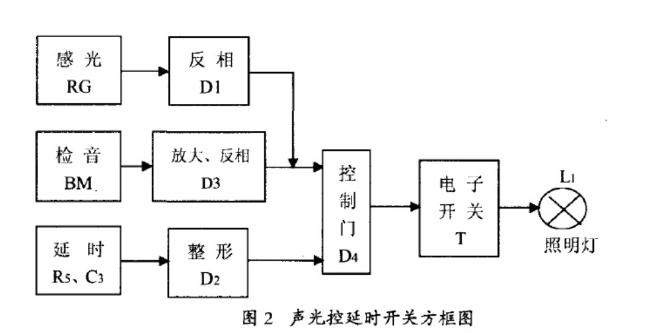

0 聲光控制延時(shí)開(kāi)關(guān)主要由聲控開(kāi)關(guān)、光控開(kāi)關(guān)、延時(shí)電路幾部分組成。聲控是通過(guò)柱極體話筒采集聲音,并產(chǎn)生脈沖信號(hào)。光控電路則是由光敏電阻控制,光敏電阻在有光和無(wú)光狀態(tài)下電阻阻值差距很大,能產(chǎn)生高低

2023-07-05 10:34:58 1409

1409

如何使RC延時(shí)電路無(wú)延時(shí)呢? RC延時(shí)電路是一種常見(jiàn)的電子電路,用于在電路中引入一個(gè)可控的時(shí)間延遲。然而,有時(shí)候我們可能需要使RC延時(shí)電路無(wú)延時(shí),即輸出信號(hào)與輸入信號(hào)幾乎同時(shí)出現(xiàn)。以下是一些方法來(lái)

2023-11-20 17:05:33 402

402

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論