LUT中文名字叫查找表。以7系列的FPGA為例,每一個(gè)Slice里面有四個(gè)LUT。FPGA就是通過LUT實(shí)現(xiàn)大量的組合邏輯,以及SLICEM里面的LUT還可以構(gòu)成RAM,Shift Register,以及Multiplexers。這篇文章我們一起來學(xué)習(xí)LUT如何構(gòu)成組合邏輯。

2023-03-13 10:28:06 2053

2053 在選擇FPGA時(shí),關(guān)注LUT(Look-Up Table)和BRAM(Block RAM)是非常重要的,因?yàn)樗鼈兪?b class="flag-6" style="color: red">FPGA架構(gòu)中的兩個(gè)核心資源,對(duì)于設(shè)計(jì)的性能和資源利用至關(guān)重要。

2023-11-21 15:03:06 548

548

,能夠存儲(chǔ)16bit數(shù)據(jù),這也是LUT能被用于組建分布式RAM的原因。如果要構(gòu)成一個(gè)6輸入1輸出MUX,可以通過兩片4輸入查找表級(jí)聯(lián),也可直接用一片完整的6輸入查找表,兩片4輸入的查找表的存儲(chǔ)容量

2018-07-30 18:11:19

;MEM [15] = 8'hf;結(jié)束永遠(yuǎn)@(posedge clk1) if(mem_we)開始 MEM [mem_waddr [3:0]]正如您所看到的,這是簡單而傳統(tǒng)的分布式RAM描述,具有全寬

2019-06-12 14:17:08

我打算在Virtex7器件中使用分布式RAM作為單端口RAM,用于我的濾波器設(shè)計(jì)。 RAM將初始配置,然后只有讀取將從RAM開始。我的讀地址生成來自CLK2,與寫時(shí)鐘CLK1異步。我可以像這樣

2019-04-16 09:52:29

您好!分布式RAM和Block RAM之間究竟有什么區(qū)別?兩者都只是芯片內(nèi)存,對(duì)吧?但我不知道兩者之間的區(qū)別。和..下一個(gè)問題.. isaboutMUX ..根據(jù)7系列概述,7系列FPGA支持全范圍

2020-07-19 06:37:51

喜我是這個(gè)社區(qū)的新手,所以如果這種話題不符合該部分或者我濫用論壇,我會(huì)提前道歉。我有一個(gè)項(xiàng)目,我需要實(shí)例化2000個(gè)分布式rams,由2000個(gè)數(shù)據(jù)文件初始化。問題是,當(dāng)我嘗試使用iSim模擬我

2019-03-12 13:01:59

大家好 ...我在實(shí)現(xiàn)大小為65535 * 3的分布式RAM時(shí)出現(xiàn)問題,在大約2小時(shí)內(nèi)合成時(shí)發(fā)生了很大的延遲并且沒有停止,對(duì)這個(gè)問題有什么解釋嗎?提前致謝以上來自于谷歌翻譯以下為原文Hello

2019-06-25 11:03:45

搭建分布式Hadoop

2019-05-22 13:11:34

分布式MySQL——InnoDB cluster和性能測試

2020-04-15 08:43:00

作為更為貼近人民日常生活的分布式光伏發(fā)電與光伏地面電站相比,其安全性如何呢?請(qǐng)看南京研旭在本文內(nèi)的具體介紹。 從使用的角度,分布式光伏發(fā)電特有的優(yōu)點(diǎn):1、分布式光伏發(fā)電可實(shí)現(xiàn)就近供電,不必長距離輸送

2018-10-12 15:35:24

1.引入分布式電源前后的網(wǎng)損模型的建立。2.仿真分析DG接入對(duì)變壓器運(yùn)行臺(tái)數(shù)及網(wǎng)損的影響;變壓器電阻對(duì)網(wǎng)損的影響。3.仿真分析DG接入位置對(duì)網(wǎng)損的影響;DG容量對(duì)網(wǎng)損的影響;DG運(yùn)行方式對(duì)網(wǎng)損的影響。

2015-04-19 10:24:25

幾種分布式發(fā)電簡介2.分布式發(fā)電與配電網(wǎng)互聯(lián)問題3.微型電網(wǎng)技術(shù)4.分布式發(fā)電(電源)技術(shù)應(yīng)用的障礙和瓶頸5.分布式發(fā)電(電源)技術(shù)發(fā)展方向6.結(jié)語

2011-03-11 13:37:39

發(fā)生干涉,干涉光反射回來以后,反向散射的干涉光回到信號(hào)處理裝置,同時(shí)將光纖沿線振動(dòng)聲波信號(hào)帶來信號(hào)處理裝置。由于光速保持不變,因此可得到每米光纖的聲波振動(dòng)的測量結(jié)果。3、分布式光纖聲波傳感系統(tǒng)(DAS

2018-11-09 11:48:17

分布式聲波傳感系統(tǒng)DAS

2020-12-21 07:48:43

分布式數(shù)據(jù)庫系統(tǒng)(DDBS)是數(shù)據(jù)庫技術(shù)和網(wǎng)絡(luò)技術(shù)兩者相互滲透和有機(jī)結(jié)合的結(jié)果。涉及數(shù)據(jù)庫基本理論和網(wǎng)絡(luò)通信理論。分布式數(shù)據(jù)庫由一組數(shù)據(jù)組成,這些數(shù)據(jù)在物理上分布在計(jì)算機(jī)網(wǎng)絡(luò)的不同節(jié)點(diǎn)上,邏輯上是屬于同一個(gè)系統(tǒng)。

2019-09-24 09:13:39

分布式電源分布式電源裝置是指與環(huán)境兼容的獨(dú)立電源,功率為數(shù)千瓦與環(huán)境兼容。這些電源由電力部門、電力用戶或第3方所有,用以滿足電力系統(tǒng)和用戶特定的要求。例如,對(duì)偏遠(yuǎn)地區(qū)的用戶或商業(yè)地區(qū)、居民地

2021-12-29 06:51:27

(1)含分布式電源的配電網(wǎng)日前兩階段優(yōu)化調(diào)度模型,EI,如圖 1—3matlab源代碼,高水平文章,保證正確,可先發(fā)您文章看是否滿足您的要求在電力市場環(huán)境下,供電公司通過對(duì)接入配電網(wǎng)的分布式電源

2021-12-29 06:33:33

當(dāng)討論分布式系統(tǒng)時(shí),我們面臨許多以下這些形容詞所描述的 同類型: 分布式的、刪絡(luò)的、并行的、并發(fā)的和分散的。分布式處理是一個(gè)相對(duì)較新的領(lǐng)域,所以還沒有‘致的定義。與順序計(jì)算相比、并行的、并發(fā)的和分布式的計(jì)算包括多個(gè)PE問的集體協(xié)同動(dòng)作。這些術(shù)語在范圍一卜相互覆蓋,有時(shí)也交換使用。

2020-03-31 09:01:18

在分布式系統(tǒng)中,共同噪聲源是相關(guān)的,而分布式噪聲源如果不相關(guān),在RF信號(hào)組合時(shí)就會(huì)降低。對(duì)于系統(tǒng)中的大部分組件,這都可以非常直觀地加以評(píng)估。對(duì)于鎖相環(huán),環(huán)路中的每個(gè)組件都有與之相關(guān)聯(lián)的噪聲傳遞函數(shù)

2019-08-02 08:35:04

提供更好的服務(wù)體驗(yàn)。

圖 3 鴻蒙硬件資源池支持各類消費(fèi)者場景

2.2 開發(fā)者場景

對(duì)于開發(fā)者來說,由于分布式硬件資源池將跨設(shè)備硬件調(diào)用的復(fù)雜度都封裝在了系統(tǒng)底層,跨設(shè)備硬件復(fù)用本地硬件的 API

2023-12-06 10:02:45

的電力系統(tǒng)LocalEPS1、2、3與區(qū)域的電力系統(tǒng)AreaElectricPowerSystem(AreaEPS)互聯(lián)。局部電力系統(tǒng)1是負(fù)荷通過PCC直接受電的地方電力系統(tǒng);局部電力系統(tǒng)2是分布式電源通過

2011-06-13 14:25:10

: 1、分布式數(shù)據(jù),但只有一個(gè)總? 據(jù)庫,沒有局部數(shù)據(jù)庫。 2、分層式處理,每一層都有自己的數(shù)據(jù)庫。 3、充分分散的分布式網(wǎng)絡(luò),沒有中央控制部分,各節(jié)點(diǎn)之間的聯(lián)接方式又可以有多種,如松散的聯(lián)接,緊密

2009-07-22 14:53:12

現(xiàn)實(shí)中多設(shè)備間通信方式多種多樣(WIFI、藍(lán)牙等),不同的通信方式使用差異大,導(dǎo)致通信問題多;同時(shí)還面臨設(shè)備間通信鏈路的融合共享和沖突無法處理等挑戰(zhàn)。那么分布式軟總線實(shí)現(xiàn)近場設(shè)備間統(tǒng)一的分布式通信管理能力如何呢?分布式軟總線組件架構(gòu)圖

2022-03-16 11:03:13

出現(xiàn)因時(shí)鐘精度不一樣而導(dǎo)致時(shí)鐘不同步。時(shí)鐘不一致就可能導(dǎo)致兩端收發(fā)節(jié)奏不一致,容易產(chǎn)生丟包。這時(shí),在多設(shè)備之間構(gòu)建一套分布式軟時(shí)鐘就非常重要了,它能讓由超級(jí)終端里的多個(gè)設(shè)備保持節(jié)奏一致。2. 空口資源

2021-11-09 17:24:38

的時(shí)鐘。而每個(gè)設(shè)備有自己的時(shí)鐘,其精度由其本機(jī)所帶晶振決定,就會(huì)非常容易出現(xiàn)因時(shí)鐘精度不一樣而導(dǎo)致時(shí)鐘不同步。時(shí)鐘不一致就可能導(dǎo)致兩端收發(fā)節(jié)奏不一致,容易產(chǎn)生丟包。這時(shí),在多設(shè)備之間構(gòu)建一套分布式軟時(shí)鐘

2021-11-23 16:58:46

對(duì)HarmonyOS分布式應(yīng)用測試解決方案,具體方案介紹如下。二、分布式應(yīng)用測試解決方案DevEco Testing是一款全新的HarmonyOS測試解決方案。如圖2所示,是DevEco Testing測試能力

2021-12-13 14:55:05

游戲任務(wù)進(jìn)行了切分,在手機(jī)端僅運(yùn)行游戲邏輯及部分簡單的2D UI渲染任務(wù),而將需要消耗大量資源的、復(fù)雜的3D渲染任務(wù)通過分布式技術(shù)卸載到PC或者筆記本上執(zhí)行,這樣對(duì)游戲任務(wù)進(jìn)行切分后,手機(jī)的負(fù)載變輕

2021-11-23 17:06:24

簡單的2D UI渲染任務(wù),而將需要消耗大量資源的、復(fù)雜的3D渲染任務(wù)通過分布式技術(shù)卸載到PC或者筆記本上執(zhí)行,這樣對(duì)游戲任務(wù)進(jìn)行切分后,手機(jī)的負(fù)載變輕,重負(fù)載任務(wù)分配在高算力設(shè)備運(yùn)行,不僅合理的利用

2021-11-15 14:54:29

設(shè)備、分布式的能力及應(yīng)用,二者具有無限能力。從開發(fā)者角度看,HarmonyOS上基本的組件分為3+1,其中3代表三個(gè)Ability,分別是:PageAbility:負(fù)責(zé)用戶界面的顯示

2021-11-22 15:15:05

什么 如何創(chuàng)建一個(gè)HarmonyOSDemo Project 如何構(gòu)建一個(gè)HAP并且將其部署到智慧屏真機(jī) 通過此示例應(yīng)用體驗(yàn)如何使用分布式任務(wù)調(diào)度2. 您需要什么硬件要求 操作系統(tǒng):Windows1064位

2020-09-18 09:21:25

設(shè)計(jì)理念HarmonyOS 是面向未來全場景智慧生活方式的分布式操作系統(tǒng)。對(duì)消費(fèi)者而言,HarmonyOS 將生活場景中的各類終端進(jìn)行能力整合,形成“One Super Device”,以實(shí)現(xiàn)

2020-09-22 17:11:07

估算電源壽命是一種辦法,和傳統(tǒng)開關(guān)電源長期實(shí)戰(zhàn)技術(shù)積累還是有些差距!分布式恒流也有它缺點(diǎn),開始會(huì)增加部分設(shè)計(jì)成本,產(chǎn)品設(shè)計(jì)品質(zhì)與線路設(shè)計(jì)選擇需要權(quán)衡。可能成本增加是短暫的,表面的,應(yīng)該綜合考量。 2

2011-03-09 16:47:54

的“超級(jí)終端”。分布式硬件技術(shù)能夠?yàn)殚_發(fā)者的上述需求提供助力,因其能夠構(gòu)建硬件資源池,提供按需定義超級(jí)終端硬件的能力,支持多路硬件的協(xié)同和調(diào)度,且能夠使硬件能力自適應(yīng)。

分布式硬件能夠帶來什么樣

2023-08-24 17:25:23

Quartus II 中定制的RAM是分布式的還是塊的

2014-03-10 17:51:45

基于反射內(nèi)存實(shí)時(shí)局域網(wǎng)的特點(diǎn)是什么?基于反射內(nèi)存卡實(shí)時(shí)局域網(wǎng)的實(shí)現(xiàn)機(jī)制RTX在分布式實(shí)時(shí)仿真系統(tǒng)中的應(yīng)用

2021-05-19 06:46:01

本帖最后由 lpc2292 于 2013-2-27 20:24 編輯

“部分 I: 用 Spartan-3 系列 FPGA 進(jìn)行設(shè)計(jì)”第 1 章 “概述”第 2 章 “使用全局時(shí)鐘資源”第 3

2013-02-27 20:20:10

TSP分布式控制有什么優(yōu)勢?TSP分布式控制提高了測試速度并且降低了測試成本。

2021-05-12 06:19:56

Vivado綜合可以理解多種多樣的RAM編寫方式,將其映射到分布式RAM或塊RAM中。兩種實(shí)現(xiàn)方法在向RAM寫入數(shù)據(jù)時(shí)都是采取同步方式,區(qū)別在于從RAM讀取數(shù)據(jù)時(shí),分布式RAM采用異步方式,塊RAM

2020-09-29 09:40:40

docker安裝分布式zabbix

2019-10-24 07:33:40

基于labview的分布式壓力采集系統(tǒng),用于假肢接受腔內(nèi)部接觸面的壓力測量,選擇哪種壓力傳感器和采集卡比較合適,求推薦。

2015-05-19 14:31:25

本篇分享一個(gè)使用hanlp分詞的操作小案例,即在spark集群中使用hanlp完成分布式分詞的操作,文章整理自【qq_33872191】的博客,感謝分享!以下為全文: 分兩步:第一步:實(shí)現(xiàn)

2019-01-21 10:45:23

《無線通信FPGA設(shè)計(jì)》分布式FIR的并行改寫,結(jié)果與matlab仿真結(jié)果基本吻合

2017-02-26 09:09:47

之前我們分享過分布式軟總線和分布式數(shù)據(jù)管理,今天主要說一下OpenHarmony的分布式任務(wù)調(diào)度,分布式任務(wù)調(diào)度是建立在分布式軟總線和分布式數(shù)據(jù)管理基礎(chǔ)之上,目標(biāo)是為了構(gòu)建統(tǒng)一的分布式服務(wù)管理(發(fā)現(xiàn)

2022-07-18 17:06:45

.設(shè)計(jì)OpenHarmony技術(shù)特性eTS UI分布式調(diào)度分布式數(shù)據(jù)管理3.支持OpenHarmony版本OpenHarmony 3.0 LTS 、OpenHarmony 3.1 Beta4.支持開發(fā)板潤

2022-07-29 14:17:34

優(yōu)秀的算法和實(shí)現(xiàn)為HarmonyOS構(gòu)建出一套高性能的分布式通信。如圖2所示,HarmonyOS分布式軟總線從邏輯架構(gòu)上將分布式通信抽象為由四個(gè)部分組成的業(yè)務(wù)模型:發(fā)現(xiàn)、連接、組網(wǎng)和傳輸。這四個(gè)部分

2022-01-06 11:32:11

有讀取和/或?qū)懭霐?shù)據(jù)總線。 寫入RAM通常是同步完成的。閱讀通常是同步進(jìn)行的,但有時(shí)可以異步進(jìn)行。 Blockram與分布式RAM現(xiàn)在,FPGA中有兩種內(nèi)部RAM:Blockrams和分布式RAM。通常

2020-09-10 11:11:57

操作系統(tǒng)-----分布式系統(tǒng)概述

2019-07-25 06:59:49

(ROF)系統(tǒng)的分布式天線網(wǎng)絡(luò)將在2G/3G/4G/WLAN四網(wǎng)融合的接入中發(fā)揮極其重要的作用。ROF分布式天線網(wǎng)絡(luò)的一般結(jié)構(gòu)如圖1所示。利用模擬直調(diào)光模塊將射頻信號(hào)調(diào)制到光載波上,經(jīng)過光纖傳輸至遠(yuǎn)端天線

2019-06-11 07:45:30

大家好,我正在嘗試用VHDL中的初始值實(shí)現(xiàn)分布式RAM。我的目標(biāo)是Virtex-5- 某處有一個(gè)例子嗎?我知道有些Virtex組件確實(shí)有一個(gè)可以使用泛型傳遞的初始值 - 我應(yīng)該將它與全局重置或其他

2019-02-26 11:15:14

特性(主要包括電壓V、電流I、有功P、無功Q)不同,需要的建模方式也有所不同。1.常見的

分布式電源

2.

分布式電源建模燃料電池是電力電子變換器接口型的潮流計(jì)算模型,它在潮流計(jì)算里面可以使用pq,pq節(jié)點(diǎn)來進(jìn)行處理。是嗎?是pq嗎?不是的是pv節(jié)點(diǎn),那么它為什么是pv節(jié)點(diǎn)呢?因?yàn)樗敵龅闹绷麟妷菏?/div>

2021-07-12 07:54:19

您好,我正在Virtex7上實(shí)現(xiàn)(127x8)即(深度x寬度)內(nèi)存。我有以下問題1.使用速度,效率和功率使用的分布式ram或block ram interms來實(shí)現(xiàn)它是否可行。2.他們使用分布式

2020-03-23 07:17:45

你好在7系列和超級(jí)FPGA器件中,可以回讀捕獲的任何寄存器數(shù)據(jù)嗎?例如:CLB寄存器,Blcok RAM寄存器,SRL,分布式RAM

2020-08-21 10:59:02

。塊RAM(BRAM),容量較大,數(shù)量少,速度較快。分布式RAM:容量小,數(shù)量多,速度不如BRAm快。一般使用方法和接口是一樣的。

2018-08-23 09:14:59

一、查找表LUT就是查找表,對(duì)于4輸入的LUT而言,實(shí)際上就是4位地址位,一位數(shù)據(jù)位的存儲(chǔ)器,能夠存儲(chǔ)16位數(shù)據(jù),所以我們在FPGA設(shè)計(jì)中可以用LUT組建分布式的RAM。這樣也可以解釋我們在設(shè)計(jì)中

2021-07-28 08:42:17

在構(gòu)建分布式嵌入式系統(tǒng)的過程中利用Jini技術(shù),不但可以降低系統(tǒng)的開發(fā)難度、實(shí)現(xiàn)嵌入式環(huán)境中基于服務(wù)級(jí)的互操作,而且可使系統(tǒng)具有很好的靈活性和可靠性。

2021-04-28 06:46:33

一種基于ZigBee和ModBus的分布式電子警察系統(tǒng)設(shè)計(jì)

2021-05-31 06:24:15

華杰智控Profinet遠(yuǎn)程分布式IO模塊上有一個(gè)modbus互轉(zhuǎn)Profinet網(wǎng)關(guān), 有什么作用?多個(gè)Profinet遠(yuǎn)程分布式IO模塊能否共用一個(gè)GSD文件?

2021-09-27 08:45:14

使用 Jmeter 進(jìn)行分布式測試;檢索日志

2023-05-10 13:00:46

的選擇無線分布式采集來進(jìn)行。現(xiàn)有的無線分布式采集系統(tǒng)中,往往使用單片機(jī)、DSP等作為系統(tǒng)的主控控制單元。但是由于其自身工作特點(diǎn),往往對(duì)于精確的定時(shí)控制以及并行處理能力上比FPGA弱。

2019-10-14 07:10:38

分布式計(jì)算技術(shù)是什么?如何去實(shí)現(xiàn)一種分布式計(jì)算技術(shù)?

2021-09-24 07:52:34

分布式車身控制系統(tǒng)的結(jié)構(gòu)是怎樣構(gòu)成的?分布式車身控制系統(tǒng)有哪些功能?

2021-05-13 07:03:30

什么是分布式天線系統(tǒng)?如何對(duì)分布式天線系統(tǒng)(DAS)進(jìn)行優(yōu)化?

2021-05-24 06:03:56

嗨,我正在瀏覽Vritex 6原始手冊。我很想知道LUT是否可以同時(shí)配置為SRL / CFGLUT5和DRAM(分布式RAM)(不同的配置將用于不同的周期)?如果沒有,為什么?如果是這樣,怎么樣?非常感謝你,

2020-06-18 08:29:16

什么是分布式干擾系統(tǒng)?分布式干擾系統(tǒng)是一種綜合化、一體化、小型化、網(wǎng)絡(luò)化和智能化系統(tǒng),是將眾多體積小,重量輕,廉價(jià)的小功率偵察干擾機(jī)裝置在易于投放的小型平臺(tái)上,撒布在接近***擾目標(biāo)空域地,通過指令

2019-08-08 06:57:44

FIR濾波器的原理及結(jié)構(gòu)是什么基于分布式算法的FIR濾波器的實(shí)現(xiàn)

2021-05-08 08:39:41

對(duì)HarmonyOS分布式應(yīng)用測試解決方案,具體方案介紹如下。二、分布式應(yīng)用測試解決方案DevEco Testing是一款全新的HarmonyOS測試解決方案。如圖2所示,是DevEco Testing測試能力

2021-12-13 18:07:58

大家好,我無法合成LUT RAM(16深48位寬),而RAM則由寄存器構(gòu)建。經(jīng)過實(shí)驗(yàn),我發(fā)現(xiàn)我可以通過注釋掉一些代碼來獲得LUT RAM綜合,以幫助模擬。在代碼中我有兩個(gè)塊,一個(gè)用于模擬,一個(gè)用于

2019-02-15 11:42:25

有效避免大型輸電網(wǎng)出現(xiàn)的故障影響范圍較大的問題。 2. 節(jié)約能源:分布式電源通常利用可再生能源,如太陽能、風(fēng)能、生物質(zhì)能等,可以節(jié)約能源,減少對(duì)化石能源的依賴。 3. 降低電網(wǎng)的負(fù)荷:分布式電源設(shè)備

2023-04-10 16:28:30

嗨,我正在xilinx virtex7上使用分布式RAM實(shí)現(xiàn)((深度)128x(寬度)8)位存儲(chǔ)器結(jié)構(gòu)。從理論上講,它應(yīng)該占用128x8 = 1024; 1024年至1064年= 16; 16/4

2020-04-06 07:19:30

想知道怎么入門DevEco Studio 分布式跨設(shè)備應(yīng)用開發(fā)?

2020-09-18 15:50:30

BST材料的特性是什么?怎樣去設(shè)計(jì)分布式電容共面波導(dǎo)結(jié)構(gòu)式移相器?

2021-06-08 06:55:30

小容量分布式光伏電站信息采集系統(tǒng)是由哪些部分組成的?怎樣去設(shè)計(jì)一種小容量分布式光伏電站信息采集系統(tǒng)?

2021-10-22 06:22:39

分布式發(fā)電的快速發(fā)展奠定了堅(jiān)實(shí)的基礎(chǔ)。 分布式光伏發(fā)電近3年呈現(xiàn)爆發(fā)式增長。我國從2009年開始實(shí)施特許權(quán)招標(biāo),推動(dòng)地面大型光伏電站建設(shè)。同年,開始了“金太陽”工程和光電建筑示范項(xiàng)目,給予分布式光伏

2014-04-22 14:38:48

FPGA 輸入輸出模塊圖7: 顯示 Sparatan2 FPGA 輸入/輸出細(xì)節(jié)的框圖分布式塊 RAM分布式塊 RAM 的概念主要存在于 Xilinx 設(shè)備中。Xilinx 設(shè)備的大多數(shù) clb 都

2022-04-03 11:20:18

分布式的濾波器算法是什么?一種基于FPGA分布式算法的濾波器設(shè)計(jì)實(shí)現(xiàn)

2021-04-29 07:13:23

視圖,API接口簡單,與拓?fù)洌瑒?dòng)態(tài)擴(kuò)展或故障恢復(fù)無關(guān),無需手動(dòng)配置,自動(dòng)選擇備份節(jié)點(diǎn),大多數(shù)緩存系統(tǒng)提供圖形化管理控制臺(tái),簡單易用保持。分布式緩存優(yōu)勢1,提高數(shù)據(jù)讀取速度2,提高系統(tǒng)擴(kuò)展能力3,降低

2018-11-16 15:45:55

嗨!我有一個(gè)關(guān)于分布式RAM和Block RAM的問題。芯片中有menexternalmemory或內(nèi)存嗎?請(qǐng)?jiān)敿?xì)告訴我。謝謝!

2019-11-07 09:07:16

一個(gè)關(guān)于分布式RAM時(shí)序的問題。你可以看到Attchments。在藍(lán)線中,如果CLK將0更改為1. AI / BI / CI / DI將被復(fù)制到輸出。在這種情況下,藍(lán)色十字架的意思是什么?我不知道它

2019-11-07 09:31:52

怎么設(shè)計(jì)一種分布式無線測控系統(tǒng)?無線測控網(wǎng)絡(luò)系統(tǒng)具有哪些優(yōu)點(diǎn)及應(yīng)用?

2021-04-13 06:29:32

電源,然后經(jīng)過板上電源模塊轉(zhuǎn)換到各個(gè)目標(biāo)電源進(jìn)行使用,電源架構(gòu)一般有集中式電源架構(gòu)和分布式電源架構(gòu)。1、集中式電源架構(gòu)即輸入電壓直接通過隔離DCDC模塊轉(zhuǎn)換到各個(gè)目標(biāo)電壓,但成本高,占用PCB面積大。2、分布式電源架構(gòu)輸入電源經(jīng)過隔離DCDC電源轉(zhuǎn)換到中間電源再經(jīng)過非隔離電源模塊轉(zhuǎn)換到最終目標(biāo)電壓

2021-11-15 07:11:43

在賽靈思Spartan-3、3E等系列的FPGA中,其邏輯單元CLB中一般含有不同數(shù)量的單端口RAM(SRAM)或者雙端口RAM(DRAM),這里的“單”或者“雙”是由我們開發(fā)人員定義的。

2017-02-11 13:56:11 6348

6348

前面簡要介紹了Spartan-3系列FPGA中分布式RAM的基本特性。為什么不從更高級(jí)的Virtex系列入手呢?我仔細(xì)看了一下各個(gè)系列的介紹、對(duì)比,Spartan系列基本就是Virtex系列的精簡版,其基本原理是一樣的,所以從簡單的入手來融會(huì)貫通未嘗不是一個(gè)好辦法。

2017-02-11 13:57:40 1176

1176

前面講了分布式RAM的方方面面,下面以RAM_16S為例,分別給出其在VHDL和Verilog HDL下面的模板代碼(在ISE Project Navigator中選擇 Edit---

2017-02-11 13:59:33 1323

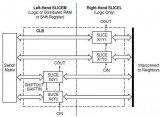

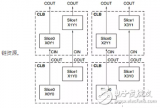

1323 CLB是xilinx基本邏輯單元,每個(gè)CLB包含兩個(gè)slices,每個(gè)slices由4個(gè)(A,B,C,D)6輸入LUT和8個(gè)寄存器組成。

2018-05-10 11:43:00 25053

25053

FPGA可以調(diào)用分布式RAM和塊RAM兩種RAM,當(dāng)我們編寫verilog代碼的時(shí)候如果合理的編寫就可以使我們想要的RAM被綜合成BRAM(Block RAM)或者DRAM(Distributed

2020-12-30 16:27:52 9

9 舉一個(gè)簡單的例子,如果要實(shí)現(xiàn)一個(gè)6*1的mux可以用一個(gè)6輸入的LUT或者是2個(gè)4輸入的LUT來實(shí)現(xiàn),6輸入的LUT相當(dāng)于是6位地址線一位數(shù)據(jù)位,能夠存儲(chǔ)64bit的數(shù)據(jù),而采用兩個(gè)4輸入的LUT的話,它的總?cè)萘看笮?2位數(shù)據(jù)。

2022-05-13 16:33:28 3734

3734 已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論