FPGA和CPU一直是雷達信號處理不可分割的組成部分。傳統(tǒng)上FPGA用于前端處理,CPU用于后端處理。隨著雷達系統(tǒng)的處理能力越來越強,越來越復(fù)雜,對信息處理的需求也急劇增長。為此,FPGA不斷在提高處理

2013-12-24 17:28:40 10148

10148

.FPGA+DSP的導(dǎo)引頭信號處理結(jié)構(gòu)成為當(dāng)前以及未來一段時間的主流。FPGA和DSP處理器具有截然不同的架構(gòu),在一種器件上非常有效的算法.在另一種器件上可能效率會非常低。如果目標要求大量的并行處理或者最大

2019-08-30 06:31:29

1.FPGA功能設(shè)計上圖所示的是FPGA圖像處理基板的邏輯功能框圖,圖中左側(cè)是背板接頭,FPGA與背板接頭相連的信號主要包括8路3.125G高速數(shù)據(jù)通道、1路1.3G高速雙向數(shù)據(jù)通道、2路時鐘信號

2021-11-10 08:06:26

你好,我們想使用LCD引腳,在FPGA中獲得外部輸入信號。我們在https://forums.xilinx.com/t5/7-Series-FPGA

2020-08-05 07:12:16

FPGA數(shù)字信號處理實現(xiàn)原理及方法

2012-08-15 19:00:58

FPGA數(shù)字信號處理實現(xiàn)原理及方法

2012-08-19 13:37:35

各位大神,小弟這邊先謝過了,真的很急!目前我需要使用FPGA技術(shù)來處理一款1對時鐘LVDS信號和8對數(shù)據(jù)LVDS信號攝像頭模組,我這邊只能對并口信號和MIPI信號輸出的攝像頭模組進行測試調(diào)焦,對于LVDS信號的模組沒有相關(guān)技術(shù),請大神幫忙啊!!!非常感謝!!!可付報酬!!!

2014-07-17 16:40:58

摘要:主要討論了FPGA設(shè)計中毛刺信號產(chǎn)生的原因,分析總結(jié)了處理毛刺信號的幾種方法,通過對毛刺信號的處理可以提高芯片的穩(wěn)定性。隨著FPGA(Field Programmable Gate Array

2009-04-21 16:47:58

比較器將網(wǎng)線傳輸過來的差分信號轉(zhuǎn)為單端信號,該信號時鐘頻率為100M,電平標準能滿足FPGA的輸入電平標準,波形質(zhì)量尚可。單端信號直接連接到FPGA,現(xiàn)在如果想用FPGA直接采集,應(yīng)該怎么處理呢,是當(dāng)作異步信號直接打拍嗎,過采樣的話時鐘頻率不夠。時鐘恢復(fù)目前來不及實現(xiàn)。

2020-03-07 16:01:37

在使用AD8302的時候,芯片手冊上描述輸入信號為-60dBm~0dBm在50Ω的系統(tǒng)中,轉(zhuǎn)換過來就是223.61uV~632.46mV的電壓范圍。

請問下,1. 如何控制輸入信號在AD8302的要求范圍內(nèi)呢?

2.當(dāng)信號高于這個范圍呢,如2V,該如何處理呢?

2023-12-08 06:06:50

處理研究的內(nèi)容2.2 數(shù)字信號處理系統(tǒng)架構(gòu)分析2.3 基于FPGA的數(shù)字信號處理的相關(guān)問題2.3.1 基于FPGA的數(shù)字信號處理系統(tǒng)設(shè)計流程2.3.2 定點數(shù)與浮點數(shù)參考文獻第3章 數(shù)字信號處理中

2012-04-24 09:33:23

``實現(xiàn)本設(shè)計信號數(shù)據(jù)處理和控制所用的硬件結(jié)構(gòu)如附件圖1(所用FPGA為V5-LX50T):數(shù)據(jù)流:AD6644對30M中頻信號進行采樣,將14位量化信號輸入FPGA。FPGA對采樣信號做DDC處理

2012-05-28 16:32:43

DSP技術(shù)廣泛應(yīng)用于各個領(lǐng)域,但傳統(tǒng)的數(shù)字信號處理器由于以順序方式工作使得數(shù)據(jù)處理速度較低,且在功能重構(gòu)及應(yīng)用目標的修改方面缺乏靈活性。而使用具有并行處理特性的FPGA實現(xiàn)數(shù)字信號處理系統(tǒng),具有很強的實時性和靈活性,因此利用FPGA實現(xiàn)數(shù)字信號處理成為數(shù)字信號處理領(lǐng)域的一種新的趨勢。

2019-10-17 08:12:27

DSP是注重數(shù)據(jù)處理。算法很重要。FPGA主要是做邏輯電路.現(xiàn)在很多框架都是基于DSP和FPGA的組合平臺,DSP作算法,FPGA作邏輯時序!FPGA一樣可以做DSP(DSP就是數(shù)字信號處理英文縮寫

2021-07-28 09:16:02

基于FPGA的數(shù)字信號處理

2020-04-04 18:08:33

`積分商城兌換的禮品《基于FPGA的數(shù)字信號處理(第2版)》曬曬,:-)`

2016-03-28 23:53:15

FFT算法在數(shù)字信號處理中占有重要的地位,所以本文提出了用FPGA實現(xiàn)FFT的一種設(shè)計思想,給出了總體實現(xiàn)框圖:重點設(shè)計實現(xiàn)了FFT算法中的蝶形處理單元,采用了一種高效乘法器算法設(shè)計實現(xiàn)了蝶形處理單元中的旋轉(zhuǎn)因子乘法器,從而提高了蝶形處理器的運算速度,降低了運算復(fù)雜度。

2017-11-28 11:32:15

作者:李慧敏 0 引 言 在數(shù)字信號處理領(lǐng)域,濾波器無疑是個非常重要的環(huán)節(jié)。而在數(shù)字濾波器中,有限脈沖響應(yīng)(FIR)濾波器因為其線性相位的特點,應(yīng)用尤為廣泛。實際應(yīng)用中FIR濾波器分為常系數(shù)FIR

2019-07-30 07:22:48

您可以顯著提高無線系統(tǒng)中信號處理功能的性能。怎樣提高呢?有效方法是利用FPGA結(jié)構(gòu)的靈活性和目前受益于并行處理的FPGA架構(gòu)中的嵌入式DSP模塊。

2019-10-23 07:04:22

隨著現(xiàn)代通信技術(shù)的廣泛使用,通信企業(yè)問的競爭不斷加劇,為提升自身的競爭優(yōu)勢,通信企業(yè)需要將其通信信號的質(zhì)量提升,并提高通信系統(tǒng)各項指標的穩(wěn)定性、安全性、高效性。在音頻信號處理方法及FPGA實現(xiàn)中

2020-10-21 16:42:15

最近做一個項目,用cpld采集方位信號處理,經(jīng)過一段時間運行后發(fā)現(xiàn),系統(tǒng)不是很穩(wěn)定,會時不時的出現(xiàn)方位不穩(wěn)的現(xiàn)象。后來經(jīng)過查閱代碼,發(fā)現(xiàn)沒有對方位信號做同步處理,導(dǎo)致時不時的亞穩(wěn)態(tài)出現(xiàn)。最后對采集的方位信號做兩級同步后問題完美解決,所以說一定要對輸入信號做同步后再使用。

2016-03-04 21:02:56

,生命周期縮短。實現(xiàn)功能強、性能指標高、抗干擾能力強、工作穩(wěn)定可靠、體積小、功耗低、結(jié)構(gòu)緊湊合理符合彈載要求的導(dǎo)引頭信號處理器已經(jīng)勢在必行。過去單一采用DSP處理器搭建信號處理器已經(jīng)不能滿足要求.FPGA+DSP的導(dǎo)引頭信號處理結(jié)構(gòu)成為當(dāng)前以及未來一段時間的主流。

2019-08-19 06:38:12

本文介紹的基于可編程門陣列( FPGA) 實現(xiàn)的沖擊信號處理芯片,能在飛行器飛行過程中,實時完成對三路沖擊信號的分析和處理,將沖擊信號的處理結(jié)果代替沖擊波的原始測量數(shù)據(jù)傳到地面,利用沖擊信號

2021-05-26 06:28:43

FPGA正在掀起一場數(shù)字信號處理的變革。本書旨在講解前端數(shù)字信號處理算法的高效實現(xiàn)。首先概述了當(dāng)前的FPGA技術(shù)、器件以及用于設(shè)計最先進DSP系統(tǒng)的工具。第1章的案例研究是40多個設(shè)計示例

2023-09-19 06:38:28

數(shù)字信號處理的FPGA實現(xiàn)

2019-12-31 17:24:40

數(shù)字信號處理的FPGA實現(xiàn)

2020-04-06 11:20:46

數(shù)字信號處理的FPGA實現(xiàn),還有個大的,上傳不了,要的M

2013-03-15 17:26:53

您好:由于最近我們要開發(fā)彩超中的后端彩色多普勒信號處理系統(tǒng),現(xiàn)在對應(yīng)用于醫(yī)療成像的DSP器件也有一定的了解,也仔細看了貴公司提供的醫(yī)療應(yīng)用解決方案中推薦的DSP,但是,介于我們這邊具體的系統(tǒng)要求

2020-06-15 13:32:45

和發(fā)送數(shù)據(jù),處理異步信號,以及為帶門控時鐘的低功耗ASIC進行原型驗證。 這里以及后面章節(jié)提到的時鐘域,是指一組邏輯,這組邏輯中的所有同步單元(觸發(fā)器、同步RAM塊以及流水乘法器等)都使用同一個網(wǎng)絡(luò)

2022-10-14 15:43:00

我做的一個基于DSP的系統(tǒng)中,DSP做主處理器,控制著整個系統(tǒng),包括信號處理,整體調(diào)度等;選擇了一塊Xilinx的FPGA做FIFO UART和系統(tǒng)的邏輯控制和譯碼。DSP的時鐘輸入為15MHz

2023-06-19 06:43:17

本帖最后由 upmcu 于 2012-7-28 15:07 編輯

截圖:FPGA控制實現(xiàn)圖像系統(tǒng)視頻圖像采集.pdfFPGA在多制式視頻轉(zhuǎn)換系統(tǒng)中的應(yīng)用.pdfFPGA在圖象處理中

2012-07-28 14:28:52

根據(jù)電力監(jiān)控系統(tǒng)的要求,提出一種基于FPGA技術(shù)的多路交流信號采集與處理系統(tǒng)的設(shè)計方法。分析整個系統(tǒng)的結(jié)構(gòu),并討論FPGA內(nèi)部硬件資源的劃分和軟件的設(shè)計方案,以及各個功能

2009-05-16 14:47:58 27

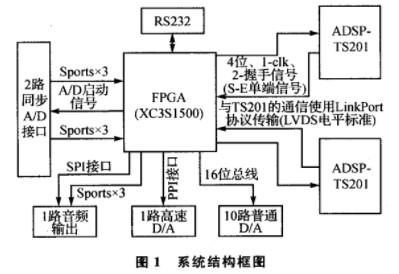

27 設(shè)計了一種基于FPGA 和DSP 的光纖信號實時處理系統(tǒng),介紹了系統(tǒng)的硬件組成和工作原理。該系統(tǒng)采用FPGA 實現(xiàn)數(shù)據(jù)的高速采集和邏輯控制,用DSP 實現(xiàn)傳感信號的全數(shù)字解調(diào),分析了載

2009-06-19 11:17:43 24

24 簡要分析了DSP+FPGA系統(tǒng)的特點和優(yōu)越性,并且結(jié)合一個實時信號處理板的開發(fā),提出在此類系統(tǒng)中,FPGA設(shè)計的幾個關(guān)鍵問題,并且給出了詳實的分析和解決方案。

2009-09-02 17:44:44 24

24 本文針對磁通門信號采集與處理的具體特點,對基于FPGA的磁通門數(shù)字信號處理系統(tǒng)進行了研究。該系統(tǒng)采用A/D轉(zhuǎn)換器對磁通門輸出信號進行采樣,采樣后的數(shù)據(jù)通過FPGA進行數(shù)據(jù)

2009-12-23 15:09:09 15

15 本文針對磁通門信號采集與處理的具體特點,對基于FPGA的磁通門數(shù)字信號處理系統(tǒng)進行了研究。該系統(tǒng)采用A/D轉(zhuǎn)換器對磁通門輸出信號進行采樣,采樣后的數(shù)據(jù)通過FPGA進行數(shù)據(jù)處理,再

2010-07-21 17:24:58 26

26 為了滿足超聲波探傷檢測的實時性需求,通過研究超聲波探傷的工作原理,提出了基于FPGA芯片的實時信號處理系統(tǒng)實現(xiàn)方案及硬件結(jié)構(gòu)設(shè)計,并根據(jù)FPGA邏輯結(jié)構(gòu)模型實現(xiàn)了軟件系統(tǒng)

2010-09-30 16:39:07 45

45 摘 要: 本文在闡述某種近距雷達目標檢測原理和FPGA技術(shù)發(fā)展狀況的基礎(chǔ)上,著重討論用FPGA設(shè)計高性能的數(shù)字信號處理系統(tǒng)的方法,并給出一個應(yīng)用實例。

2006-03-11 13:16:43 1698

1698

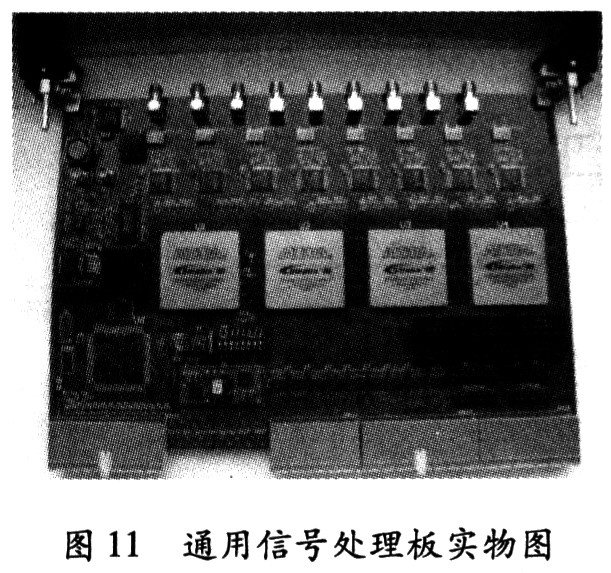

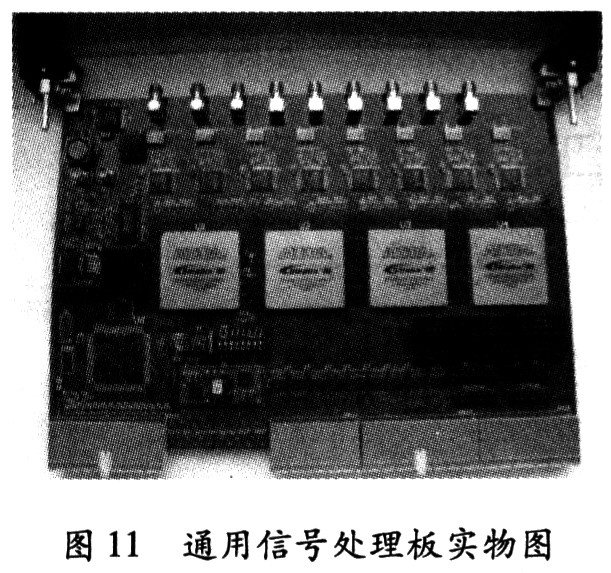

基于CPCI總線的通用FPGA信號處理板的設(shè)計

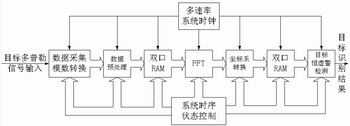

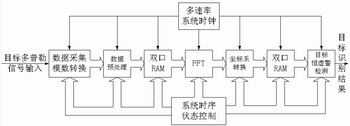

?隨著雷達信號處理技術(shù)的不斷發(fā)展以及現(xiàn)代國防對雷達技術(shù)的需求,系統(tǒng)對雷達信號處理的要求也越來越高,需要實時處

2009-11-28 15:07:38 922

922

基于DSP與FPGA的光柵地震檢波器的信號處理

0 引 言

在石油地震勘探中,地震儀通過地震檢波器采集信號。地震檢波器是為了接收和記錄地

2010-01-20 11:26:15 719

719

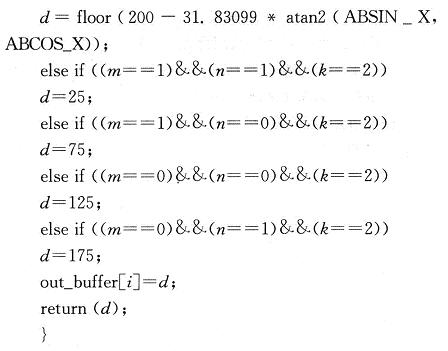

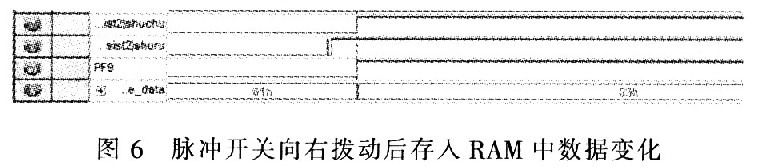

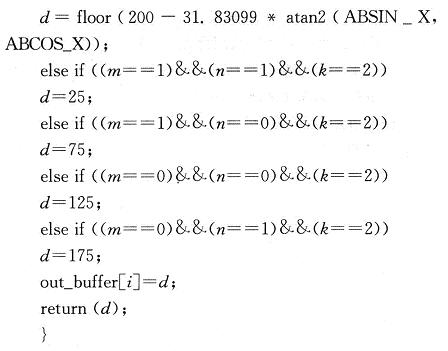

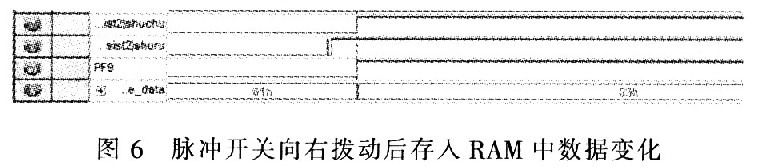

本系統(tǒng)設(shè)計利用FPGA間接控制2塊MAX4312選通所需要的視頻通道,實現(xiàn)各個視頻通道間相互切換。根據(jù)開關(guān)控制信號的設(shè)計思想在FPGA中對撥動開關(guān)輸入信號做去抖動處理,然后對不同的

2010-06-29 15:45:27 3378

3378

應(yīng)用領(lǐng)域: 6U VME TigerSHARC201FPGA信號處理機主要面向雷達、聲納、通信、圖象處理等高速信號處理領(lǐng)域。采用專用DSP與FPGA可編程邏輯器組成陣列化并行處理機,已經(jīng)越來越成為當(dāng)前數(shù)字信號處理發(fā)展的趨勢。 雷航科技的6U VME TigerSHARC201FPGA信號處理機就

2011-02-28 12:05:32 64

64 以FPGA 芯片為載體, 通過QuartusII 的LPM_ROM 模塊和VHDL 語言為核心設(shè)計一個多功能信號發(fā)生器,根據(jù)輸入信號的選擇可以輸出遞增鋸齒波、遞減鋸齒波、三角波、階梯波和方波等5 種信號,

2011-09-26 14:05:54 8050

8050

在3G移動通信網(wǎng)絡(luò)建設(shè)中,如何實現(xiàn)密集城區(qū)的無線網(wǎng)絡(luò)覆蓋是目前基站的發(fā)展方向。本文提出了基于FPGA的數(shù)字收發(fā)機信號處理。

2011-10-21 17:56:36 60

60 本文提出基于FPGA的數(shù)字收發(fā)機信號處理研究與實現(xiàn)

2011-11-01 18:20:42 50

50 本書共分8章,主要內(nèi)容包括典型fpga器件的介紹、vhdl硬件描述語言、fpga設(shè)計中常用軟件簡介、用fpga實現(xiàn)數(shù)字信號處理的數(shù)據(jù)規(guī)劃、多種結(jié)構(gòu)類型的fir數(shù)字濾波器的fpga實現(xiàn)、不同結(jié)構(gòu)

2011-11-04 15:50:12 0

0 提出一種基于FPGA的實時視頻信號處理平臺的設(shè)計方法,該系統(tǒng)接收低幀率數(shù)字YCbCr 視頻信號,對接收的視頻信號進行格式和彩色空間轉(zhuǎn)換、像素和,利用片外SDRAM存儲器作為幀緩存且通

2012-08-13 17:17:58 100

100 為了實現(xiàn)低成本的MEMS慣性測量組合應(yīng)用于現(xiàn)有應(yīng)用系統(tǒng)或測試系統(tǒng),提出了一種基于FPGA的MIMU信號處理技術(shù)方案,并完成系統(tǒng)的軟硬件設(shè)計。該系統(tǒng)實現(xiàn)了采集現(xiàn)有MIMU輸出的RS422數(shù)字信

2013-08-07 18:38:02 38

38 隨著新的FPGA體系的出現(xiàn),DSP IP核和工具數(shù)量的增加,采用可編程邏輯的DSP應(yīng)用繼續(xù)增加。FPGA器件能夠以高速、實時、低成本、高靈活性的優(yōu)點應(yīng)用于數(shù)字信號處理領(lǐng)域,它可以完全取代通用DSP芯片或作為通用DSP芯片的協(xié)處理器進行工作。

2015-02-02 14:11:36 8469

8469 基于FPGA的雷達信號處理系統(tǒng)設(shè)計的論文

2015-10-30 10:38:12 6

6 基于FPGA的心電信號處理研究與實現(xiàn)論文

2015-10-30 10:38:53 9

9 基于FPGA數(shù)字信號處理,本文主要探討了基于FPGA數(shù)字信號處理的實現(xiàn)

2015-10-30 10:39:38 30

30 本書比較全面地闡述了fpga在數(shù)字信號處理中的應(yīng)用問題。本書共分8章,主要內(nèi)容包括典型fpga器件的介紹、vhdl硬件描述語言、fpga設(shè)計中常用軟件簡介、用fpga實現(xiàn)數(shù)字信號處理的數(shù)據(jù)規(guī)劃、多種

2015-12-23 11:07:46 44

44 基于FPGA的超聲波無損檢測信號處理研究/

2016-01-04 15:26:58 0

0 本文主要研究如何利用FPGA實現(xiàn)FFl’算法,研制具有自主知識產(chǎn)權(quán)的FFT

信號處理器

2016-03-21 16:22:52 40

40 外文翻譯過來的,數(shù)字信號處理的FPGA實現(xiàn)中文版。

2016-05-04 16:04:24 0

0 基于FPGA的數(shù)字信號處理算法研究與高效實現(xiàn)

2016-08-29 23:20:56 39

39 基于FPGA數(shù)字信號處理

2016-12-14 22:08:25 20

20 數(shù)字信號處理的FPGA實現(xiàn)

2016-12-14 22:08:25 32

32 利用FPGA實現(xiàn)信號處理算法是一個難度頗高的應(yīng)用,不僅涉及到對信號處理算法、FPGA芯片和開發(fā)工具的學(xué)習(xí),還意味著要改變傳統(tǒng)利用軟件在DSP上實現(xiàn)算法的習(xí)慣,從面向硬件實現(xiàn)的算法設(shè)計、硬件實現(xiàn)、結(jié)構(gòu)優(yōu)化和算法驗證等多個方面進行深入學(xué)習(xí)。

2016-12-26 17:26:41 12

12 基于DSP_FPGA的LFMCW雷達測距信號處理系統(tǒng)設(shè)計_陳林軍

2017-03-19 19:07:17 4

4 基于FPGA的通用傳感器信號處理系統(tǒng)設(shè)計_李輝

2017-03-19 19:07:17 3

3 光柵計量技術(shù)在工業(yè)計量領(lǐng)域得到了飛速發(fā)展,其中光柵傳感器在線位移和角位移測量中得到廣泛應(yīng)用。對光柵信號進行處理有很多方法,如傳統(tǒng)電路、 單片機或者現(xiàn)場可編程門陣列(FPGA)等。隨著電子技術(shù)

2017-08-30 18:10:14 5

5 光纖陀螺信號處理電路中FPGA與DSP的接口方法研究

2017-10-20 08:40:25 2

2 基于Cortex_A8和FPGA的嵌入系統(tǒng)在雷達信號處理中的應(yīng)用

2017-10-26 08:27:50 3

3 多抽樣率的數(shù)字信號處理及其FPGA實現(xiàn)

2017-10-30 11:42:44 10

10 DSP技術(shù)廣泛應(yīng)用于各個領(lǐng)域,但傳統(tǒng)的數(shù)字信號處理器由于以順序方式工作使得數(shù)據(jù)處理速度較低,且在功能重構(gòu)及應(yīng)用目標的修改方面缺乏靈活性。而使用具有并行處理特性的FPGA實現(xiàn)數(shù)字信號處理系統(tǒng),具有很強

2017-10-31 10:37:23 0

0 針對信號處理數(shù)據(jù)量大、實時性要求高的特點,從實際應(yīng)用出發(fā),設(shè)計了以雙DSP+FPGA為核心的并行信號處理模塊。為了滿足不同的信號處理任務(wù)需求,FPGA可以靈活地選擇與不同的DSP組成不同的信號處理

2017-11-17 06:11:40 2373

2373

在振動信號采集和處理系統(tǒng)設(shè)計中,信號的處理時間與可靠性決定著系統(tǒng)應(yīng)用的可行性。本文設(shè)計了一種基于FPGA的振動信號采集處理系統(tǒng),該系統(tǒng)通過振動信號采集電路、抗混疊濾波電路、AD采樣電路將電荷信號轉(zhuǎn)化

2017-11-18 05:26:02 3148

3148

在FPGA中,隨著信號處理的層次加深,對信號進行乘、累加、濾波等運算后,可能輸入時僅為8位位寬的信號會擴展成幾十位位寬,位寬越寬,占用的硬件資源就越多,但位寬超過一定范圍后,位寬的增寬并不會對處理

2017-11-18 12:37:12 1786

1786

本文設(shè)計并在FPGA芯片中實現(xiàn)了數(shù)字音頻廣播系統(tǒng)的信號調(diào)制系統(tǒng)。信號調(diào)制系統(tǒng)位于整個數(shù)字音頻廣播系統(tǒng)基帶信號處理鏈的末端,是基帶數(shù)字信號處理的核心系統(tǒng)。根據(jù)Eureka147標準,信號調(diào)制系統(tǒng)需要

2017-11-22 15:25:01 3892

3892 現(xiàn)如今,賽靈思 FPGA 上采用低電壓差分信令 (LVDS) 輸入, 僅需一個電阻器和一個電容器就能實現(xiàn)模擬輸入信號的數(shù)字化 。 由于數(shù)百組 LVDS 輸入駐留在生成電流的賽靈思器件上,因此

2018-01-11 01:06:07 4940

4940

隨著實時數(shù)字信號處理技術(shù)的發(fā)展,ARM、DSP和FPGA體系結(jié)構(gòu)成為3G移動終端實現(xiàn)的主要方式。本文的設(shè)計通過ARM對目標及環(huán)境進行建模、運算,生成網(wǎng)絡(luò)協(xié)議仿真數(shù)據(jù)庫,應(yīng)用DSP進行數(shù)據(jù)調(diào)度、運算和處理,最后形成所需的調(diào)幅、調(diào)相、調(diào)頻等控制字,通過FPGA控制收發(fā)器芯片產(chǎn)生射頻模擬信號。

2018-04-26 16:26:00 1281

1281

針對聲學(xué)多普勒流速剖面儀的高速信號采集和處理對運算實時性與易升級的需求,提出一種基于現(xiàn)場可編程門陣列( FPGA)的軟硬件協(xié)同設(shè)計方法。闡述聲學(xué)多普勒剖面儀的測流原理,選擇FPGA作為單一的信號

2018-03-05 15:45:18 2

2 FPGA+DSP的數(shù)字硬件系統(tǒng)正好結(jié)合了兩者的優(yōu)點,兼顧了速度和靈活性。本文以導(dǎo)引頭信號處理系統(tǒng)為例說明FPGA+DSP系統(tǒng)中FPGA的關(guān)鍵技術(shù)。

2019-01-08 08:36:00 2449

2449

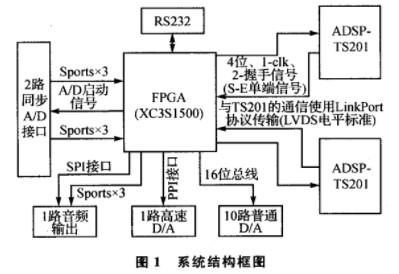

本系統(tǒng)以FPGA作為高性能實時信號處理系統(tǒng)的數(shù)據(jù)采集和控制中心,2片DSP為數(shù)據(jù)處理中心,主要包括4個功能模塊——數(shù)據(jù)采集模塊、FPGA數(shù)據(jù)控制模塊、DSP處理模塊和通信模塊,系統(tǒng)結(jié)構(gòu)框圖如圖1所示。

2019-04-23 08:29:00 3426

3426

高速中頻采樣信號處理平臺在實際應(yīng)用中有很大的前景,提出采用FPGA+DSP的處理結(jié)構(gòu),結(jié)合高性能A/D和D/A處理芯片,設(shè)計了一個通用處理平臺,并對其主要性能進行了測試。

2018-10-18 16:36:48 4637

4637

本文提出了一種實現(xiàn)信號采集方案,介紹了由ARM 處理器S3C2410 和EP2C8 FPGA 組成的高速信號采集系統(tǒng)的系統(tǒng)設(shè)計,并著重介紹前端硬件的設(shè)計,并就ARM 處理器和FPGA 的互聯(lián)設(shè)計進行探討。利用FPGA 硬件控制A/D 轉(zhuǎn)換,達到了較好的效果,實現(xiàn)了信號的采集與存儲。

2018-11-02 15:46:01 10

10 本文檔的主要內(nèi)容詳細介紹的是FPGA視頻教程之使用FPGA進行嵌入式信號處理系統(tǒng)設(shè)計視頻資料免費下載包括了:1、FPGA的最新發(fā)展現(xiàn)狀和設(shè)計流程;,2、基于FPGA的嵌入式系統(tǒng)技術(shù),3、基于FPGA

2019-03-29 16:53:50 15

15 本文通過GA3816、FPGA和DSP構(gòu)建了一個高速、通用、可擴展的多功能信號處理平臺,該信號處理平臺經(jīng)過動態(tài)配置GA3816處理芯片可實現(xiàn)一些信號處理領(lǐng)域常用的運算,也可以通過對DSP、FPGA芯片的編程來實現(xiàn)一些其它算法,所以該平臺能夠廣泛的應(yīng)用于信號處理等領(lǐng)域。

2021-05-22 15:29:05 1594

1594

多速率技術(shù)已廣泛應(yīng)用于數(shù)字音頻處理、語音處理、頻譜分析、無線通信、雷達等領(lǐng)域。作為一項常用信號處理技術(shù),FPGA攻城獅有必要了解如何應(yīng)用該技術(shù),解決實際系統(tǒng)中的多速率信號處理問題。 01什么是多速率

2021-06-01 11:02:19 2799

2799

基于FPGA的嵌入式信號處理系統(tǒng)設(shè)計方案

2021-06-02 11:04:33 0

0 基于FPGA的嵌入式信號處理系統(tǒng)設(shè)計方案

2021-06-02 11:04:33 0

0 數(shù)字信號處理的FPGA實現(xiàn).第3版英文

2021-10-18 10:55:32 0

0 說到異步時鐘域的信號處理,想必是一個FPGA設(shè)計中很關(guān)鍵的技術(shù),也是令很多工程師對FPGA望 而卻步的原因。但是異步信號的處理真的有那么神秘嗎?那么就讓特權(quán)同學(xué)和你一起慢慢解開這些所謂的難點

2021-11-01 16:24:39 11

11 基于FPGA+DSP彈載SAR信號處理系統(tǒng)設(shè)計

2021-12-27 18:58:51 21

21 FPGA和CPU一直是雷達信號處理不可分割的組成部分。傳統(tǒng)上FPGA用于前端處理,CPU用于后端處理。隨著雷達系統(tǒng)的處理能力越來越強,越來越復(fù)雜,對信息處理的需求也急劇增長。為此,FPGA不斷在提高處理

2022-12-14 11:46:09 1268

1268 ? ? ?由于信號在不同時鐘域之間傳輸,容易發(fā)生亞穩(wěn)態(tài)的問題導(dǎo)致,不同時鐘域之間得到的信號不同。處理亞穩(wěn)態(tài)常用打兩拍的處理方法。多時鐘域的處理方法很多,最有效的方法異步fifo,具體可以

2023-02-17 11:10:08 484

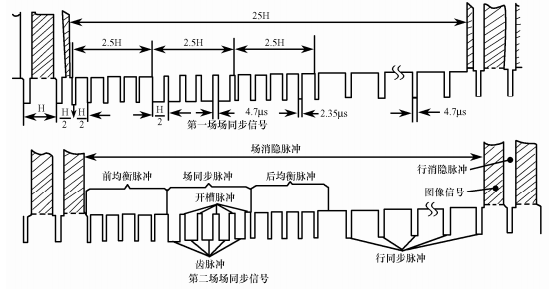

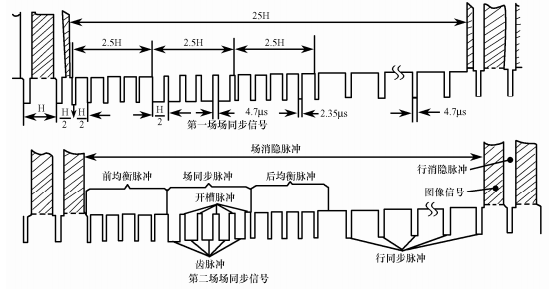

484 今天給大俠帶來基于FPGA的數(shù)字視頻信號處理器設(shè)計,由于篇幅較長,分三篇。 今天帶來第一篇,上篇,視頻信號概述和視頻信號處理的框架。 話不多說,上貨。

2023-05-19 10:56:17 953

953

一種基于FPGA 實現(xiàn)的800G信號處理平臺

2023-07-31 10:23:11 375

375

FPGA輸入的時鐘信號必須是方波么?正弦波會有影響么? FPGA是一種可編程邏輯器件,通常用于實現(xiàn)數(shù)字電路。輸入時鐘信號是FPGA中非常重要的時序信號,對整個系統(tǒng)的穩(wěn)定性和性能都有很大

2024-01-31 11:31:42 1244

1244

電子發(fā)燒友App

電子發(fā)燒友App

評論