賽靈思器件和工具支持從二進制到雙精度在內的多種數據類型。UltraScale ? 架構的可擴展精度提供極大靈活性,便于優化功耗和資源利用,同時滿足設計性能目標要求。

在數據中心、航空航天與軍用、5G 無線以及汽車等領域,客戶必須滿足高級駕駛員輔助 (ADAS)、雷達和深度學習等應用中嚴峻的散熱、功耗和成本要求。

要實現這些目標,一種極為有效的方法是用定點數實現信號處理鏈。賽靈思FPGA 和 SoC 具備固有的可變精度支持,允許客戶輕松調整以適應不斷演變的朝更低精度解決方案發展的這種行業趨勢。

賽靈思提供一種包含 Vivado? 高層次綜合 (HLS) 的工具流程,允許客戶方便地評估 C/C++ 設計的更低精度實現方案,諸如定點等。

簡介 :賽靈思支持的數據類型

賽靈思 All Programmable 器件和工具支持從二進制到雙精度浮點在內的多種數據類型。用定點實現的設計總是比用浮點實現的同一設計更加高效,因為定點實現方案所占用的資源和消耗的功耗更少。若將設計遷移到定點,功耗和占用面積縮減一半并不稀奇。

相較于浮點,定點數據類型的優勢包括 :

? 邏輯資源占用減少

? 功耗降低

? 材料成本降低

? 時延縮短

賽靈思所有器件均支持客戶采用浮點數據類型提供的動態范圍,能實現高達 7.3TFLOPs 的單精度浮點DSP 性能。

業界領先的賽靈思工具套件提供浮點支持。Vivado? 高層次綜合 (HLS) [ 參考資料 1] 和 System Generator for DSP [ 參考資料 2] 本身均支持可變的浮點精度,包括半精度 (FP16)、單精度 (FP32) 和雙精度 (FP64) ;System Generator 還支持自定義精度,具備更大的靈活性。這些工具本身還支持可變定點數據類型。

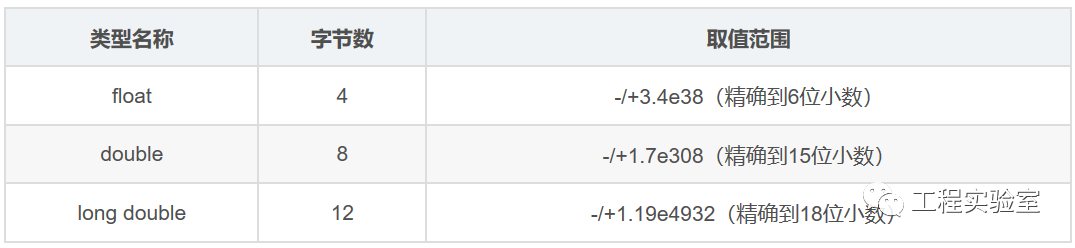

表1 :賽靈思工具支持浮點和定點數據類型

注 :

1. System Generator for DSP 原本不支持 FP16,但支持自定義 FP16。

2. 浮點運算符內核支持 →定點到浮點轉換、浮點到定點轉換以及浮點到浮點的精度變換

賽靈思器件和工具均能支持可變精度數據類型,以便客戶能夠簡單、靈活地調整和適應行業趨勢的變化,例如圖像分類只要求 INT8 或更低的定點計算,以保持可接受的推斷精度 [ 參考資料 3][ 參考資料 4]。

用于高計算強度工作負載的其他器件,例如 GPU,在傳統上其結構決定了只能有效支持單精度浮點。這些廠商現在也開始重新設計產品,以應對趨勢的變化。賽靈思的可擴展架構允許客戶調整信號處理鏈的精度,以便滿足日新月異的行業需求。

當選擇實現浮點還是定點信號處理鏈時,客戶必須在功耗、成本、生產力和精度之間仔細權衡。

賽靈思靈活的 DSP48E2 Slice 可使用所有數據類型進行重要的 DSP 計算。當實現新的定點設計或針對某些應用(適用浮點到定點轉換)將現有設計從浮點轉換成定點時,DSP Slice 與賽靈思工具集相結合能夠帶來巨大優勢和靈活性 [ 參考資料 5]。

對于采用 C/C++ 語言設計的客戶,賽靈思提供 Vivado HLS 并支持任意精度定點數據類型,使客戶能夠方便地采用定點進行設計或者將現有的 C/C++ 設計轉換成定點。

浮點轉換為定點的優勢

對于目前幾乎所有的設計,最小化功耗是需要優先處理的問題。大多數應用產品必須首先滿足嚴格的功耗和散熱范圍要求,才能投產。

普遍接受的一個原則是,浮點設計較之低精度設計而言,功耗更大 [ 參考資料 6][ 參考資料 7]。這對FPGA 來說也一樣,其中的浮點 DSP 模塊已被硬化在 FPGA 中,另外客戶必須使用提供的 DSP 資源和其它 FPGA 資源來實現軟解決方案。浮點方案與同等的定點解決方案相比需占用更多的 FPGA 資源。資源占用增多,功耗隨之增大,最終會增加設計實現的總成本。

將浮點設計轉換為定點設計有助于滿足嚴格的規范,具體體現在以下幾個方面 :

減少 FPGA 資源占用

○ 使用定點數據類型時,所需的 DSP48E2、查找表 (LUT) 和觸發器更少。

○ 存儲定點數字所需的存儲容量更小。

? 功耗更低

○ 減少 FPGA 資源利用自然就會降低功耗。

? 材料成本降低

○ 設計人員可利用額外的資源以相同成本在應用中實現附加功能。

○ 資源的節約能大幅提升 FPGA 的計算能力。計算能力的提升可以讓很多應用受益,例如機器學習

DNN。

○ 資源的節省還可能減小設計所需的器件尺寸。

? 降低時延

○ 當實現 FIR 時減少所用的資源,尤其是減少 DSP48E2 Slice 的占用,能降低定點設計的時延。

? 相近的性能和精度

○ 對于不需要用浮點實現動態范圍的設計和應用,定點方案能提供相近的結果和精度。 有些情況

下,結果甚至更好。

過去由于缺乏工具支持,難以將設計從浮點轉換為定點。對于針對賽靈思 All Programmable 器件的 C/C++ 開發人員來說,可使用 Vivado HLS 減少轉換過程中遇到的挑戰。

這種轉換能帶來多種優勢,在適用情況下應認真考慮——尤其是不需要利用浮點來實現動態范圍和浮點精度的設計,而且很小的可預見的精度損失不會在部署后的應用中導致無效性。

實例 :將浮點 FIR 濾波器轉換為定點

Vivado HLS 中簡單的 FIR 濾波器設計 [ 參考資料 8] 可用來展示浮點 FIR 設計轉換為定點設計如何減少所用資源和功耗并實現相近的結果精度。

單精度浮點 FIR

在 C++ FIR 函數代碼中,頂層函數將 FIR.h 報頭文件中找到的類 CFir 文件 (class CFir) 實例化。

CFir 類 (CFir class) 是主要的 FIR 算法,在報頭文件 FIR.h 中定義。

此函數包含重要的 ARRAY_PARTITION 編譯指示,以確保設計的所有實現方案都是 II=1 (迭代間隔為1)[ 參考資料 9]。PIPELINE 編譯指示也被應用到頂層函數調用。

這些編譯指示、并行產品實現以及用于執行累加的加法器樹,能夠在整個 FIR 函數中確保最低時延(無論數據類型如何),同時保持 II = 1。

在 fp_FIR 函數中,fp_coef_t、fp_data_t 和 fp_acc_t 都被定義為浮點類型,即 C++ 默認的單精度浮點數據類型。

通過報頭文件中的 include 命令加載濾波器系數

用系數創建一個對稱 FIR 濾波器,但本例中,未使用 DSP48E2 Slice 中的預加法器。如果使用預加法器,會實現更高效率。

以下是針對 85 抽頭 FIR 濾波器得到的結果,在 Vivado HLS 中運行 C 綜合與實現,并采用 XCVU9P2FLGB2104 器件上的 400MHz 時鐘(2.5ns 時鐘周期)。見表 2。

表 2 :單精度浮點 FIR 的實現后結果

本例中,需要 423 個 DSP48E2 以及約 23,000 個 LUT 來實現單精度浮點 FIR。實現后,時延為 91 個時鐘周期,FMAX 為 500MHz(遠遠高于 400MHz 的目標)。

轉換到定點 FIR 濾波器

為實現最高 DSP 效率,浮點到定點的轉換必須考慮 DSP Slice 的總線寬度,即 27x18 位乘法器和 48 位累加器。將總線寬度進一步縮減到到設計允許的最低水平,從而盡可能減少資源占用和功耗。

針對這個 FIR 濾波器實例,定義以下定點數據類型以匹配 DSP48E2 Slice 中的總線大小,即 18 位系數中1 個整數位和 17 個小數位 ;27 位數據中 15 個整數位和 12 個小數位 ;以及 48 位累加器中 19 個整數位和29 個小數位。

要使用 Vivado HLS 固有的 ap_fixed 數據類型,必須包含 ap_fixed.h 報頭文件,以定義任意定點數據類型 [ 參考資料 9]。

再次采用 400MHz 時鐘(2.5ns 時鐘周期)和 XCVU9P-2FLGB2104 器件,定點 FIR 設計的 C 綜合與實現產生的結果如表 3 所示。

表 3 :比較兩種設計的實現后結果

正如結果顯示的那樣,重視時延和 FPGA 資源利用率,能獲得明顯的改進。

在 UltraScale 架構中,通過將多個 DSP48E2 Slice 級聯,必要時仍可支持更高總線寬度。采用級聯DSP48E2 Slice 的定點設計,與浮點方案相比仍可顯著減少資源占用和功耗。

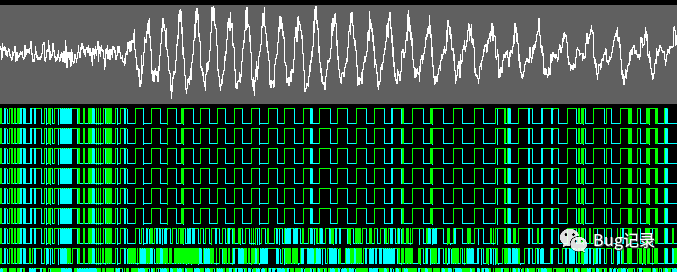

比較濾波器精度

在 System Generator for DSP 中使用 Vivado HLS 模塊(來自賽靈思模塊集),在 MATLAB?/Simulink?環境中比較 FIR 濾波器的兩種實現方案。見圖 1。

圖 1 :System Generator for DSP 模型 - 使用兩種 HLS 解決方案進行分析

System Generator 模型由兩個 Vivado HLS 模塊構成,都經過配置以包含來自 Vivado HLS 的單精度浮點 (FP32) 和定點 FIR 解決方案。兩個模塊具有相同的輸入和離散脈沖信號,然后在 Simulink 示波器上比較每個 FIR 的輸出。見圖 2。

圖 2 :System Generator 中兩個 HLS 設計的輸出

為了方便比較輸出,有必要延遲定點結果,以按照兩種解決方案之間的時延差進行對比。

正如預期的那樣,兩種 FIR 濾波器產生的結果幾乎相同,差異很小。

為進一步分析信號,將兩個輸出相減。得到的信號表明精度損失非常小,處在如圖 3 所示頻譜分析圖中的 -100dBm 至 -160dBm 范圍。

圖 3 :兩個輸出差的 dB 圖

關鍵優勢

當把原始單精度浮點 FIR 濾波器的結果與轉換后定點 FIR 濾波器的結果進行比較時,發現定點設計不僅減少了資源占用 , 降低了時延,同時還能保持甚至提高設計的最大頻率 (FMAX) 。見圖 4。

圖 4 :定點 - 性能相近,并減少時延、資源占用和功耗

大大減少 FPGA 資源占用

本例中的定點 FIR 所占資源不足原始浮點 FIR 的五分之一。

選擇總線寬度,實現到硬件中 DSP48E2 slice 的最佳映射。這樣允許每次相乘都在一個 DSP48E2 Slice 中完成,并針對 85 個系數并行完成。這將 DSP48E2 Slice 的使用量減小至浮點解決方案的 20%。

實現 FPGA 架構中 LUT 的大幅節省(約 90%),因為在定點方案中,無需額外的 LUT 來構建浮點運算。

如果一個設計有 10 個 FIR 濾波器,預計功耗會隨設計而擴展。表 4 顯示了 10 FIR 濾波器設計的單精度和定點實現方案的 XCVU9P FPGA 資源占用。當將單精度浮點的資源占用與定點實現方案進行對比時,會看到明顯的差異。

表 4 :兩種數據類型 10 FIR 濾波器所使用的資源

顯著的資源節省能實現多種優勢,為設計人員帶來深遠的影響,有助于他們改進設計特性集、設計功耗、設計性能和設計成本。

實現顯著的功耗節省

顯著的資源節省能夠相應地降低功耗量。

將本白皮書中單個 FIR 濾波器的兩種實現方案的功耗估算結果進行比較,發現定點 FIR 的功耗減少1.4W。兩種方案中,器件的靜態功耗都是略高于 3W,單個單精度浮點 FIR 設計的總功耗為 4.7W。這表明該設計的動態功耗節省 80% 以上,定點 FIR 功耗為 3.3W。

再看看 10 FIR 濾波器設計,可利用賽靈思功耗估算器 (XPE) 和表 4 中的資源來獲得兩種實現方案的功耗估算結果。圖 5 對節省效果進行了比較。

圖 5 :10 FIR 濾波器實例 :利用定點實現顯著的功耗節約

這個 10 FIR 濾波器實例中,把設計轉換成定點數據類型后,總功耗節省 70%。如果設計具有大量浮點信號處理,需占用大量 FPGA 資源,則通過將部分或全部浮點信號處理鏈轉換成定點,能夠實現巨大的功耗節省。

削減材料成本

將浮點設計轉換成定點方案,能大大減少 FPGA 資源占用。FPGA 資源的削減能降低材料成本。通過三種方法來實現。

1 可利用最新可用的 FPGA 資源來增加應用特性集。

2 由于所用 FPGA 資源大量減少以及通過數據路徑提高 FMAX,因此 FPGA 的總體計算能力顯著提高。

3 由于所需 FPGA 資源減少,因此設計可遷移到更小型的賽靈思 FPGA 中。

相近的精度

通過比較單個 FIR 濾波器設計兩種實現方案的輸出,會發現定點實現方案提供相近的濾波器精度,精度損失僅為 -100dBm 至 -160dBm,同時能降低功耗和成本。

然而,定點方案無法獲得相同的動態范圍,導致設計中出現可預測的精度損失。對于很多設計來說這不成問題,因為只需要最低標準的精度。與單個 FIR 實例類似,這類設計很適合轉換為定點。

對于需要更大精度值的設計,有時可將信號處理鏈中的中間值從浮點轉換為定點。這種方案使設計人員能夠將設計的特定部分(而非全部)轉換為定點。最終,這使設計人員能夠在需要時保持動態范圍,確保維持數據路徑的精度,同時充分發揮定點實現方案帶來的部分優勢。

降低時延

對于單個 FIR 設計實例,可通過濾波器降低時延——定點實現方案為 12 個時鐘周期,浮點設計為 91 個時鐘周期。隨著資源用量減少,尤其是 DSP48E2 Slice 減少,有望降低時延。

除了降低時延,在單個 FIR 實例中,還能提升 FMAX,實現之后能將 FMAX 提升 16%。

結論

賽靈思 All Programmable 器件和工具支持多種數據類型,包括多種精度的浮點和定點。使用浮點的設計與使用定點的同一設計相比,資源用量和功耗都要更高,無論針對 FPGA 還是其他架構(例如 GPU)都是如此。

某些應用領域已開始放棄浮點數據類型,例如深度學習推斷工作負載會盡可能多地使用 INT8 或更低精度,這已經成為明顯的行業趨勢。

如今的設計環境極富挑戰,散熱和功耗要求越來越難以滿足,因此,設計人員必須評估所有可能的方法來降低功耗。其中一種選擇就是將浮點設計轉換為定點。

如果是使用 C/C++,Vivado HLS 等賽靈思工具有助于簡化轉換過程。

設計人員必須對定點數據類型的轉換進行充分權衡,并充分理解這樣做所能帶來的巨大優勢。

繼續使用浮點是通向市場的捷徑,但是成本高。投入時間和精力轉換成定點,這樣能夠降低資源使用量、成本和功耗,而且性能損失很小,從而獲得巨大優勢。

電子發燒友App

電子發燒友App

評論