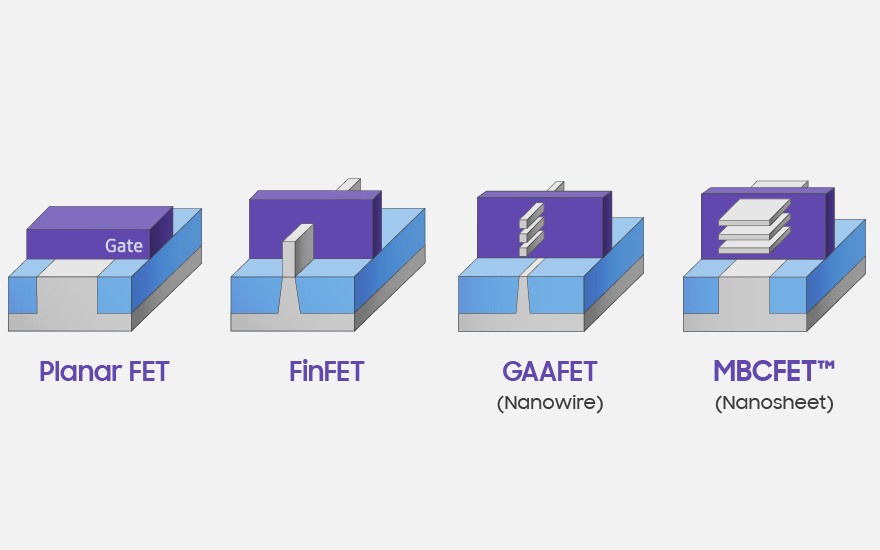

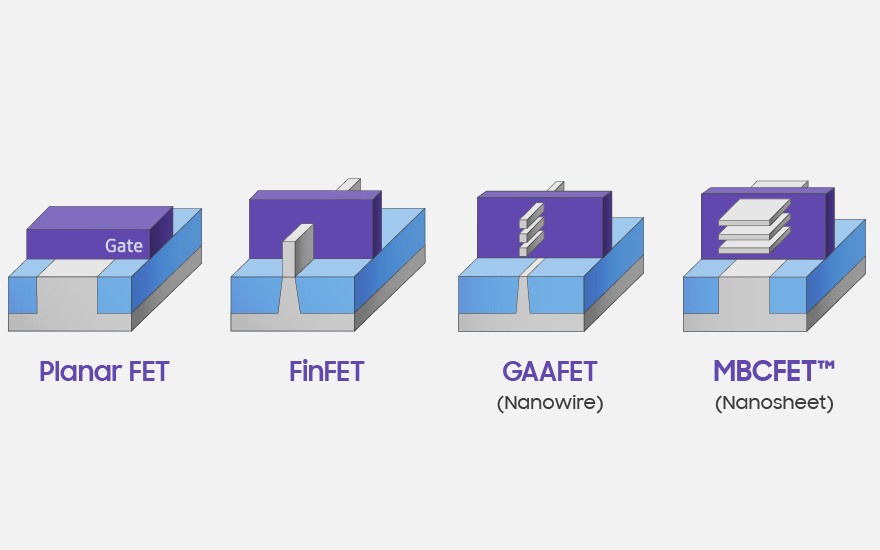

工藝相比,3GAE可將芯片面積減少高達45%,降低50%的功耗或實現35%的性能提升。基于GAA的過程節(jié)點有望用于下一代應用,如移動,網絡,汽車,AI和物聯網。 3GAE的特點是采用GAA的專利變體

2019-05-17 11:29:17 7797

7797

在FPGA上使用OpenCL標準,與目前的硬件體系結構(CPU、GPU,等)相比,能夠大幅度提高性能,同時降低了功耗。此外,與使用Verilog或者VHDL等底層硬件描述語言(HDL)的傳統(tǒng)FPGA

2014-05-26 09:10:18 3967

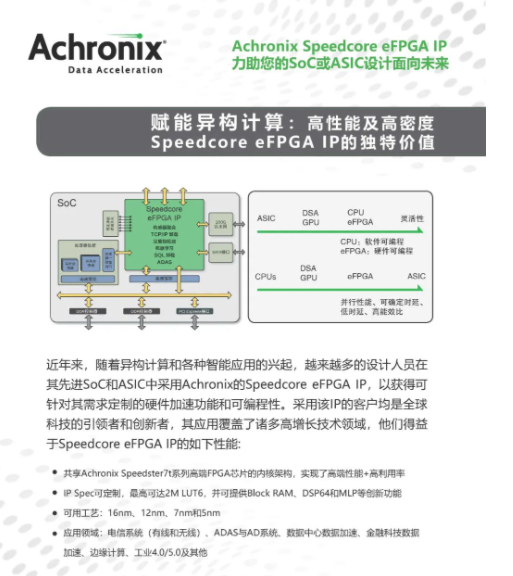

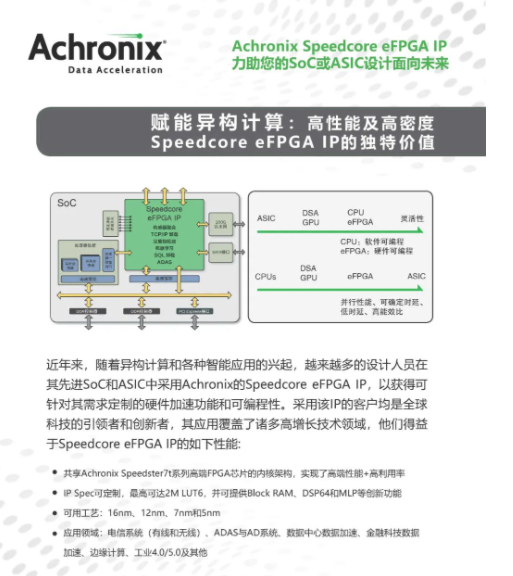

3967 2016年10月11日,Achronix Semiconductor全球同步推出可集成至系統(tǒng)級芯片(SoC)中的Speedcore 嵌入式FPGA(embedded FPGA ,eFPGA)知識產權

2016-10-14 10:46:06 2274

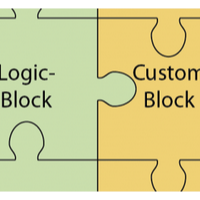

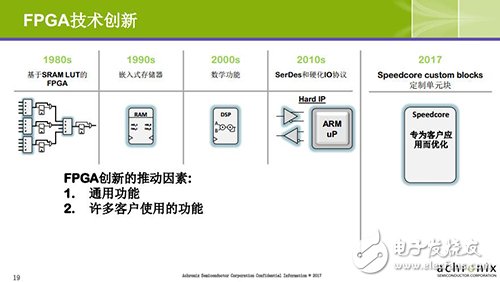

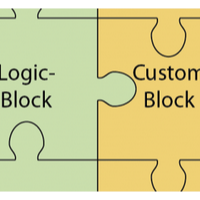

2274 在FPGA獨立芯片上無法實現的功能。利用Speedcore custom blocks定制單元塊,客戶可以獲得ASIC級的效率并同時保持FPGA的靈活性,從而帶來了一種可以將功耗和面積降至最低、同時將數據流通量最大化的高效實現方式。

2017-10-19 11:47:25 5201

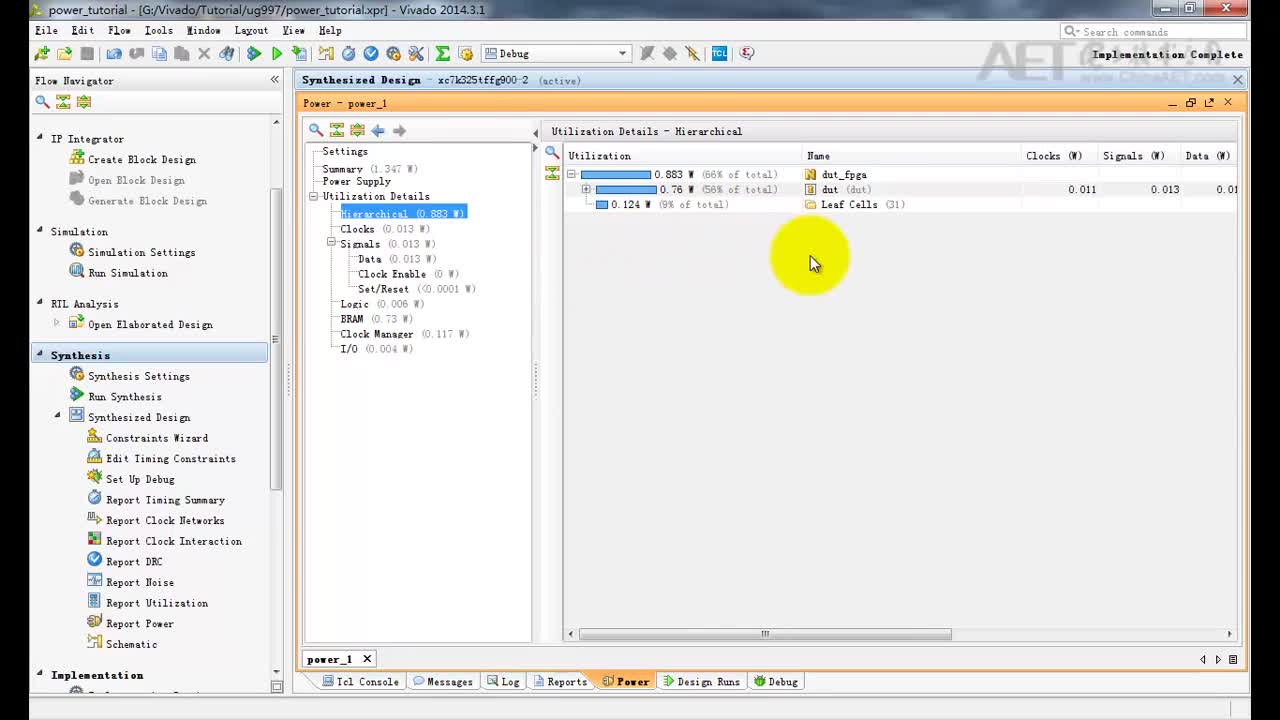

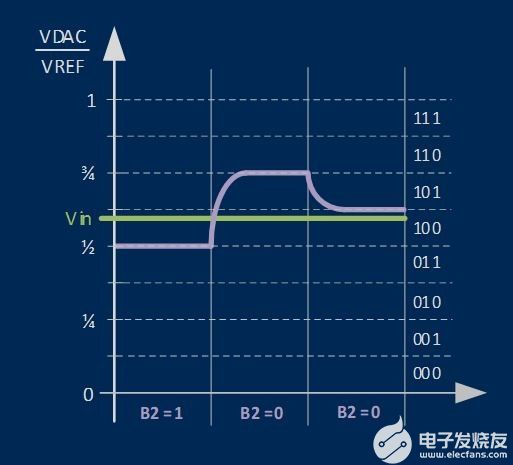

5201 整個FPGA設計的總功耗由三部分功耗組成:1. 芯片靜態(tài)功耗;2. 設計靜態(tài)功耗;3. 設計動態(tài)功耗。

2022-11-24 20:46:41 1028

1028 采用單芯片的SoC形態(tài),兼顧性能和功耗。FPGA-Based DPU在硬件設計上的挑戰(zhàn)主要來自芯片面積和功耗。

2024-02-23 14:40:32 320

320

【導讀】為了滿足人工智能、機器學習、無人駕駛、ADAS等應用提出的越來越高的特殊計算需求,Achronix宣布為其eFPGA IP解決方案推出Speedcore定制單元塊,這是一種可以將功耗和面積降至最低、同時將數據流通量最大化的解決方案。

2017-10-19 11:28:32 988

988 待機功耗、高效率、動態(tài)紋波小優(yōu)異線性調整率和負載調整率內置抖頻電路抗干擾能力強內置150V MOSESOP8封裝【帶抖頻電路,抗干擾能力強,有效解決EMC問題,外圍簡潔,有效縮減外圍布板體積】【帶線損補償,空載帶載電壓一致性高,高低壓輸入情況輸出電壓穩(wěn)定,恒壓精度高】

2021-03-18 16:04:00

面積縮減了50%,賽靈思FPGA芯片在升級中,功耗和性能平衡得非常好。 (2)Kintex-7 FPGA 系列——業(yè)界最佳性價比 堪稱“業(yè)界性價比之王”的Kintex-7 FPGA 系列,能以不到

2012-09-21 13:46:16

FPGA功耗的基本概念,如何降低FPGA功耗?IGLOO能夠做到如此低的功耗是因為什么?

2021-04-30 06:08:49

`FPGA面積優(yōu)化1.對于速度要求不是很高的情況下,我們可以把流水線設計成迭代的形式,從而重復利用FPGA功能相同的資源。2.對于控制邏輯小于共享邏輯時,控制邏輯資源可以用來復用,例如FIR濾波器

2014-12-04 13:52:40

FPGA已經被廣泛用于實現大規(guī)模的數字電路和系統(tǒng),隨著CMOS工藝發(fā)展到深亞微米,芯片的靜態(tài)功耗已成為關鍵挑戰(zhàn)之一。文章首先對FPGA的結構和靜態(tài)功耗在FPGA中的分布進行了介紹。接下來提出了晶體管

2020-04-28 08:00:00

FPGA提供了更加高效的功能。總體上看,采用這些模塊節(jié)約了常規(guī)邏輯資源并增加了系統(tǒng)執(zhí)行的速度,同時可以減少系統(tǒng)功耗。因此更高的邏輯效率也意味著能夠實現更小的器件設計,并進一步降低靜態(tài)功耗和系統(tǒng)成本

2015-02-09 14:58:01

。可編程功能支持靈活的通信標準和網絡協議。圖3應用實例:下一代驅動單芯片方法明顯增強了性能,降低了功耗。在驅動系統(tǒng)中,控制環(huán)速率是最關鍵的性能參數。SoCFPGA控制環(huán)速率是多芯片解決方案的20倍,從100

2021-07-14 08:00:00

芯片對功耗的苛刻要求源于產品對功耗的要求。集成電路的迅速發(fā)展以及人們對消費類電子產品——特別是便攜式(移動)電子產品——的需求日新月異,使得設計者對電池供電的系統(tǒng)已不能只考慮優(yōu)化速度和面積,而必

2019-11-06 07:57:07

突破FPGA系統(tǒng)功耗瓶頸 FPGA作為越來越多應用的“核心”,其功耗表現也“牽一發(fā)而動全身”。隨著工藝技術的越來越前沿化,FPGA器件擁有更多的邏輯、存儲器和特殊功能,如存儲器接口、DSP模塊

2018-10-23 16:33:09

在滿足設計時序要求(包括對設計頻率的要求)的前提下,占用最小的芯片面積。或者在所規(guī)定的面積下,是設計的時序余量更大、頻率跑的更高。這兩種目標充分體現了面積和速度的平衡的思想。作為矛盾的兩個組成部分

2021-07-04 14:16:15

滿足設計時序要求(包括對設計頻率的要求)的前提下,占用最小的芯片面積。或者在所規(guī)定的面積下,是設計的時序余量更大、頻率跑的更高。這兩種目標充分體現了面積和速度的平衡的思想。作為矛盾的兩個組成部分,面積

2021-07-25 11:09:06

滿足設計時序要求(包括對設計頻率的要求)的前提下,占用最小的芯片面積。或者在所規(guī)定的面積下,是設計的時序余量更大、頻率跑的更高。這兩種目標充分體現了面積和速度的平衡的思想。作為矛盾的兩個組成部分,面積

2021-07-26 14:47:48

滿足設計時序要求(包括對設計頻率的要求)的前提下,占用最小的芯片面積。或者在所規(guī)定的面積下,是設計的時序余量更大、頻率跑的更高。這兩種目標充分體現了面積和速度的平衡的思想。作為矛盾的兩個組成部分,面積

2021-11-22 10:04:03

在滿足設計時序要求(包括對設計頻率的要求)的前提下,占用最小的芯片面積。或者在所規(guī)定的面積下,是設計的時序余量更大、頻率跑的更高。這兩種目標充分體現了面積和速度的平衡的思想。作為矛盾的兩個組成部分

2021-07-09 14:24:42

滿足設計時序要求(包括對設計頻率的要求)的前提下,占用最小的芯片面積。或者在所規(guī)定的面積下,是設計的時序余量更大、頻率跑的更高。這兩種目標充分體現了面積和速度的平衡的思想。作為矛盾的兩個組成部分,面積

2021-07-09 14:34:18

滿足設計時序要求(包括對設計頻率的要求)的前提下,占用最小的芯片面積。或者在所規(guī)定的面積下,是設計的時序余量更大、頻率跑的更高。這兩種目標充分體現了面積和速度的平衡的思想。作為矛盾的兩個組成部分,面積

2021-08-10 14:51:33

滿足設計時序要求(包括對設計頻率的要求)的前提下,占用最小的芯片面積。或者在所規(guī)定的面積下,是設計的時序余量更大、頻率跑的更高。這兩種目標充分體現了面積和速度的平衡的思想。作為矛盾的兩個組成部分,面積

2020-08-02 10:45:07

LED屏幕點白平是,芯片比別的模組溫度更高些,是什么原因啊,請大俠指點指點。

2011-12-04 19:26:52

你好。我正在寫一篇技術論文和需要知道LUT和Kintex 7 FPGA芯片中的FF所需的資源。資源可以是晶體管數量,柵極數,芯片面積大小等等。我在一個網站上聽說LUT需要2.5倍的“FPGA門”,但

2019-02-27 13:49:58

請教各位,LabVIEW 2010為什么可以實現更高效的測量?

2021-04-26 07:15:49

,獲得的縱向電場分布幾乎是恒定的,而給定擊穿電壓所需的漂移區(qū)長度大幅降低。與此同時,漂移區(qū)的雜質濃度提高。這兩種技術都可導致通態(tài)電阻的大幅降低。擴展器件系列,實現更高阻斷能力占板空間更小的全新高效邊緣終端

2018-12-07 10:21:41

小弟剛學FPGA ,在看Veriolg ,遇到縮減運算符,對于縮減與 縮減或能理解,那個非本身就是單目運算,縮減非是怎么回事呢?

2013-10-07 10:13:36

nRF52832低功耗藍牙(Bluetooth? low energy) (前稱為藍牙智能)系統(tǒng)級芯片(SoC)的晶圓級芯片尺寸封裝(WL-CSP)產品,占位面積為標準封裝nRF52832器件

2017-08-16 10:43:56

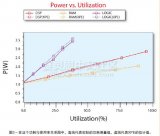

從Xilinx公司推出FPGA二十多年來,研發(fā)工作大大提高了FPGA的速度和面積效率,縮小了FPGA與ASIC之間的差距,使FPGA成為實現數字電路的優(yōu)選平臺。今天,功耗日益成為FPGA供應商及其

2019-09-20 06:33:32

,工業(yè)界對芯片設計的要求已從單純追求高性能、小面積轉為對性能、面積、功耗的綜合要求。而微處理器作為數字系統(tǒng)的核心部件,其低功耗設計對降低整個系統(tǒng)的功耗具有重要的意義。

2019-10-14 07:48:14

,更高效的處理視頻; e. 通過CODEC和1080p視頻工作臺IP內核提供全面的解決方案。 2 Arria V系列:中端市場最佳性價比之王 2.1 Arria V系列 FPGA芯片基本描述

2012-09-21 13:49:05

更高的性能,還在于它們具有更低的密度,因而對于相同的操作可以消耗較少的功率。評估您的器件選項時,請考慮專門邏輯的類型和數量。 選擇適當的 I/O 標準也可以節(jié)省功耗。這些都是簡單的決定,如選擇最低

2012-01-11 11:59:44

功能可能產生更高的功耗。● 在FPGA中除了實現專用標準器件(ASSP)所具有的復雜功能,還得添加一些額外的功能,實屬一大挑戰(zhàn)。FPGA的設計復雜性和難度可能會給產品的開發(fā)帶來一場噩夢。 `

2016-06-29 09:37:38

在微功耗場景下,使用RCC是否比低功耗芯片的效率更高?設計例子:單火取電項目,從AC線取電取電,交流220V轉直流12V,再通過DC-DC方案,將12V轉為3.3V供Zigbee工作,該Zigbee

2016-06-17 13:50:42

。可編程功能支持靈活的通信標準和網絡協議。圖3應用實例:下一代驅動單芯片方法明顯增強了性能,降低了功耗。在驅動系統(tǒng)中,控制環(huán)速率是最關鍵的性能參數。SoCFPGA控制環(huán)速率是多芯片解決方案的20倍,從100

2021-07-12 08:00:00

方面滿足DSP應用的需要。然而在應用FPGA進行系統(tǒng)設計綜合過程中,選擇芯片的運行速度優(yōu)化和資源利用優(yōu)化常常是相互矛盾的,對速度指標要求高的設計優(yōu)化常常要占用較大的芯片資源,而減小芯片面積的設計又需要

2019-08-02 06:03:48

STM32定時器的功能包括哪些呢?如何更高效的去實現STM32按鍵和延時功能呢?

2021-11-23 07:59:06

的提高,光收發(fā)器模塊的功耗勢必增大,同時其外形尺寸需要保持不變。這就給模塊設計工程師帶來巨大壓力,要求其使用低功耗、高度集成的芯片。那么如何在狹小空間內提供更多功能的同時實現更高效地供電?本設計方案提出一種創(chuàng)新的電源管理系統(tǒng),能夠以較小的空間高效供電,且滿足下一代光收發(fā)器的需求。

2021-02-24 06:22:34

和寬厚比公式做為一名 SMT 工藝工程師,即使已知“面積比和寬厚比的最佳條件”,但面對成千上萬的開口,在沒有專業(yè)工具軟件的前提下,要想實現“驗證每一個開口是否符合 IPC7525 標準”是極其不現實

2021-07-01 13:46:58

器件的功耗更低,能以更高的速度工作,有更高的性能(2倍的帶寬),并有更大的密度。與DDR2相比,DDR3器件的功耗降低了30%,主要是由于小的芯片尺寸和更低的電源電壓(DDR3 1.5V而DDR2

2019-08-09 07:42:01

MCU和電源的選擇讓您的嵌入式電路設計更高效

2021-04-02 07:16:43

同時具備設計面積最小、運行頻率最高是不現實的。更科學的設計目標應該是在滿足設計時序要求(包括對設計頻率的要求)的前提下,占用最小的芯片面積。或者在所規(guī)定的面積下,是設計的時序余量更大、頻率跑的更高

2020-09-18 10:32:44

,可減小電容器的尺寸,因而可進一步縮減電路整體的安裝面積。豐富的輸出電壓陣容,支持眾多應用BUxxJA2MNVX-C 系列擁有從1.0V到3.3V共10種固定輸出電壓版本,幾乎涵蓋已有各種元器件的所有

2018-12-05 10:09:47

封裝技術至關重要。衡量一個芯片封裝技術先進與否的重要指標是:芯片面積與封裝面積之比,這個比值越接近1越好。封裝時主要考慮的因素:芯片面積與封裝面積之比,為提高封裝效率,盡量接近1:1。引腳要盡量短以

2020-02-24 09:45:22

1.工藝節(jié)點 首先不管選擇什么廠家的產品,都建議在其主流產品中選擇合適的芯片。 以上是目前 Xilinx 主流的也是常用的幾個 FPGA 產品系列,這里不談傳說中的后兩個系列

2020-12-23 17:21:03

ADAU1850相比上款產品擁有極小的芯片面積,超強音質ANC codec,以更低的成本提供更精確降噪的可能。ADAU1850詳細參數特征:1、28pin,0.4 mm pitch, 3.0 mm

2021-08-23 11:12:42

的小型化,從而大大縮減安裝面積。(*截至2016年11月18日ROHM調查數據)通過輸出電壓的線性控制,使電機旋轉速度的精度更高以往的分立結構存在相對于外部MCU生成的PWM信號來說輸出電壓的線性度較低

2018-12-04 10:18:47

請教下,誰能夠推薦一款比 cc1100 功耗更低的芯片 ?

2020-08-20 08:00:30

芯片靜態(tài)功耗;2. 設計靜態(tài)功耗;3. 設計動態(tài)功耗。l芯片靜態(tài)功耗:FPGA在上電后還未配置時,主要由晶體管的泄露電流所消耗的功耗l設計靜態(tài)功耗:當FPGA配置完成后,當設計還未啟動時,需要維持I

2014-08-21 15:31:23

和期望輸出電壓的規(guī)范,并且需要選擇一些 FET。另外,如果您是一名 IC 設計人員,則您還會有一定的預算,其規(guī)定了 FET 成本或者封裝尺寸。這兩種輸入會幫助您選擇總 MOSFET 芯片面積。之后

2018-09-26 10:24:59

的CPU為例,外形尺寸28×28mm,芯片尺寸10×10mm,則芯片面積/封裝面積=10×10/28×28=1:7.8,由此可見QFP比DIP的封裝尺寸大大減小。QFP的特點是: 1.適合用SMT

2018-09-03 09:28:18

管殼到環(huán)境的熱阻隨芯片面積只有很小的變化。●但是,TO220和TO247具有不同的管殼到環(huán)境的熱阻(水平線)。由于TO220與環(huán)境相連的引線架的面積大了許多,因此TO220的值(1.4K/W)幾乎比

2018-12-03 13:46:13

請問圖中字樣的三極管芯片面積是多大?謝謝

2014-05-08 17:07:35

成本 通過表1我們不難得出以下結論: 與上一代 FPGA相比,其功耗降低了50%,成本削減了35%,性能提高30%,占用面積縮減了50%,賽靈思FPGA芯片在升級中,功耗和性能平衡得非常好。 (2

2012-09-06 16:24:35

高度集成的單芯片射頻收發(fā)器解決方案 (例如,ADI 推出的 ADRV9008/ADRV9009 產品系列) 的面市促成了此項成就。在此類系統(tǒng)的 RF 前端部分仍然需要實現類似的集成,意在降低功耗 (以改善熱管理) 和縮減尺寸(以降低成本),從而容納更多的 MIMO 通道。

2019-07-31 07:05:44

自從Xilinx推出FPGA二十多年來,研發(fā)工作大大提高了FPGA的速度和面積效率,縮小了FPGA與ASIC之間的差距,使FPGA成為實現數字電路的優(yōu)選平臺。今天,功耗日益成為FPGA供應商及其客戶關注的問題。降低FPGA功耗是縮減封裝和散熱成本、提高器件可靠性以及打開移

2011-03-15 14:58:34 31

31 集成電路晶圓代工企業(yè)中芯國際集成電路制造有限公司(“中芯國際”)日前宣布,其0.11微米后段銅制程(Cu-BEoL)超高密度IP庫解決方案可為客戶平均節(jié)省31%芯片面積。

2012-03-12 09:14:40 1004

1004 全新賽靈思(Xilinx)FPGA 7系列芯片精彩剖析:賽靈思的最新7系列FPGA芯片包括3個子系列,Artix-7、 Kintex-7和Virtex-7。在介紹芯片之前,先看看三個子系列芯片的介紹表,如下表1所示: 表

2012-08-08 15:04:04 395

395 白皮書 :采用低成本FPGA實現高效的低功耗PCIe接口 了解一個基于DDR3存儲器控制器的真實PCI Express (PCIe) Gen1x4參考設計演示高效的Cyclone V FPGA怎樣降低系統(tǒng)總成本,同時實現性能和功耗

2013-02-26 10:04:25 72

72 2016 年 2 月 26 日─ Imagination Technologies 宣布,推出適用于大眾市場的新系列 PowerVR GPU 產品,為成本敏感市場設立了性能、功耗與面積的新標準。

2016-02-26 11:11:25 735

735 Achronix Semiconductor公司今日宣布:推出可集成至客戶系統(tǒng)級芯片(SoC)中的Speedcore? 嵌入式FPGA(embedded FPGA ,eFPGA)知識產權(IP)產品,并即刻開始向客戶供貨。

2016-10-11 18:12:01 1054

1054 有一種新方法可用于測量真實FPGA器件的功耗估計值 現代的FPGA 芯片能夠開發(fā)高性能應用,但在這些設計中電源管理通常是一大限制因素。FPGA 器件的資源使用最能決定設計的容量和處理速度,但是增加

2017-11-18 01:14:02 5406

5406

為設計尋找“完美”FPGA 的重要性日漸升級,其中功耗已成為主要考慮因素。功耗管理在大部分應用中都非常關鍵。某些標準已為單卡或者單個系統(tǒng)設定了功耗上限。鑒于此,設計人員必須在設計過程中更早地對功耗

2017-11-22 15:03:01 2573

2573 的數量,可以用消耗的觸發(fā)器和查找表的個數或者是等效邏輯門數來衡量;速度是指一個設計在FPGA上穩(wěn)定運行時所能 達到的最高頻率,由設計時序狀態(tài)決定。 關于面積和速度的折衷,應在滿足設計時序和工作頻率要求的前提下,占用最小的芯片面積;或者在所規(guī)定

2017-11-25 03:57:01 802

802

要點:

術量產級測試芯片的驗證

Speedcore驗證芯片通過了嚴格的整套測試,同時所有功能已獲驗證

在所有的運行條件下,復雜的設計均可運行在500MHz速率

2018-01-19 15:02:33 7697

7697

隨著芯片集成度越來越高,隨機存儲器(random access memory,RAM)在片上系統(tǒng)(system on chip,SoC)中的占比也越來越高,因此RAM對SoC的面積及功耗的貢獻

2018-01-19 15:27:13 1

1 工智能(AI)/機器學習、5G移動通信、汽車先進駕駛員輔助系統(tǒng)(ADAS)、數據中心和網絡應用; Speedcore custom blocks定制單元塊可以大幅度地提升性能、功耗和面積效率,并支持以前在FPGA獨立芯片上無法實現的功能。

2018-01-22 16:42:01 816

816 由于FPGA具有可編程專用性,高性能及低功耗的特點,浪潮推出基于FPGA的深度學習加速解決方案,希望通過更高配置的硬件板卡設計和內置更高效已編譯算法,來加速FPGA在人工智能領域的應用。

2018-02-19 05:02:00 656

656 芯片面積估計就是通過目標工藝的庫信息,設計的spec、以往設計的信息及,部分IP的綜合報告來統(tǒng)計這主要部分的總面積的過程。

2018-04-25 15:36:59 10289

10289 Imagination公司日前基于其神經網絡加速器(NNA)架構PowerVR 2NX推出了兩款全新的神經網絡內核AX2185和AX2145,其設計目的是在極小芯片面積上以極低功耗實現神經網絡高性能計算。

2018-06-20 10:50:04 3674

3674

該組項目將使研究機構和公司能夠使用Achronix高性能Speedcore eFPGA技術快速構建低成本測試芯片

2018-12-01 08:25:37 2970

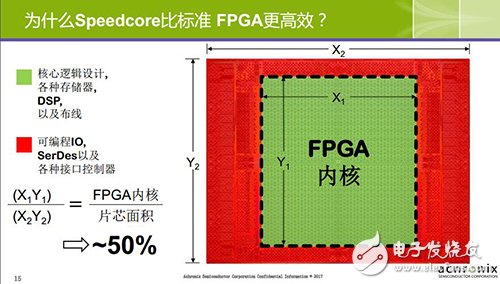

2970 %、功耗降低了50%、芯片面積減少65%,同時保留了原有的Speedcore eFPGA IP的功能,即可將可編程硬件加速功能引入廣泛的計算、網絡和存儲應用,實現接口協議橋接/轉換、算法加速和數據包處理。

2018-12-10 17:28:00 688

688 2016年,Achronix推出的Speedcore成為首款向客戶出貨的嵌入式FPGA(eFPGA)IP,使客戶將FPGA功能集成到他們的SoC中成為可能。由于Speedcore IP是專為計算

2018-12-23 16:29:40 4151

4151 和公司能夠全面對接Achronix領先Speedcore eFPGA技術。 eFPGA技術正在迅速地成為基于系統(tǒng)級芯片(SoC)的CPU卸載功能中可編程硬件加速單元的必備硅知識產權(IP),已被廣泛用于包括人工智能/機器學習(AI / ML)、區(qū)塊鏈、網絡加速、智能網卡和智能物聯網等各種應用。這些被

2018-12-24 14:47:29 1164

1164 2019 年 12 月 10 日——萊迪思半導體公司(NASDAQ:LSCC),低功耗可編程器件的領先供應商,今日宣布推出全新低功耗 FPGA 技術平臺——Lattice Nexus?。該技術平臺

2019-12-11 15:05:51 899

899 傳值、傳址、傳引用的區(qū)別,哪個更高效?

2020-06-29 15:05:26 5370

5370 降低了50%,芯片面積減少了65%,同時保留了Speedcore eFPGA IP的原有功能,將可編程硬件加速功能帶到廣泛的高性能計算、網絡和存儲應用中。Achronix將于9月26日參加在圣克拉拉

2020-08-07 15:41:06 556

556 芯片能夠提供 1.8 倍的邏輯密度、速度增快 15%,或者功耗降低 30%,同樣制程的 SRAM 也十分優(yōu)異且面積縮減。

2020-08-10 11:34:37 1432

1432 。 得益于最新的5nm工藝、全新Arm架構的使用,以及高通自主研發(fā)設計,新一代驍龍888不僅在性能上提升非常明顯,而且功耗控制也趨于完美。在這個芯片性能與功耗并駕齊驅的時代,沒有哪個芯片廠家像高通這樣注重性能和功耗的極致平衡,這種極致,在驍

2020-12-04 13:13:07 2231

2231 Achronix Speedcore eFPGA IP使客戶公司能夠將FPGA功能集成到其ASIC或SoC器件中。 Speedcore eFPGA具有可變換的架構,它可讓客戶根據需求去定義eFPGA IP的FPGA邏輯陣列、存儲器和DSP處理能力。

2021-03-26 10:18:54 1905

1905 葉片是植物進行光合作用合成有機物的重要器官,它的面積大小對農作物產量具有重要影響。 另外,在農業(yè)科研中,許多生理指標的測定和研究也都會涉及到葉面積。早期測定植物葉片面積,往往需要通過畫格子、稱重

2021-08-02 18:08:50 1254

1254 Achronix將在此次ICCAD 2021上展出Speedcore eFPGA IP及其全系可編程硬件加速器,包括Speedcore eFPGA IP、Speedster7t獨立FPGA芯片

2022-02-08 16:08:31 1511

1511 在查看芯片面積時,智能手機和可穿戴設備中的小尺寸設計將明顯受益于基于軟件的基帶實現所實現的芯片面積減少。

2022-06-29 10:23:38 723

723 平方毫米的芯片面積。Adesto 還可以提供 12 位 SAR 輔助流水線 ADC,在僅 0.05mm2 的裸片面積上實現 200Msamples/s 的采樣率、10mW 的功耗。

2022-08-10 17:29:51 650

650

相對于FPGA+SoC的方案,集成了eFPGA的SoC或者ASIC將在功耗、單位成本、延遲和連接帶寬方面獲得巨大收益,其價值已經得到全球數十家頂級創(chuàng)新公司驗證。

2022-12-23 10:21:14 286

286

(Flip-Flop)和查找表(Look Up Table)等資源。在FPGA設計過程中,速度的提高通常以面積擴增為代價,面積的縮減通常以速度的降低為代價。如何權衡二者的性能要求,在滿足時序(速度)要求的前提下盡可能節(jié)約邏輯資源(面積),是FPGA設計過程中需要考慮的重點。

2023-06-09 09:36:37 798

798

在人工智能的不斷發(fā)展的時代,永遠需要性能更高、功耗更低、成本更低的芯片面世。

2022-03-21 09:23:45 840

840

尋求最高集成度的設計人員可以選擇去開發(fā)一款包含Speedcore eFPGA IP的單芯片ASIC。然而,在某些應用中,單芯片集成無法實現某些產品靈活性,而這在使用基于chiplet的方案中就有更多靈活性。

2023-09-06 15:12:11 234

234

電子發(fā)燒友App

電子發(fā)燒友App

評論