在嵌入式系統(tǒng)中,很容易在系統(tǒng)核心找到 FPGA。這是因為 FPGA 能同時并行執(zhí)行多個功能,并具有確定性的響應(yīng)。很多嵌入式系統(tǒng)還包含一個處理器,用來處理通信任務(wù)、內(nèi)務(wù)管理、調(diào)度任務(wù)以及通常在軟件中執(zhí)行的其他任務(wù)。

這種 FPGA 與處理器的組合會增加系統(tǒng)的 SWAP-C。SWAP-C 是指解決方案的尺寸、重量、功耗和成本。顯然,同時使用處理器和 FPGA 不僅會增加材料成本,同時還會增加偶生工程成本(NRE)。此外,設(shè)計與驗證工作變得更加復(fù)雜。兩個器件還需要更多板級空間,這會增大解決方案的尺寸和重量。電源結(jié)構(gòu)也比只用一個器件時復(fù)雜,這進(jìn)一步影響 SWAP-C。

盡管難以用軟件驅(qū)動的處理器來實現(xiàn)通常由 FPGA 執(zhí)行的功能,但在 FPGA 內(nèi)部實現(xiàn)處理器,通常能讓設(shè)計大受裨益。

對于在賽靈思 FPGA 中實現(xiàn)處理器,我們有多個選擇:

PicoBlaze– 8 位高確定性微控制器(見賽靈思中國通訊 54 期,“充分發(fā)揮 PicoBlaze 微控制器的優(yōu)勢。”)

MicroBlaze– 32 位 RISC(精簡指令集計算機(jī))處理器,可針對眾多應(yīng)用在性能和面積方面進(jìn)行定制。

Zynq UltraScale MPSoC 和 Zynq-7000 SoC將硬化的嵌入式 ARM 處理器和可編程邏輯完美集成在單個芯片上。(如需了解有關(guān) Zynq-7000 SoC 使用方面的信息,敬請查閱MicroZed Chronicles)

本文中,我們將深入了解如何在 FPGA 設(shè)計中實現(xiàn)賽靈思 MicroBlaze 處理器以減小 SWAP-C。

什么是 MicroBlaze

MicroBlaze 是 32 位軟核處理器。這意味著它是一款可先定制,然后綜合,最后布局布線到目標(biāo) FPGA 的邏輯資源中的軟 IP 核。每個 MicroBlaze 處理器實例都是自定義的,包含 FPU(浮點(diǎn)單元)、MMU(存儲器管理單元)以及指令與數(shù)據(jù)緩存這樣的高級特性。

用戶可在 MicroBlaze 處理器上運(yùn)行一系列操作系統(tǒng),包括 FreeRTOS、Micrium uc/OSiii 和 Linux。用戶還可以運(yùn)行裸機(jī)代碼。實例的軟特性可確保不存在過時問題。簡而言之,MicroBlaze 處理器是一款功能非常強(qiáng)大的嵌入式系統(tǒng)開發(fā)工具。

創(chuàng)建 MicroBlaze 系統(tǒng)

在設(shè)計中實現(xiàn) MicroBlaze 處理器是賽靈思 Vivado HL WebPACK 版本的一項標(biāo)準(zhǔn)功能。

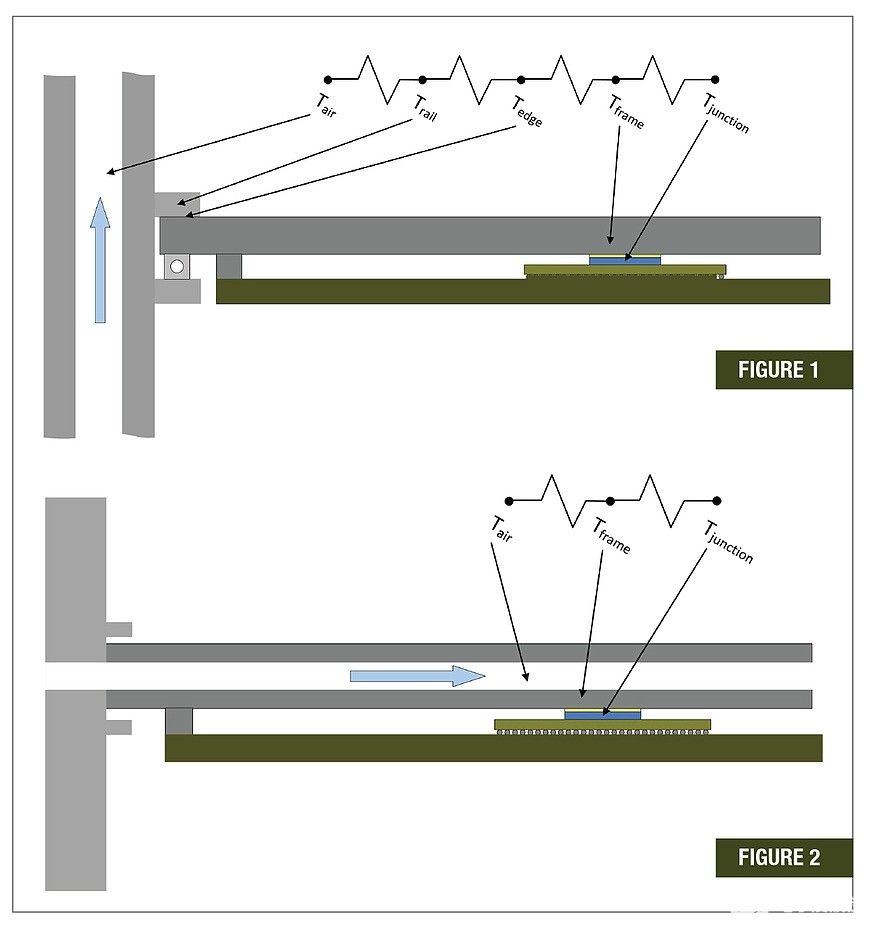

首先要做的是在 Vivado 中創(chuàng)建新項目,并添加一個新的方框圖。然后,我們可以從 IP Catalog 中選擇添加 MicroBlaze 處理器核。一旦我們將 MicroBlaze 處理器放在方框圖中,應(yīng)針對所需的性能對其進(jìn)行自定義。打開要自定義的 MicroBlaze 處理器后,會出現(xiàn)五個處理器自定義頁面中的第一個。在第一頁中,我們可以為處理器核選擇所需的性能,如圖 1 所示。本例中,我們將開發(fā)一個高性能 MicroBlaze 處理器。

?

圖 1:選擇 MicroBlaze 的配置。

要創(chuàng)建一個基礎(chǔ)的系統(tǒng),我們需要以下 IP 核:

AXI UART lite – 雙擊它可設(shè)置 RS232 選項。默認(rèn)設(shè)置是 9600bps,無奇偶校驗位,一個停止位。

AXI 定時器

AXI 中斷控制器 – 需要一個連接模塊驅(qū)動來自定時器和 AXI UART lite 的中斷。

用于 AXI 數(shù)據(jù)和指令緩存的 AXI BRAM 控制器和 BRAM

用于輸出 166.667MHz 時鐘和 333MHz 時鐘的時鐘向?qū)?/p>

MicroBlaze 調(diào)試模塊

用于連接定時器和 UART 的 AXI 外設(shè)互連

用于連接 MIG (DDR) 和 AXI BRAM 控制器的 AXI 存儲器互連

針對 MicroBlaze 時鐘域的處理器復(fù)位系統(tǒng)

針對存儲器接口生成器時鐘域的處理器復(fù)位系統(tǒng)

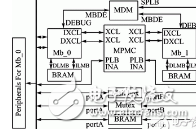

這些模塊的連接架構(gòu)如以下的圖 2 所示:

?

圖 2:高級方框圖

我們將 100MHz 時鐘作為時鐘向?qū)У妮斎耄撓驅(qū)Ю?MMCM(混合模式時鐘管理器)生成 100MHz、166.667MHz 和 200MHz 的時鐘。MicroBlaze 處理器將采用 MMCM 的 100MHz 輸出來運(yùn)行,而其他時鐘將被用于存儲器接口生成器。下面的表 1 和表 2 給出了 AXI 互連的配置:

?

表 1:外設(shè) AXI 互連,時鐘和復(fù)位配置

?

?

表 2:存儲器 AXI 互連,時鐘和復(fù)位配置

配置 DDR 存儲器

我們正在開發(fā)高性能 MicroBlaze 系統(tǒng),因此我們希望能從 DDR SDRAM 執(zhí)行我們的程序,并且還能使用更多特殊功能(包括 DMA),這樣 MicroBlaze 處理器能夠處理所捕獲的數(shù)據(jù)。DDR 存儲器接口由于其復(fù)雜的驅(qū)動要求而難以實現(xiàn),但是賽靈思 MIG 可以自動生成 AXI 總線與 DDR SDRAM 之間的 DDR 接口。

MIG 在 IP Catalog 中提供,通過對它進(jìn)行自定義,我們可以選擇想要的時鐘頻率、目標(biāo)存儲器設(shè)備、存儲器選項、終止計劃以及引腳分配。圖 3 給出了目標(biāo) DDR 設(shè)備的選擇。盡管開始看起來比較復(fù)雜,但其實很容易上手和使用,而且運(yùn)行快速。

?

圖 3:MIG 選擇目標(biāo)設(shè)備

根據(jù)應(yīng)用需求對接口進(jìn)行自定義后,本例中我們需要提供兩個時鐘:200MHz 參考時鐘和 166.667MHz 系統(tǒng)時鐘。

設(shè)計中所有模塊都根據(jù)需求進(jìn)行了自定義,我們可以創(chuàng)建 RTL 包裝器并重新生成輸出,這樣就能構(gòu)建系統(tǒng)并開發(fā)第一個應(yīng)用。

開發(fā)軟件

完成項目實現(xiàn)并獲得數(shù)字文件后,我們可以打開實現(xiàn)后的設(shè)計,并將 HDF 和數(shù)字文件導(dǎo)出至 SDK。現(xiàn)在,我們已準(zhǔn)備好創(chuàng)建軟件應(yīng)用。

如果是第一次打開 SDK,那么軟件會詢問你想使用哪個工作空間。工作空間是存儲項目和相關(guān)軟件項目文件(例如板支持包 (BSP) 和硬件定義)的區(qū)域。

要啟動并在 SDK 中運(yùn)行,我們需進(jìn)行以下操作:

創(chuàng)建硬件定義項目

為硬件定義創(chuàng)建 BSP

創(chuàng)建應(yīng)用

構(gòu)建應(yīng)用

定義調(diào)試環(huán)境,以使我們能夠通過 JTAG 鏈路在開發(fā)板上運(yùn)行應(yīng)用

第一步是導(dǎo)入硬件定義。要在 Vivado 中進(jìn)行此操作,應(yīng)從 SDK 菜單中選擇 file -> new -> other。這會打開一個對話框,如圖 4 所示。選擇 Xilinx 文件夾下的“Hardware Platform Specification”

?

圖 4:選擇硬件平臺規(guī)范

在下個對話框中輸入項目名稱。比較好的方法是始終命名為 project_HW,以清楚標(biāo)明。瀏覽至 Vivado 項目中包含 HDF 文件的目錄。注意,這在 Vivado 項目下的 .sdk 文件夾內(nèi)。

這樣可創(chuàng)建硬件規(guī)范,并出現(xiàn)在 SDK 左側(cè)的項目瀏覽器中。這個項目中,你可打開 HDF 文件,并查看所有存儲器映射的外設(shè)的地址。

利用創(chuàng)建的硬件平臺,我們現(xiàn)在就可創(chuàng)建 BSP。這里面包含用來驅(qū)動和控制硬件的驅(qū)動程序和 API。我們可選擇 file -> new -> board support package,以創(chuàng)建 BSP。這將打開一個對話框,我們可以逐頁設(shè)置。

輸入項目名稱。注意它如何關(guān)聯(lián)我們剛創(chuàng)建的硬件平臺。本例中,我們使用獨(dú)立的操作系統(tǒng)。這會打開一個 BSP 的設(shè)置彈出窗口。在這里,我們不需要做任何修改,但是如果需要,可以添加一些選項,例如輕量級 IP 協(xié)議棧等。

在獨(dú)立頁面中,我們還可為編譯器選擇 stdin 和 stdout。確保將它設(shè)置成 AXI UART。

此時,我們就可以創(chuàng)建自己的應(yīng)用了。本例中,我使用“hello world”簡單模板。我們在 SDK 中選擇 -> new -> application project ,以創(chuàng)建應(yīng)用項目。這將打開一個對話框,我們可以在對話框中選擇之前創(chuàng)建的 BSP,以及硬件定義和我們針對的處理器。(本例中只有一個。)

通過這些步驟,我們可以創(chuàng)建一個通過 UART 輸出“hello world”字符串的簡單應(yīng)用。選擇“build all”以構(gòu)建 BSP 和應(yīng)用項目,并產(chǎn)生一個 ELF 文件,你可以下載這個文件并在硬件上運(yùn)行。

在硬件上運(yùn)行

我們需要創(chuàng)建一個調(diào)試環(huán)境,然后點(diǎn)擊下載 ELF 文件。為此,右鍵點(diǎn)擊應(yīng)用項目并選擇 Debug As -> Debug Configurations。這將打開一個對話框,如圖 5 所示,在此創(chuàng)建一個新的調(diào)試環(huán)境。我們希望創(chuàng)建一個新的 GBD 調(diào)試應(yīng)用。

?

圖 5:創(chuàng)建調(diào)試配置

提供一個名稱,在接近底部的下拉菜單中選擇“Reset Processor”。我們還需要點(diǎn)擊“Debugger applications”標(biāo)簽,并將“stop at main() when debugging.”選項取消選中,以確保應(yīng)用程序下載后自動運(yùn)行。最后,點(diǎn)擊apply,而非調(diào)試,然后關(guān)閉。

首先要做的是對 FPGA 編程。我們在 Xilinx Tools -> Program FPGA 下進(jìn)行此操作。對 FPGA 編程后,就可以下載 ELF 文件。點(diǎn)擊頂部菜單上的“bug”圖標(biāo),這樣就可使用剛剛創(chuàng)建的調(diào)試配置。

下載后,你可以看到軟件運(yùn)行,而且“hello world”消息出現(xiàn)在所選的終端程序中。

結(jié)論

構(gòu)建 MicroBlaze 系統(tǒng)非常簡單,而且容易實現(xiàn),開發(fā)系統(tǒng)上運(yùn)行的軟件也同樣如此。如果你想降低系統(tǒng)的 SWAP-C,那么 MicroBlaze 處理器可以幫到你。

電子發(fā)燒友App

電子發(fā)燒友App

評論