摘 要: 目前星載信號(hào)處理平臺(tái)中大量使用商用芯片,但商用芯片抗輻射能力較弱,在空間環(huán)境下常出現(xiàn)單粒子翻轉(zhuǎn)(Single Event Upset,SEU),從而造成系統(tǒng)功能紊亂,甚至中斷。提出以星載信號(hào)處理平臺(tái)中大量使用的SRAM型FPGA為研究對(duì)象,采用故障注入的方式研究FPGA中不同硬件資源對(duì)于SEU效應(yīng)的敏感性問(wèn)題。根據(jù)不同資源對(duì)SEU效應(yīng)表現(xiàn)出不同敏感性的結(jié)論,可在SRAM型FPGA的抗SEU防護(hù)上進(jìn)行有針對(duì)性的設(shè)計(jì)。

0 引言

隨著星載信號(hào)處理平臺(tái)對(duì)于信號(hào)處理能力需求的不斷提升,宇航級(jí)芯片已越來(lái)越難以滿足需求,而商用芯片相對(duì)宇航級(jí)芯片擁有更強(qiáng)的處理能力和更多的處理資源。所以基于商用芯片構(gòu)建星載處理平臺(tái)的商用現(xiàn)成技術(shù)(Commercial Off-The-Shelf,COTS)成為當(dāng)前衛(wèi)星通信平臺(tái)設(shè)計(jì)領(lǐng)域的研究熱點(diǎn)。

由于商用芯片向著高密集度、低操作電壓的方向迅速發(fā)展,使得它們?cè)诳臻g輻射環(huán)境下的可靠性大大降低。其中軟故障是主要故障,它是由帶電粒子和PN結(jié)相互作用引起的一種暫態(tài)故障,可造成芯片嚴(yán)重的運(yùn)行錯(cuò)誤[1]。所以如何彌補(bǔ)商用芯片本身抗輻照能力的不足是需要解決的重要問(wèn)題。

國(guó)內(nèi)外研究機(jī)構(gòu)對(duì)于星載信號(hào)處理平臺(tái)抗SEU方法目前主要分為兩類(lèi):一類(lèi)是針對(duì)SEU的屏蔽,包括各種抗SEU加固結(jié)構(gòu)設(shè)計(jì)、高性能抗SEU的CMOS(Complementary Metal Oxide Semiconductor)工藝等[2];另一類(lèi)是針對(duì)SEU的修復(fù),如動(dòng)態(tài)可重構(gòu)技術(shù)、編碼糾正[3]等方法。另外,由于星載平臺(tái)中包含大量的諸如FIR(Finite Impulse Response)濾波和FFT(Fast Fourier Transform)的處理過(guò)程,故近年來(lái)針對(duì)各種濾波器和信號(hào)處理算法本身抗SEU的方法研究特別廣泛,如文獻(xiàn)[4]、文獻(xiàn)[5]分別實(shí)現(xiàn)FIR濾波器和FFT算法的容錯(cuò)技術(shù)。

相對(duì)于上述研究思路,本文則重點(diǎn)關(guān)注芯片內(nèi)部各種不同硬件資源對(duì)于SEU事件的敏感性。以星載平臺(tái)上應(yīng)用廣泛的SRAM型FPGA為研究對(duì)象,通過(guò)模擬星載平臺(tái)和故障注入的實(shí)驗(yàn),根據(jù)各種資源在故障源注入后誘發(fā)系統(tǒng)出現(xiàn)功能紊亂的概率總結(jié)出各種資源對(duì)于SEU敏感性高低的結(jié)論。

1 SEU敏感性研究模型

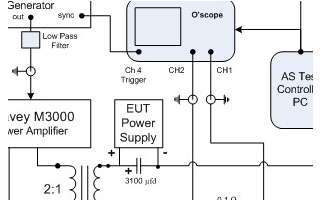

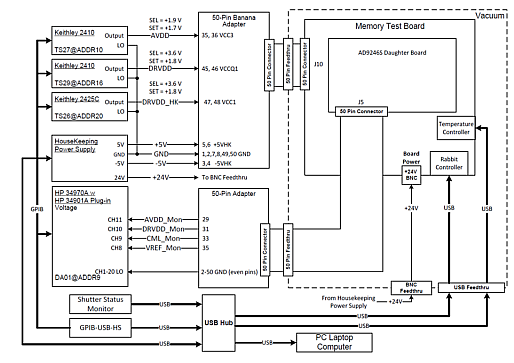

為驗(yàn)證SRAM型FPGA不同資源對(duì)于SEU存在不同的敏感性,需要模擬星載信號(hào)處理平臺(tái)SRAM型FPGA在外部空間遭遇SEU效應(yīng)的整個(gè)過(guò)程。即在地面上模擬采用SRAM型FPGA的星載信號(hào)處理平臺(tái),模擬FPGA出現(xiàn)的SEU錯(cuò)誤,以及將模擬的SEU錯(cuò)誤注入到FPGA內(nèi)部不同資源中。據(jù)此提出SEU敏感性研究的模型,如圖1所示。

?

根據(jù)研究模型,首先可以采用基于商用芯片的星地聯(lián)合處理平臺(tái)來(lái)模擬星載平臺(tái),其硬件環(huán)境如圖2所示。其中CPCI(Compact Peripheral Component Interconnect)總線用來(lái)模擬星地鏈路,星載處理板模擬星載信號(hào)處理平臺(tái),處理板采用了多片SRAM型FPGA芯片作為實(shí)驗(yàn)的測(cè)試芯片。

?

為調(diào)用FPGA內(nèi)部資源,采用兩種功能相同但實(shí)現(xiàn)方式不同的功能模塊,因此可以針對(duì)兩種模塊設(shè)計(jì)顆粒度不同的實(shí)驗(yàn)A和實(shí)驗(yàn)B來(lái)分別進(jìn)行實(shí)驗(yàn)。基于功能模塊通過(guò)故障注入的方式生成模擬的SEU錯(cuò)誤,在系統(tǒng)正常運(yùn)行的情況下,將錯(cuò)誤注入到平臺(tái)FPGA的功能模塊中,觀察注入前后的輸出狀態(tài),對(duì)比兩次實(shí)驗(yàn)結(jié)果,得出SEU敏感性研究的結(jié)論。

2 SEU敏感性實(shí)驗(yàn)設(shè)計(jì)

2.1 基于IP核的FFT敏感性實(shí)驗(yàn)設(shè)計(jì)

通常星載平臺(tái)中擁有大量的FFT運(yùn)算,而這些運(yùn)算大都通過(guò)在FPGA中調(diào)用IP核來(lái)實(shí)現(xiàn)。因此以基于IP核的FFT來(lái)進(jìn)行SEU敏感性實(shí)驗(yàn)是合理的。SRAM型FPGA芯片由6個(gè)部分組成,其中Slice資源是可編程邏輯單元的基本邏輯單元,RAM資源是FPGA常用的硬核模塊,兩種資源都是FPGA內(nèi)部廣泛分布且應(yīng)用較多的資源。所以基于IP核的FFT敏感性實(shí)驗(yàn)所針對(duì)的資源就是Slice和RAM。

Slice資源內(nèi)部主要的配置關(guān)系是邏輯關(guān)系,即“+”、“~”、“*”關(guān)系;RAM資源內(nèi)部主要的配置關(guān)系是數(shù)值關(guān)系,即0、1數(shù)值關(guān)系。所以針對(duì)這兩種資源的故障注入將分別圍繞這兩種配置關(guān)系進(jìn)行修改。利用FPGA_Editor查看網(wǎng)表文件,并對(duì)其進(jìn)行修改,生成差異比特文件,即模擬故障源。在FFT模塊正常運(yùn)行后通過(guò)測(cè)試電腦經(jīng)模擬星地鏈路,反復(fù)將故障源注入到FFT模塊中,通過(guò)chipscope抓取結(jié)果,根據(jù)結(jié)果得出結(jié)論。

2.2 基于軟件實(shí)現(xiàn)的FFT敏感性實(shí)驗(yàn)設(shè)計(jì)

為進(jìn)一步驗(yàn)證上述結(jié)論,在前述實(shí)驗(yàn)的基礎(chǔ)上,設(shè)計(jì)了另一種顆粒度更高的實(shí)驗(yàn)來(lái)加以證明。該實(shí)驗(yàn)運(yùn)用VHDL語(yǔ)言編程實(shí)現(xiàn)16點(diǎn)的FFT功能模塊,該模塊調(diào)用更多的FPGA資源,采用相同的星地聯(lián)合處理平臺(tái),同樣針對(duì)Slice和RAM兩種資源進(jìn)行故障注入實(shí)驗(yàn)。

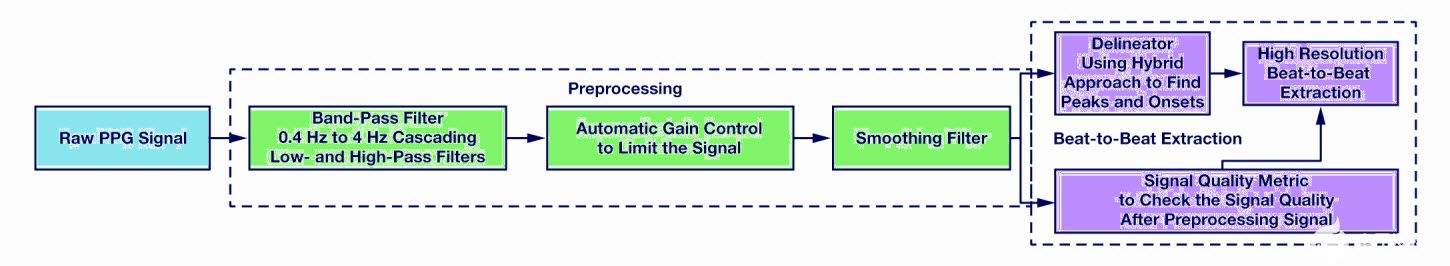

設(shè)16點(diǎn)數(shù)據(jù)為x(0)、x(1)…x(15)的16位的實(shí)數(shù)數(shù)據(jù),按時(shí)間抽取的基2 FFT算法原理可得該16點(diǎn)FFT的蝶形交織運(yùn)算,如圖3所示,其結(jié)果即是X(0)~X(15)的16點(diǎn)FFT輸出。由圖可知,該FFT算法原理的核心是每一層的蝶形交織運(yùn)算,因此整個(gè)16點(diǎn)FFT程序設(shè)計(jì)的關(guān)鍵是四層的蝶形交織運(yùn)算。

?

設(shè)計(jì)程序分成五部分,即頂層的輸入輸出和4個(gè)蝶形交織層。最初輸入16點(diǎn)的16位實(shí)數(shù)數(shù)據(jù),然后通過(guò)每層的蝶形交織計(jì)算得到最終FFT的輸出。將結(jié)果與MATLAB仿真進(jìn)行對(duì)比,驗(yàn)證該FFT模塊是否編寫(xiě)正確。確認(rèn)模塊功能正確后,同樣針對(duì)Slice和RAM進(jìn)行修改;然后進(jìn)行故障注入試驗(yàn),通過(guò)chipscope抓取結(jié)果;最后根據(jù)結(jié)果得出結(jié)論。

3 SEU敏感性實(shí)驗(yàn)及分析

3.1 基于IP核的FFT敏感性實(shí)驗(yàn)及分析

通過(guò)FPGA_Editor可得知IP核FFT模塊擁有1 227個(gè)Slice、17個(gè)RAM資源。將1 227個(gè)Slice資源中每連續(xù)的20個(gè)左右分為一組,共分為60組。對(duì)每一組資源中的每一個(gè)Slice都在數(shù)量為10處進(jìn)行邏輯修改。將17個(gè)RAM資源劃為17組,對(duì)每一個(gè)RAM分別進(jìn)行數(shù)量統(tǒng)一為10處的數(shù)值修改。最后得到60個(gè)Slice和17個(gè)RAM的差異比特文件,并對(duì)每一個(gè)差異比特文件進(jìn)行100次的反復(fù)注入。

3.1.1 實(shí)驗(yàn)結(jié)果

針對(duì)Slice資源的故障注入結(jié)果分為四個(gè)程度,分別如圖4~圖7所示。所有60組試驗(yàn)中只有4組結(jié)果正確,其余組都出現(xiàn)各種錯(cuò)誤。

?

?

針對(duì)RAM資源的故障注入結(jié)果分為三個(gè)程度,如圖4、圖8和圖9所示。所有試驗(yàn)中只有4組出現(xiàn)錯(cuò)誤。

?

3.1.2 實(shí)驗(yàn)結(jié)論

(1)在Slice顆粒度約為20個(gè)一組、共60組的情況下,根據(jù)大量反復(fù)注入的試驗(yàn)結(jié)果,利用統(tǒng)計(jì)數(shù)據(jù)可得針對(duì)Slice資源故障注入后模塊的故障率為:θ1=(56/60)×100%=93.3%;針對(duì)RAM資源故障注入后的故障率為:θ2=(4/7)×100%=23.5%。故在SEU效應(yīng)敏感度上,Slice強(qiáng)于RAM。

(2)試驗(yàn)中每組故障注入的數(shù)量一致,但注入的位置各不相同。通過(guò)每組最后的結(jié)果對(duì)比可知,不同位置的故障注入將對(duì)模塊產(chǎn)生不同程度的影響。

(3)在77組故障注入試驗(yàn)中,結(jié)果是邏輯修改引起的模塊故障率更高。故SEU造成邏輯上的故障對(duì)整個(gè)模塊影響要明顯強(qiáng)于數(shù)值故障造成的影響。

3.2 基于軟件實(shí)現(xiàn)的FFT敏感性實(shí)驗(yàn)及分析

為了驗(yàn)證該編寫(xiě)的FFT模塊功能正確,首先在MATLAB中實(shí)現(xiàn)FFT算法,然后將其每層蝶形交織結(jié)果與VHDL程序的每一層蝶形交織結(jié)果進(jìn)行對(duì)比。對(duì)比輸出結(jié)果如圖10所示,左側(cè)為MATLAB仿真結(jié)果,右側(cè)為VHDL程序運(yùn)行結(jié)果。

?

由對(duì)比可知,VHDL程序運(yùn)行結(jié)果與MATLAB仿真吻合,證明該程序具備正確的FFT功能,可作為本次實(shí)驗(yàn)的模塊。通過(guò)FPGA_Editor可知,生成的FFT模塊擁有2 265個(gè)Slice、2個(gè)RAM資源。

與前述實(shí)驗(yàn)類(lèi)似,將該FFT中的2 265個(gè)Slice資源每連續(xù)的10個(gè)左右分為一組,共分為240組,對(duì)每個(gè)Slice進(jìn)行數(shù)量為10處的故障注入;將2個(gè)RAM資源劃為2組,對(duì)每個(gè)RAM進(jìn)行數(shù)量10處的數(shù)值修改。最后生成240個(gè)Slice和2個(gè)RAM差異比特文件,并對(duì)每個(gè)文件進(jìn)行100次的反復(fù)注入。

3.2.1 實(shí)驗(yàn)結(jié)果

針對(duì)Slice資源試驗(yàn),所有試驗(yàn)中有32組結(jié)果正確,其余出現(xiàn)明顯錯(cuò)誤,如圖11所示。針對(duì)RAM資源的試驗(yàn)結(jié)果2組都正確,如圖12所示。

?

3.2.2 實(shí)驗(yàn)結(jié)論

(1)本次實(shí)驗(yàn)在前述實(shí)驗(yàn)的基礎(chǔ)上將Slice測(cè)試顆粒度提高1倍,試驗(yàn)組數(shù)提高4倍。由大量反復(fù)注入的試驗(yàn)結(jié)果,利用統(tǒng)計(jì)數(shù)據(jù)可得針對(duì)Slice注入模塊故障率為:θ1=(208/240)×100%=86.7%;針對(duì)RAM資源故障注入后的FFT模塊故障率為:θ2=(0/2)×100%=0%。所以有θ1>θ2,故在SEU效應(yīng)敏感度上,Slice強(qiáng)于RAM。

(2)每組故障注入的數(shù)量相同,但位置不同。結(jié)果發(fā)現(xiàn)不同位置的注入對(duì)模塊產(chǎn)生不同程度的影響。

(3)該次實(shí)驗(yàn)依然是針對(duì)Slice資源進(jìn)行邏輯修改,針對(duì)RAM資源進(jìn)行數(shù)值修改。從結(jié)果來(lái)看,依然是邏輯的錯(cuò)誤對(duì)整個(gè)模塊的影響強(qiáng)于數(shù)值錯(cuò)誤。

4 結(jié)論

本文重點(diǎn)分析芯片內(nèi)部不同硬件資源對(duì)于SEU效應(yīng)敏感性的問(wèn)題。以SRAM型FPGA為研究對(duì)象,設(shè)計(jì)進(jìn)行了兩種顆粒度不同的故障注入實(shí)驗(yàn)。結(jié)果表明,在FPGA內(nèi)部資源中,Slice資源對(duì)于SEU效應(yīng)的敏感性很強(qiáng),RAM相對(duì)較弱。SEU效應(yīng)引起的邏輯錯(cuò)誤比數(shù)值錯(cuò)誤更能誘發(fā)系統(tǒng)的功能紊亂。所以,可針對(duì)FPGA中占用Slice資源較多的模塊進(jìn)行防護(hù),重點(diǎn)針對(duì)邏輯錯(cuò)誤進(jìn)行防護(hù)。

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論