摘要:為了實現對某航天器在地面及飛行過程中的超聲數據進行高精度、高速采集的功能,根據測量系統的技術要求,設計數據采集裝置的硬件電路和時序控制邏輯。為了滿足惡劣的環境測試要求,設計采用高速、高精度、寬溫度范圍的THS1408模數轉換器。選取高速運放AD8028 進行信號調理,以FPGA 作為邏輯控制器,控制THS1408 進行模數轉換。經測試,采集精度優于0. 5%,滿足實際工程需要,具有很高的可靠性,已成功應用于該測量系統。

隨著數字化技術不斷深入的今天,數據采集技術已經成為信號處理過程中的重要環節。數據采集技術已經廣泛應用于雷達、聲納、瞬態信號測試、無線探傷、航空、航天等諸多領域[1-2] 。隨著數據采集技術應用的不斷加深,不僅對數據采集裝置的采集精度、采集速度和數據量有了更高的要求,還要求數據采集裝置能夠在惡劣環境條件下可靠的工作[3] 。而模數轉換芯片性能的優劣對數據采集會產生最直接的影響,因此,本設計在實際應用的背景下,根據測量系統的技術要求,通過合理的選取高速、高精度、寬溫度范圍的THS1408 模數轉換器,優化數據采集裝置的電路設計和時序設計,以實現超聲數據采集裝置的功能。

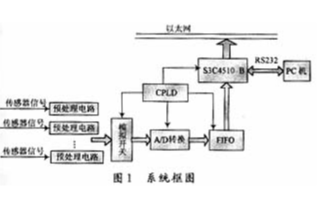

1 整體設計方案

超聲數據采集裝置的整體設計框圖如圖1 所示。輸入的超聲信號是經過傳感器轉換過的電壓模擬信號(0 ~5 V),電壓信號經過傳感器信號輸入接口進入信號調理電路, 調理后的輸入信號經過THS1408 前的單端轉差分電路后轉換為差分信號,THS1408 在FPGA 芯片的邏輯控制下,將差分信號進行模數轉換,模數轉換后的數字量經過內部程序進行數據處理后緩存入外部FIFO 中,再將FIFO 中的有效數據編幀、存儲在16 Gflash 存儲陣列中。超聲數據采集裝置通過總線接口進行板間通信:接收上位機指令,上傳數據和裝置狀態。

圖1超聲數據采集裝置的整體設計框圖

2 THS1408 功能簡介

測量系統要求超聲數據采集裝置的單通道采樣率為5 Msample/ s,分辨率為12 位,采樣精度小于0.5%,保留8 位有效數據位,采集裝置的工作溫度

范圍為-50℃~125 ℃,模數轉換芯片功耗小于500mW。為了滿足超聲數據采集裝置的技術指標,設計選用了德州儀器的THS1408 模數轉換器,THS1408 具有以下功能特點:

(1)采樣速率高:3 Msample/ s ~8 Msample/ s 采樣率;

(2)工作溫度范圍寬:-55 ℃~125 ℃;

(3)功耗低:典型功耗為270 mW,最大功耗為360 mW;

(4)14 位分辨率;

(5)差分輸入接口;

(6)可編程輸入增益;

(7)單電源供電;

(8)片內集成高性能的采樣保持放大器和參考電壓源。

THS1408 在寬溫帶、強振動的環境下,能夠滿足測量系統的技術要求,且具有很好的性價比和功耗/速度比[4] 。

THS1408 的采樣內核采用的是一個延時9. 5 個采樣周期的循環采樣結構,信號開始采樣后的9. 5個時鐘周期后,轉換結果開始輸出,THS1408 采用具有三態緩沖的并行數據接口,可以直接連接到數據總線接口,通過驅動OE 為低可以將數據輸出使能,使得電路設計更加簡單。采樣時序如圖2 所示。時鐘頻率為5 MHz,時鐘上升沿采樣,下降沿輸出數字量,數據輸出延時td =25 ns。

圖2THS1408 采樣時序圖

3 超聲采集電路設計與分析

超聲采集電路主要由兩部分組成:信號調理電路、單端轉差分電路和模數轉換電路。電路原理圖如圖3 所示,信號調理電路的功能是對輸入信號進

行運放跟隨調理以及接口保護,R13 為接口保護電阻,單端轉差分電路將輸入信號轉為差分信號,滿足THS1408 轉換的輸入信號要求,模數轉換電路為:FPGA 芯片控制THS1408 完成模數轉換部分[5] 。

圖3 超聲采集電路原理圖

輸入的超聲信號是經過傳感器轉換成電壓量的模擬信號(0 ~5 V),輸入信號頻率不大于1. 5 MHz,設計擬采用-3 dB 帶寬為16 MHz 的AD823 進行運放跟隨,在電路調試的過程中,當信號頻率達到500 kHz時,經過AD823 運放跟隨后信號出現明顯失真現象,運放跟隨前后波形如圖4 所示(通道1 為跟隨前波形)。為了解決高頻信號經過運放跟隨后波形失真的現象,設計采用低失真率、-3 dB 帶寬為190 MHz 的AD8028 替換AD823,經過AD8028 進行運放前后的測試波形如圖5 所示(通道1 為跟隨前波形)。電路采用AD8028 以后, 當信號頻率達到最大要求(1. 5MHz)時,運放跟隨后的波形效果仍然很好,失真幾乎可以忽略不計,大大提高了信號采樣的精度[6-7] 。

由于THS1408 的模擬信號輸入接口采用差分形式,而輸入信號為單端模擬信號,所以需要對輸入信號進行單端轉差分處理。THS1408 芯片資料推薦了兩種單端轉差分的電路:變壓器耦合和單端配置方式單端轉差分電路。變壓器耦合單端轉差分電路雖然精度較高,抗干擾能力較好,但是電路比較復雜,而且功耗較高;單端配置方式單端轉差分電路簡單,容易實現,功耗較低,能夠滿足采樣精度要求,綜合考慮,設計采用單端配置方式的單端轉差分電路,電路設計如圖3 中運放跟隨和THS1408 之間的電路。

圖4AD823 運放跟隨前后波形

圖5 AD8028 運放跟隨前后波形

芯片資料推薦電路中R12 為10 K,在實際電路調試過程中,AD 運放的容性負載隨著輸入信號頻率的增大不斷減小,當輸入信號頻率達到1 MHz 以上時,根據AD8028 的輸入電容值C =和容性負載計算公式:

系統要求采集的有效數據位為8 位, 根據THS1408 芯片資料可知:駐VIN 的范圍為-2 V ~ 2 V,對應的AD14 位編碼為0 ~16 383,編碼方式設置為

線性二進制。為了實現有效編碼的全范圍覆蓋,即輸入電壓范圍為0 ~5 V 時,采集的有效對應編碼為0 ~255,設計駐VIN 最值差為0. 5 V,對應的AD14 位編碼差值為2 048,通過FPGA 內部程序將模數轉換的高11 位編碼進行轉換處理:如果高11 位編碼大于“10111001100冶,則有效對應編碼值為255;如果高11 位編碼小于“10011001100冶,則有效對應編碼值為0; 其他情況下, 高11 位編碼減去零位值(10011001100)后,取低8 位數據為采集的有效對應編碼。經過內部程序處理后,輸入電壓范圍為0 ~5 V 時,采集的有效對應編碼為0 ~ 255,最后對采集的有效數據進行編幀、打包和儲存。

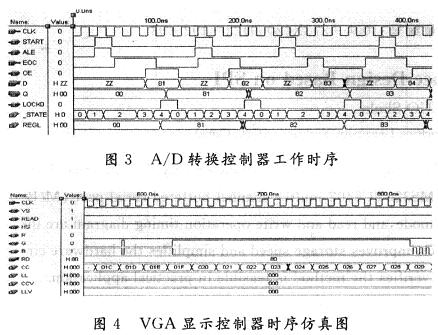

4 時序邏輯設計

設計采用Xilinx 公司的FPGA 芯片作為時序邏輯控制器[8-9] ,根據THS1408 的采樣時序和采樣率確定AD 采集時序如圖6 所示。系統時鐘CLK 頻率為60 MHz,AD 采樣時鐘ad_clk 為6 MHz,系統上電后,FPGA 按照THS1408 的寫時序對THS1408 的增益寄存器、偏移寄存器、控制寄存器進行初始化配置,增益設置為1,偏移校正值設置為0,THS1408 工作模式設置為:普通工作模式、內部參考電壓、線性二進制編碼方式。當上位機下發超聲數據采集命令時,采集裝置進入數據采集狀態,通過對系統時鐘進行計數分頻產生AD 采樣時鐘ad_clk,對輸入信號進行采樣和數據轉換,再通過控制數據輸出使能out_oe 輸出轉換的14 位數字量,數字量經過內部數據處理緩存入外部FIFO 中,再將FIFO 中的有效數據編幀存儲在16 GFlash 存儲陣列中[10] 。當上位機下發讀取超聲數據命令時,超聲數據采集裝置將Flash 中的有效數據通過總線接口上傳到上位機進行數據處理。

圖6 AD 采集時序

5 功能驗證

將超聲數據采集裝置接入測試系統,對超聲數據采集裝置進行功能測試。在模擬的工作環境下,通過地面測試臺為采集裝置提供3 V 直流量,上位機軟件將超聲數據采集裝置采回的數據進行數據處理和分析,數據的幀校驗準確無誤,對分解后的數據進行繪圖。

經過功能驗證,超聲數據采集裝置滿足實際工程的要求,能夠可靠的對超聲數據進行采集。本設計只介紹了單通道的超聲數據采集,在單通道的基礎上,增加多路采集電路設計和調整AD 的采集時序可以實現多通道數據采集,這里就不做介紹了。

電子發燒友App

電子發燒友App

評論