美國賽靈思(Xilinx)2012年4月5日使用28nm工藝制造的FPGA “Virtex-7 X690T”演示了有線通信系統(背板)。該FPGA配備有80個以最大13.1Gbit/秒的速度工作的高速串行收發器“GTH”,已于2012年

2012-04-09 11:13:59 2848

2848 xilinx的7系列FPGA根據不同的器件類型,集成了GTP、GTX、GTH以及GTZ四種串行高速收發器,四種收發器主要區別是支持的線速率不同,圖一可以說明在7系列里面器件類型和支持的收發器類型以及

2020-11-20 12:08:15 17712

17712

FPGA GTP收發器設計指導疑問描述測試表明,Spartan-6 FPGA的GTP收發器有可能受到臨近bank中用戶管腳的干擾。因此,賽靈思針對bank0和bank2中管腳的使用提出了一些新的建議

2016-08-25 09:46:38

針對bank0和bank2中管腳的使用提出了一些新的建議。本文中的使用建議目的在于盡量減小用戶管腳對GTP收發器的影響。在所有情況下,利用Spartan - 6 FPGA的SSO準則仍然需要遵循

2017-03-21 14:34:27

FPGA高速收發器設計原則高速FPGA設計收發器選擇需要考慮的因素

2021-04-09 06:53:02

高速收發器(SERDES)的運用范圍十分廣泛,包括通訊、計算機、工業和儲存,以及必須在芯片與芯片/模塊之間、或在背板/電纜上傳輸大量數據的系統。但普通高速收發器的并行總線設計已無法滿足現在的要求。將收發器整合在FPGA中,成為解決這一問題的選擇辦法。FPGA高速收發器設計時,我們需要注意哪些事項呢?

2019-08-07 06:26:42

技術開發的廣闊前景。Xilinx公司在推出的Virtex-5 FPGA以及配套的Virtex-5 RocketIOTM GTP收發中開始支持多種協議,如SATA2.0傳輸協議。SATA(Serial

2018-12-11 11:04:22

RocketIO收發器怎么實現高速通信?

2021-05-26 06:28:57

RocketIO高速串行接口本人在北京工作6年以上,從事FPGA外圍接口設計,熟練使用Virtex-5/Virtex-6 FPGA,非常熟悉RocketIO GTP/GTX協議,Aurora協議

2014-03-01 18:46:35

、體積小、無中繼、傳輸距離長等優點得到了廣泛的應用,光纖收發器正是利用了光纖這一高速傳播介質很好的解決了以太網在傳輸方面的問題。那么,我們對這個名詞也來做個解釋吧。光纖收發器,是一種將短距離的雙絞線

2014-04-30 17:28:08

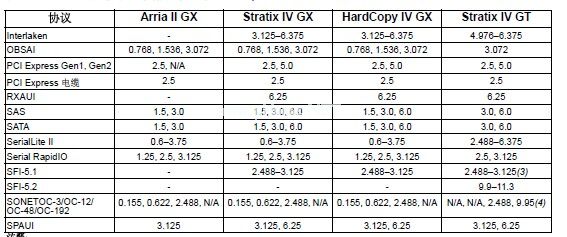

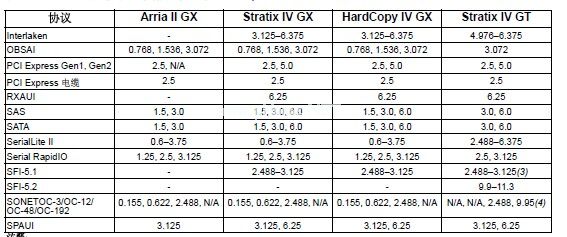

在低成本的 FPGA 中,Cyclone? IV GX 器件內嵌多達八個全雙工收發器,運行在 600Mbps 到 3.125 Gbps 的串行數據速率上。 表 1-1 列出了 Cyclone IV GX 收發器通道所支持的串行協議信息。

2017-11-14 10:54:41

嗨,我正在使用ARTIX 7 FGG676,Transciever的示例參考設計 - GTP - 如UG769中所述。我為SATA2.0配置了兩個這樣的收發器,將它們連接在一起并成功地在它們之間來回

2020-07-31 10:20:29

嗨,可以告訴我MGT,GTP,GTX收發器之間的區別嗎?Rocketio屬于MGT還是GTP組?

2020-03-10 08:51:53

Express Master DMA Read --> DDR2/DDR3內存 --> 光纖/RocketIO GTP接口.3. 寄存器訪問:軟件訪問FPGA內部與DMA傳輸相關的寄存器.4.

2012-05-21 09:32:15

海 任何人都可以解釋Virtex 5(ML 506)中的GTP及其規格以及MGT和GTP收發器之間的區別。

2019-08-14 10:01:43

`描述PMP9408 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌。它利用一個 PMBus 接口來實現電流

2015-05-11 10:30:22

設計GTXGTH收發器電源設計1.概述Xilinx 7系列FPGA GTX/GTH收發器是模擬電路,當設計和實現PCB設計需要特殊考慮和注意。這其中涉及器件管腳功能、傳輸線阻抗和布線、供電設計濾波、器件選擇、PCB布線和層疊設計相關內容。2.管腳描述和設計指導2.1 GTX/GTH收發器管腳描述

2021-11-11 07:42:37

我正在使用spartan6 gtp收發器向導。但沒有外部時鐘。相反,我使用時鐘向導使用200 M振蕩器生成所需的速率。我嘗試使用chipcope測試示例設計,但錯誤計數信號正在增加gradullay。誰能幫幫我嗎?

2019-08-06 10:47:32

我之前在CSDN上查到的資料都顯示FPGA需要連接一個獨立CAN控制器,如SJA1000再去連CAN收發器。請問我能直接把FPGA的引腳直接連在CAN收發器的TX、RX上嗎?如果不能原因又是什么?

2018-10-10 09:25:39

一、概述

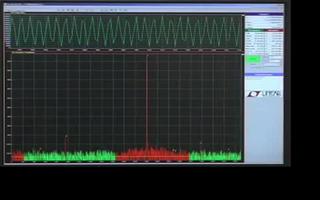

IBERT(集成誤碼率測試儀)是xilinx為7系列FPGA GTX收發器設計的,用于評估和監控GTX收發器。IBERT包括在FPGA邏輯中實現的模式生成器和檢查器,以及對端口的訪問

2023-06-21 11:23:12

你好,關于GTP / GTX收發器的JTAG實現,我有幾個問題。1. JTAG是否針對GTP / GTX收發器實現(因此可以驅動和讀取引腳以進行電路板驗證)2. JTAG組件放在GTP磁貼中的哪個

2020-06-18 14:41:02

)經過CPRI接口傳輸。3 FPGA實現CPRI協議傳輸方案3.1 基本方案用FPGA實現CPRI協議傳輸具有以下2種方案。(1) 方案一RocketIO收發器的FPGA來實現CPRI協議的光纖通信

2019-06-04 05:00:18

)經過CPRI接口傳輸。3FPGA實現CPRI協議傳輸方案3.1基本方案用FPGA實現CPRI協議傳輸具有以下2種方案。(1) 方案一RocketIO收發器的FPGA來實現CPRI協議的光纖通信[3

2019-05-31 05:00:06

精準的數據收發信息,更好的為工程項目服務。傳統的并行傳輸方式由于走線多、信號間串擾大等缺陷,無法突破自身的速度瓶頸。而串行傳輸擁有更高的傳輸速率但只需要少量的信號線,降低了板開發成本和復雜度,滿足高頻率遠距離的數據通信需求,被廣泛應用到各種高速數據通信系統設計中。

2019-10-21 06:29:57

高速差分IO信號的基礎知識: 1、初步認識GTX 當你接觸到FPGA的高速串行通信時,比如GTX收發器,一條TX發送線,一條RX接收線,這時候你肯定會聯想到UART串口,UART串口通信多么簡單

2018-08-16 09:59:19

高速LVDS數據傳輸方案和協議基于FPGA的高速LVDS數據傳輸本人在北京工作6年,從事FPGA外圍接口設計,非常熟悉高速LVDS數據傳輸,8B/10B編碼等,設計調試了多個FPGA與FPGA以及

2014-03-01 18:47:47

每對電源和地引腳都要良好旁路。5 結論本文給出了基于FPGA高速數據采集系統中的輸入輸出接口的實現,介紹了高速傳輸系統中RocketIO設計以及LVDS接口、LVPECL接口電路結構及連接方式,并在

2018-12-18 10:22:18

串行通信要求的傳輸線少,可靠性高,傳輸距離遠,被廣泛應用于計算機和外設的數據交換。通常都由通用異步收發器(UART)來實現串口通信的功能。在實際應用中,往往只需要UART的幾個主要功能,專用的接口

2011-09-09 09:10:09

的關鍵技術是嵌入式RocketIO GTP低功耗串行收發器。最大的Virtex-5LXTFPGA中最高可包含24個串行收發器,每個串行收發器的運行速率范圍均為100Mbps至3.2Gbps。結合可編程

2019-04-12 07:00:11

FPGA的關鍵技術是嵌入式RocketIO GTP低功耗串行收發器。最大的Virtex-5LXTFPGA中最高可包含24個串行收發器,每個串行收發器的運行速率范圍均為100Mbps至3.2Gbps。結合

2019-04-16 07:00:07

,支持PCI Express Gen2(5Gbps/lane); ?支持64bit DDR3-1600,容量1GByte; ?該FPGA內嵌16個高速串行收發器RocketIO GTX; ?4個

2014-11-24 15:31:02

,pin_to_pin兼容FPGAXC7K410T-2FFG900,支持8-Lane PCIe、64bit DDR3、四路SFP+連接器、四路SATA接口、內嵌16個高速串行收發器RocketIO GTX,軟件

2015-01-28 15:48:55

如果系統精度、效率和可靠性至關重要,那么設計傳感器節點無線數據傳輸以用于遠程監控就會是一個相當大的挑戰。而溶液的pH值是許多行業需要考慮的一種測量,今天我們分享的參考設計的目的是評估pH玻璃探針的特性,從而解決硬件和軟件設計的不同挑戰,并提出一種利用射頻收發器模塊從探針無線傳輸數據的解決方案。

2019-07-19 07:34:37

我使用了Virtex 5系列芯片XC5VSX95T。我使用了GTP模塊,實現了快速IO通信,3.125Gbps。然后,出現了問題.FPGA可以通過Rapid IO與FPGA進行通信,通信速率高達

2020-06-19 08:53:14

嗨,我正在嘗試使用spartan 3E FPGA(成本因素)實現千兆以太網接口。由于斯巴達系列中沒有RocketIO收發器,因此我們必須使用LVDS TBI接口。有沒有人有實施這個經驗?你能給我一些

2019-08-07 09:38:25

ASIC系統。 使用USB協議棧知識產權(IP)及外部收發器 在第一種方法中,我們可以在FPGA或ASIC中實現SIE(見圖3)。圖3 FPGA + USB協議棧IP + USB收發器 SIE IP

2012-11-22 16:11:20

嗨,有沒有辦法在V5的GTP收發器中進行串行環回模式?手冊提供了4種環回模式,但它們都涉及解串器之后的路徑,我需要通過接收器循環串行數據并在CDR之后將其路由到發送器,而不通過重新鎖定的并行路徑。這可能嗎?謝謝,戴夫

2020-05-27 17:17:02

嗨,大家好,我正在嘗試在我的vhdl設計中實現GTP收發器。該設計應該用作兩個定制硬件板之間的連接測試。它使用線性反饋移位寄存器來生成比特流,該比特流被打包到數據幀中。在通過鏈路發送幀之前,發送對齊

2019-07-24 14:10:28

Virtex-5LXT FPGA的關鍵技術是嵌入式RocketIO GTP低功耗串行收發器。最大的Virtex-5LXTFPGA中最高可包含24個串行收發器,每個串行收發器的運行速率范圍均為

2019-05-05 09:29:30

本文在對Virtex-5 RocketIOTM GTP進行了解的基礎上,針對串行高速接口開發中位寬不匹配的問題,提出了一種位寬轉換方法,以解決Virtex-5 RocketI0TM GTP無法直接應用于某些串行高速接口開發的問題,并就SATA2.0接口開發中該問題的解決方案進行詳細闡述。

2021-05-28 06:21:43

本文給出了基于FPGA高速數據采集系統中的輸入輸出接口的實現,介紹了高速傳輸系統中RocketIO設計以及LVDS接口、LVPECL接口電路結構及連接方式,并在我們設計的高速數傳系統中得到應用。

2021-04-29 06:04:42

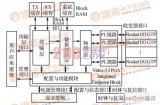

本文介紹了基于Xilinx Virtex-6 FPGA的高速串行數據傳輸系統的設計與實現,系統包含AXI DMA和GTX串行收發器,系統增加了流量控制機制來保證高速數據傳輸的可靠性。最后進行了仿真測試,測試結果顯示系統可以高速可靠地傳輸數據。

2021-05-25 06:45:36

怎么實現基于MRF24J40的IEEE802154無線收發器電路方案設計?

2021-05-25 07:00:15

實現4字節的Aurora通信嗎?第二個問題......我怎樣才能找到哪個GTP或GTX收發器連接到SFP,哪個不連接。我在計劃中迷失了方向。謝謝。問候,的Ondrej

2019-09-06 10:39:10

是否可以在不使用GTP / GTX收發器的情況下從Virtex-5中的數據信號中恢復時鐘?該數據使用差分信令并具有NRZ編碼(例如,8b / 10b)。不幸的是,輸入引腳沒有連接到高速收發器,所以

2020-06-08 14:50:56

親愛的所有人,1。是否有人有關于使用Virtex 5 Rocket GTP收發器為SATA創建物理層的信息?2.并且我不了解火箭GTP中的元素RX終止和均衡,它決定了輸入的高速差分信號的值。如果有

2018-09-30 11:06:24

求助FPGA高速串行收發器,輸出12.5Gbps的信號要用什么電平輸出28.5Gbps的信號要用什么電平?

2014-11-10 09:12:51

UG196的第83頁注1,Virtex-5 FPGA RocketIO GTP收發器用戶指南,2.1版,“采購GTP_DUAL磁貼上方的GTP_DUAL磁貼數量不得超過3個”。如果我有LX110

2020-06-04 11:49:37

描述PMP9463 參考設計提供為 Xilinx Ultrascale? Kintex? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌。它利用一個 PMBus 接口來實現電流和電壓

2018-08-10 09:36:45

什么是解復用電路?解復用電路在高速收發器中的應用是什么?

2021-05-19 06:24:03

親愛的先生我試圖在Artix-7中使用GTP傳輸串行數據。遺憾的是,由于串行數據流包含一些抖動,Artix-7 GTP接收器中有時會出現數據錯誤。另一方面,收發器參考時鐘是干凈的。我想我應該提高

2020-08-24 09:44:56

從FPGA1中的GTP傳輸到FPGA2中的GTP。每個FPGA都有自己的本地收發器參考振蕩器。我有兩個目標,我想要實現:頻率匹配FPGA1和FPGA2上的TXOUTCLK,和即使在重新編程FPGA之后

2020-08-28 06:22:25

收發器。無論如何,我的問題如下:我可以使用這些SMA連接器(連接到rocketIO引腳),而無需使用FPGA的內部傳輸器嗎?要恢復,我想使用那些SMA連接器,但不使用ROAKEIO收發器,因為我有一個外置的?謝謝您的回復。再見

2019-09-04 11:26:58

作為第二個Spartan 6上的收發器來響應回送數據。截至目前,我可以傳輸Master 2 GTP收發器。 Slave GTP適當地響應并發回數據。在GTP_DUAL塊中的某處,看起來好像已啟用通道

2019-08-02 06:59:30

Virtex-5 RocketI0TM GTP是Xilinx公司根據高速串行接口開發市場對高性能GTP的特殊要求而開發的一款具有通用性、易用性、低功耗和低成本特性的GTP收發器。文章針對Virtex-5 RocketIOTM GTP收發

2010-07-22 17:08:27 30

30 利用RocketIO高速串行傳輸模塊將數字圖像和控制指令串行化,實現對高幀頻、多通道數字圖像的高速遠程傳輸和反饋控制。利用Virtex2II Pro系列FPGA設計的光纖數字圖像傳輸模塊,可將

2010-09-22 08:34:12 36

36 摘 要:介紹了FPGA最新一代器件Virtex25上的高速串行收發器RocketIO。基于ML505開發平臺構建了一個高速串行數據傳輸系統,重點說明了該系統采用RocketIO實現1. 25Gbp s高速串行傳輸的設

2010-09-22 08:41:18 43

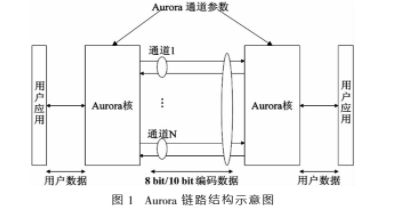

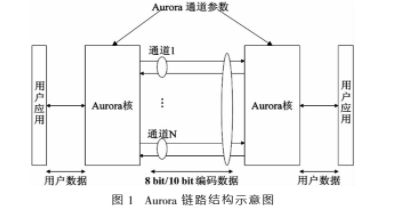

43 摘要: 串行傳輸技術具有更高的傳輸速率和更低的設計成本, 已成為業界首選, 被廣泛應用于高速通信領域。提出了一種新的高速串行傳輸接口的設計方案, 改進了Aurora 協議數據幀

2010-09-22 08:42:29 31

31 采用Xilinx 公司Virtex- II Pro 系列FPGA 內嵌得SERDES 模塊———RocketIO 作為高速串行協議的物理層, 利用其8B/10B的編解碼和串化、解串功能, 實現了兩板間基于數據幀的簡單高速串行傳輸

2010-09-22 08:44:28 28

28 FPGA高速收發器設計原則

高速收發器(SERDES)的運用范圍十分廣泛, 包括通訊、計算機、工業和儲存,以及必須在芯片與

2009-04-07 22:26:14 986

986 收發器的傳輸速率

不同的收發器產品由于轉換接口的不同,傳輸速率也不同,典型接口傳輸速率如下:

2010-01-08 14:16:26 4038

4038 采用帶有收發器的全系列40-nm FPGA和ASIC實現創新設計

人們對寬帶服務的帶寬要求越來越高,促使芯片供應商使用更多的高速串行收發器。因此,下一代應用采

2010-02-04 11:06:19 879

879

本文基于Virtex-5 FPGA的GTP單元給出了一種在高級電信計算架構(ATCA)機箱內實現單對差分線進行3.125Gbps串行傳輸的設計方案。

2011-09-16 09:52:19 1733

1733

GTP transceiver是FPGA里一種線速度達500Mb/sà6.6Gb/s的收發器,利用FPGA內部可編程資源可對其進行靈活地配置,使其適合不同的需要如以太網、SATA1.0接口

2018-07-14 06:45:00 17860

17860

了解如何在您的 ?UltraScale? FPGA? 設計中部署串行收發器。了解并利用串行收發器模塊的特性,如 ?8B/10B? 和 ?64B/66B? 編碼、通道綁定、時鐘校正和逗點檢測。其它專題

2017-02-09 08:04:41 327

327 賽靈思(Xilinx)公司FPGA器件的高速串行收發器類別如下

2017-02-11 11:11:30 5958

5958

線的過多會增加衛星重量,增加衛星發射成本。日前市面上的主流工業級FPGA芯片都集成各自開發的高速串行收發器,能達到很高的數據傳輸速率,但是衛星上使用的宇航級FPGA芯片中,卻少有集成高速串行收發器,在國防軍事衛星上使用國

2017-11-14 11:48:33 6

6 的數據傳輸,適用于多種高速數據傳輸協議。依據實際工程應用需求,提出了基于RocketIO的高速串行數據傳輸系統解決方案,實現了每通道2.5 Gb/s的傳輸速度。最后介紹了RocketIO在Aurora和PCI Express協議實現中的應用,并總結了高速通信系統的共性特征。

2017-11-24 20:37:49 1787

1787

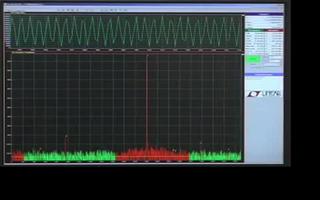

經理。我從事FPGA工作已經有12年了。他們中后5人的主要工作是高速串行收發器應用。

我們今天在這里演示新的Linear Technology LTC2274模數轉換器怎樣與具有嵌入式串行收發器

2018-06-20 05:28:00 4215

4215

展示7系列GTZ(高達28.05Gb / s)高速串行收發器的性能;

與Luxtera公司的不重定時光模塊進行四路26G對接,實現100G應用。

2018-11-23 06:20:00 3057

3057 通過Virtex-7 2000T FPGA中的GTX收發器實現高速串行性能。

2018-11-22 06:27:00 3461

3461 本文檔介紹如何在Spartan?6 FPGA中使用GTP收發器。?spartan-6 FPGA GTP收發器簡稱為GTP收發器。

?gtpa1_dual是實例化原語的名稱,它實例化一組

2019-02-15 14:42:47 27

27 7系列FPGA GTP收發器的可定制Logicore?IP Chipscope?Pro集成誤碼率測試(IBert)內核用于評估和監控GTP收發器。該核心包括在FPGA邏輯中實現的模式生成器和校驗

2019-02-20 14:30:00 25

25 UART(Universal Asynchronous Receiver Transmitter通用異步收發器)是一種應用廣泛的短距離串行傳輸接口。常常用于短距離、低速、低成本的通訊中。

2019-08-12 17:46:18 722

722

FPGA 針對需要超高速串行連接的應用進行了優化,Virtex?-6HXT FPGA通過結合6.6 Gbps GTX收發器和11.18 Gbps GTH收發器,提供了業界最高的串行帶寬,以實現下一代分組和傳輸,交換結構。 ,視頻切換和成像設備。Virtex-6 FPGA系列

2021-04-14 11:53:31 4122

4122

介紹了基于模塊化方法在FPGA上實現高速通信的設計方案。系統在Aurora協議下采用高速串行收發器Rocket I/O,解決了不同

2021-05-05 14:35:00 8915

8915

Virtex-5 RocketIOTM GTP收發器的串行高速系統接口開發過程中位寬轉換的幾個技術問題提出了解決方案,并以SATA2.0開發為例,通過Xilinx Virtex-5 XC5VLX50T FPGA驗證方案進行了可行性驗證。

2021-06-24 16:10:42 2510

2510

xilinx的7系列FPGA根據不同的器件類型,集成了GTP、GTX、GTH、GTZ四種串行高速收發器,可以支持多種協議如PCI Express,SATA,JESD204B等。

2022-03-01 17:17:20 3769

3769

此篇文章深入淺出介紹了關于高速串行收發器的幾個重要概念和注意事項,為方便知識點復習總結和后續查閱特此轉載。

2022-03-14 17:19:38 2541

2541 電子發燒友網站提供《Logos系列FPGA高速串行收發器(HSST)用戶指南.pdf》資料免費下載

2022-09-26 10:25:17 22

22

電子發燒友App

電子發燒友App

評論