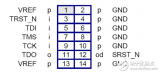

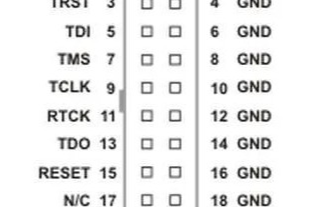

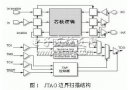

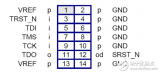

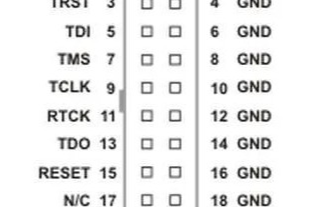

JTAG接口主要包括以下四個引腳:TMS TCK TDI和TCO及一個可選配的引腳TRST,用于驅動電路模塊和控制執行規定的操作。

2014-09-15 12:44:31 22903

22903

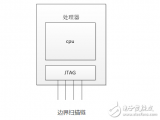

ARM系列處理器正是通過JTAG 接口使用內部集成的ICE 功能, 并采用這種方式實現在線調試。此外CPLD、FPGA 等器件大多都可以使用JTAG 接口實現在線編程或下載。因此,JTAG 接口已經成為復雜芯片系統的必備接口, 在芯片測試、調試及實現其他特殊功能方面發揮著重要作用。

2018-10-16 08:11:00 5801

5801

??AXI接口雖然經常使用,很多同學可能并不清楚Vivado里面也集成了AXI的Verification IP,可以當做AXI的master、pass through和slave,本次內容我們看下

2023-07-27 09:19:33 633

633

的輸出信號都在上升沿時變化。 2.ARESETn 全局復位信號,低電平有效。在復位期間,所有的xxVALID信號必須復位為低電平。其他的信號可以是任意值。 主機(master)控制的信號

2021-01-08 16:52:32

的axi quad spi ip core。 線連接如下所示:slave_io0_i - master_io0_o slave_io1_o - master_io1_i slave_clk_i

2020-04-17 10:13:04

Axi4ReadOnlyDecoder對于Axi4讀操作而言,其指令的完成由ar、r兩個通道完成,相較于寫操作,其通道數雖然少了一個,但也是兩個方向的數據流:ar:master——>

2022-08-04 14:28:56

“hw_axi_1”作為上面的第二個參數?如果您知道只有一個JTAG到AXI IP連接到調試集線器,為什么還需要一個列表(這是一個列表?)。 UG825(v2016.2)的第250頁將此參數稱為“并將其描述為”關聯

2020-05-20 09:11:18

,如下截圖。有時候手動選擇JTAG 調試時 JTAG Device Chain下面沒有可以選擇的東西,只能選擇SW調試,選JTAG 有時報錯我沒截到圖。有沒有大蝦可以幫幫忙,求助?

2019-03-22 04:26:17

JTAG 作為一個通用的標準器件功能測試接口, 具有靈活高效、易于實現等優點, 是微控制器、微處理器、DSP、SoC 等器件的重要外部接口。它不但可以用來測試內部功能模塊狀態, 而且可以實現在線調試

2019-08-27 06:18:54

JTAG調試:協議轉換器解釋上位機傳送過來的命令,通過JTAG控制ARM執行z Angel調試:協議轉換器可以直接做為目標板的Firmware的一部分。直接執行從宿主機傳送過來的調試命令;并回送相應

2017-11-07 14:53:44

CPU核通信,實現了完全非插入式調試,不使用片上資源,不需要目標存儲器,不占用目標系統的任何端口。由于JTAG調試的目標程序是在目標板上執行,使得仿真更加接近于目標硬件[1]。目前針對嵌入式系統

2019-10-18 06:33:42

ARM-JTAG調試原理

2012-08-03 22:00:11

ARM.JTAG.調試原理

2018-02-05 09:43:30

[hide]ARM.JTAG.調試原理/[/hide]

2013-10-20 16:53:24

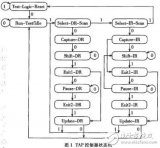

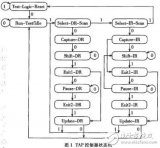

這篇文章主要介紹 ARM JTAG 調試的基本原理。 基本的內容包括了 TAP (TEST ACCESSPORT) 和 BOUNDARY-SCAN ARCHITECTURE 的介紹, 在此基礎上

2017-11-07 14:56:55

正確執行任何其他讀取操作。在PSoC創建者中顯示以下錯誤:dg.M033:選定的調試目標“CY8C5688 AXI-060未分配”與項目選定的設備“CY8C5688 AXI-060 ES1”不兼容

2019-04-02 14:17:24

API函數實現JTAG to AXI Master的讀寫通過調用SDK里的API函數,可以實現通過JTAG線與FPGA內部邏輯通信。即在FPGA內部例化SDK里的IP(JTAG轉localbus或者

2020-09-27 10:45:13

用中斷,波特率1000,片選、ENA管腳用作普通的IO口。程序工作過程:570主設備發送一個字符到從設備,從設備立即把這個字符返回發給主設備570。

??? 出現的問題:在使用JTAG單步調試的時候

2018-06-21 09:36:14

大部分器件的接口要求,提供互聯架構的靈活性與獨立性。

(1)AXI總線

總線是一組傳輸通道,是各種邏輯器件構成的傳輸數據的通道,一般由數據線、地址線、控制線等構成。在ZYNQ中支持三種AXI總線

2023-11-03 10:51:39

ARM JTAG調試時檢測不到目標系統 答:調試前,請把目標板連接好,然后用調試軟件檢測目標系統。如果檢測不到目標系統,請做以下的檢查。A - 有些芯片是可以加密的,加密后JTAG接口就自動被禁

2011-11-30 10:18:29

我根據以下快速拍攝視頻完成了我的設計:http://www.xilinx.com/video/hardware/using-jtag-to-axi-master-in-vivado.html在視頻

2020-08-12 09:16:08

user_clk從端點連接到AXI configuredILA的時鐘端口時,似乎永遠不會出現在硬件管理器中(在調試探針窗口中)。 a)這是否必須對自由運行時鐘要求做些什么? b)我使用了緩沖的系統時鐘(來自

2019-09-25 09:26:14

AXI總線在FPGA設計中使用越來越頻繁,但初學的同學經常會因為對協議的理解不夠深入,寫出來的代碼經常會出現死鎖等問題,對FPGA設計與調試帶來很多不必要的麻煩。為了解決這個問題,我們可以

2022-10-09 16:08:45

幸運的是,isee“Zynq-7000示例設計 - 使用Master AXI GP訪問AXI Slave的CPU吞吐量”。以下列表是結果。我能否得出結論,使用Master AXI GP訪問AXI

2019-11-01 09:31:44

調試ARM,要遵循arm的調試接口協議,JTAG就是其中的一種。當仿真時,IAR、KEIL、ADS等都有一個公共的調試接口,RDI就是其中的一種,那么我們如何完成RDI-->arm調試協議

2022-05-24 15:53:14

嵌入式系統交叉調試方法一般分為兩種,一種是基于JTAG的片上調試方法,一種是基于調試代理的遠程調試方法。JTAG是一種國際標準芯片測試協議,目前大多數CPU體系都支持JTAG。基于JTAG的片上調試

2017-12-18 10:55:39

我對AXI互連有疑問,1.我的AXI4 Masterwith數據寬度為32位。我有64位數據寬度的AXI3從器件。互連如何工作?2.如果我有64位的PL AXI3 Master,我想連接到PS

2019-04-01 10:10:35

求大佬分享uart2axi_master_intf程序源碼

2022-02-22 06:43:59

是通過配置ZYNQ系統自動生成的;axi_gp_top.v模塊以及其下的兩個子模塊,是這個實例我們自己動手編寫的邏輯。axi_gp_ctrl.v模塊對AXI GP總線的控制、地址時序進行譯碼

2019-11-12 10:23:42

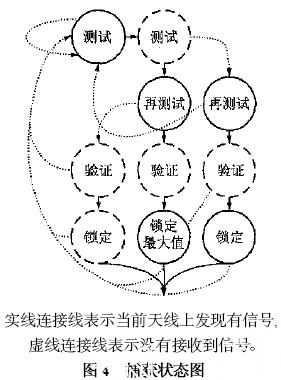

測試機。IBERT是針對高速串行接口的在線調試和驗證。通過IBERT的檢測,可以確認FPGA內部的高速串行口傳輸數據的可靠性和穩定性。JTAG-to-AXI Master,即JTAG-to-AXI主機

2019-05-24 15:16:32

我使用vivado 2014.4使用JTAG到AXI Master進行調試設計。當我運行實現時,系統有錯誤[Drc 23-20]規則違規(RPBF-2)IO端口驅動邏輯 - 設備端口clk驅動邏輯

2020-05-01 15:01:24

是:使用designware AHB2AXI IP,將AHB master轉換成AXI master,同時設置AXI總線上的pipeline options(當然相應的也要將原先的AHB slave改為AXI slave

2021-06-23 09:01:13

的Linux的xdevcfg設備來編程PL部件。有趣的解決方案是通過在同一芯片的PS部分運行的XVC遠程調試基于Zynq的設計。假設我將XAPP1251中描述的AXI-JTAG控制器添加到我的設計中,是否

2020-07-30 13:51:19

JTAG先進的功能和系統設計,JTAG Advanced Capabilities and System Design

The JTAG bus, originally intended

2009-05-16 09:57:30 32

32 JTAG調試原理(推薦):ARM JTAG 調試原理

2009-05-27 08:59:49 21

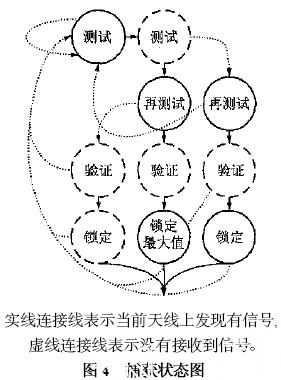

21 JTAG調試原理(推薦):溫度循環監測儀

2009-05-27 10:38:59 54

54 JTAG調試原理(推薦):這篇文章主要介紹ARM JTAG調試的基本原理。基本的內容包括了TAP (TEST ACCESS PORT) 和BOUNDARY-SCAN ARCHITECTURE的介紹,在此基礎上,結合ARM7TDMI詳細介紹了的JTAG調試原

2009-05-27 10:44:50 147

147 這篇文章主要介紹ARM JTAG調試的基本原理。基本的內容包括了TAP (TEST ACCESS PORT) 和BOUNDARY-SCAN ARCHITECTURE的介紹,在此基礎上,結合ARM7TDMI詳細介紹了的JTAG調試原理。這篇文章主要是

2009-07-14 23:19:49 82

82 嵌入式ARM 軟、硬件調試技術依賴于ARM 處理器調試硬件,本文在分析JTAG 邊界掃描結構的基礎上,介紹了EmbeddedICE、嵌入式跟蹤等實時調試技術,并給出了一個嵌入式調試開發系統

2009-08-14 15:55:42 5

5 ARM與JTAGJTAG(Joint Test Action Group ,聯合測試行動小組 ) 是一種國際標準測試協議,主要用于芯片內部測試及對系統進行仿真、調試, JTAG 技術是一種嵌入式調試技術,它在芯片內

2009-09-13 10:57:35 85

85 嵌入式JTAG調試方法步驟

嵌入式系統JTAG調試步驟1. 將PC與調試器Multi-ICE用并口連接;調試器與開發板用14或20針的JTAG線連接。2. 依次打開調試器

2010-03-01 16:24:20 34

34 什么是jtag接口

JTAG(Joint Test Action Group ,聯合測試行動小組 ) 是一種國際標準測試協議,主要用于芯片內部測試及對系統進行仿真、調試, J

2007-12-20 13:40:08 47060

47060

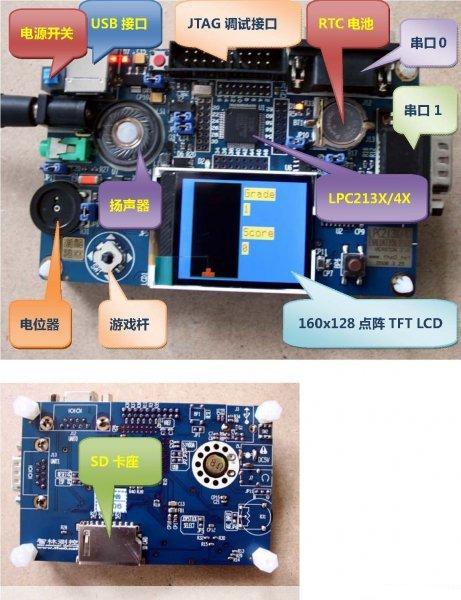

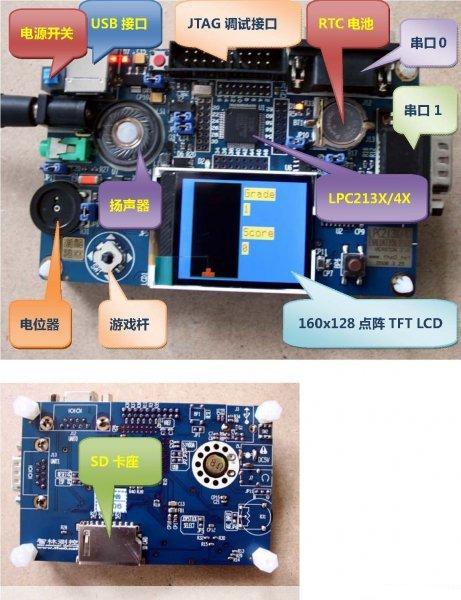

JTAG技術是一種嵌入式調試技術,芯片內部封裝了專門的測試電路TAP(測試訪問口),通過專用的JTAG測試工具對內部節點進行測試和控制,目前大多數ARM器件支持JTAG

2008-08-24 13:10:39 8144

8144

JTAG調試快速入門

提要:本文介紹 AVR Studio Debug:調試運行方式及QuickWatch實時查看變量的數值。

以下的degug方式,英文版來自 AVR St

2008-10-31 21:58:10 2055

2055 一種嵌入式系統實現的JTAG調試器

JTAG 作為一個通用的標準器件功能測試接口, 具有靈活高效、易于實現等優點, 是微控制器、微處理器、DSP、SoC 等器

2009-10-06 09:53:55 1106

1106

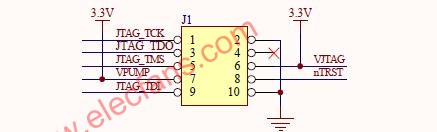

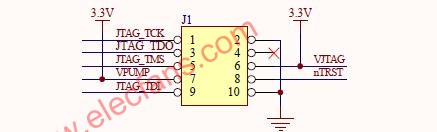

JTAG調試接口電路

注:VPUMP和VJTAG需要接3.

2010-03-17 09:25:56 2554

2554

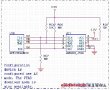

基于JTAG仿真器的調試是目前ARM開發中采用最多的一種方式。大多數ARM設計采用了片上JTAG接口,并將其作為測試、調試方法的重要組成。

JTAG仿真器通過ARM芯片的JTAG邊界掃描

2010-06-30 15:20:03 3001

3001

本內容向大家提供了JTAG功能及系統設計 JTAG也是一種國際標準測試協議(IEEE 1149.1兼容),主要用于芯片內部測試。現在多數的高級器件都支持JTAG協議,如DSP、FPGA器件等。標準的JTAG接口是

2011-03-30 10:04:32 0

0 本內容提供了ARM JTAG調試頭和Altera下載線合并電路 詳細列舉了電路原理圖

2011-03-31 17:19:22 209

209 ARM處理器采用一種基于JTAG的ARM的內核調試通道,它具有典型的ICE功能,基于ARM的包含有Embedded ICE(嵌入式在線仿真器)模塊的系統芯片通過JTAG端口與主計算機連接。

2011-08-16 09:51:08 2371

2371

這篇文章主要介紹ARM JTAG調試的基本原理。基本的內容包括了TAP (TEST ACCESS PORT) 和BOUNDARY-SCAN ARCHITECTURE的介紹,在此基礎上,結合ARM7TDMI詳細介紹了的JTAG調試原理。 這篇文章主要是總結了

2011-11-15 17:35:39 0

0 Altera JTAG下載和調試接口電路圖如下圖所示:

2012-08-15 14:25:22 13966

13966

電子發燒友網站提供《H-JTAG調試軟件下載.exe》資料免費下載

2012-12-18 13:15:34 57

57 STM32 調試器不能通過 JTAG 連接器件

2015-12-07 17:52:55 0

0 IAR+H_JTAG調試FLASH說明及例程。

2016-02-18 15:11:44 4

4 ARM JTAG 調試原理對于了解jtag結構由很好的幫助。

2016-03-10 14:08:48 10

10 H-JTAG 用戶使用手冊簡單介紹了 H-JTAG 和 H-FLASHER 的基本使用和配置,手冊同時也提供了一

些簡單的例子供用戶參考

2016-05-03 15:15:08 6

6 AXI總線的MicroBlaze雙核SoPC系統設計

2017-10-31 08:54:44 8

8 JTAG編程方式是在線編程,傳統生產流程中先對芯片進行預編程實現再裝到板上因此而改變,簡化的流程為先固定器件到電路板上,再用JTAG編程,從而大大加快工程進度。JTAG接口可對PSD芯片內部的所有部件進行編程

2017-12-10 10:20:22 9779

9779

調試ARM,要遵循ARM的調試接口協議,JTAG就是其中的一種。當仿真時,IAR、KEIL、ADS等都有一個公共的調試接口,RDI就是其中的一種,那么我們如何完成RDI--》ARM調試協議(JTAG)的轉換呢?

2017-12-10 10:40:02 10967

10967 JTAG(JointTestActionGroup,聯合測試行動小組)是一種國際標準測試協議,主要用于芯片內部測試及對系統進行仿真、調試,JTAG技術是一種嵌入式調試技術,它在芯片內部封裝了專門

2018-01-11 09:45:50 28818

28818

本文從引腳、調試方式、仿真器的支持和硬件接口四個方面對jtag和swd進行了詳細的對比區別。

2018-01-11 10:06:23 133181

133181

者能夠通過JTAG接口,用開放的硬件和軟件系統進行燒寫、校驗和調試。他們都基于JTAG調試接口協議。

2018-01-30 09:29:10 17445

17445

IARMSP430項目編譯與JTAG仿真調試步驟。

2018-04-19 08:29:09 5

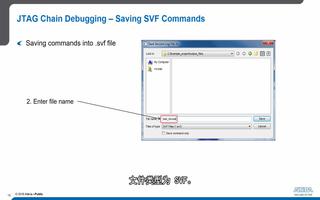

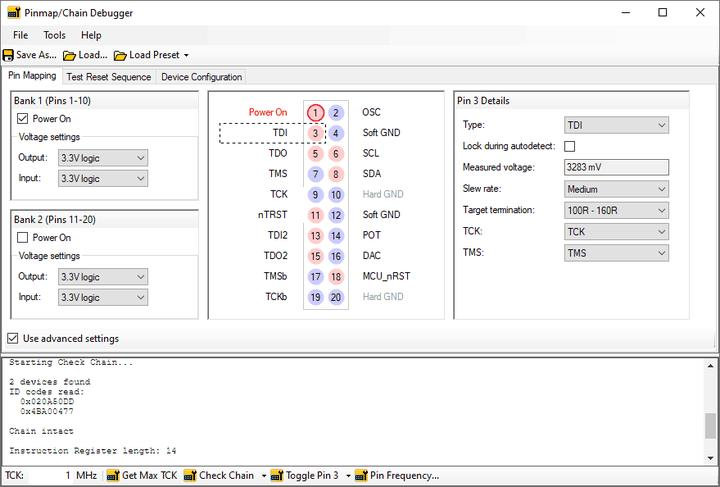

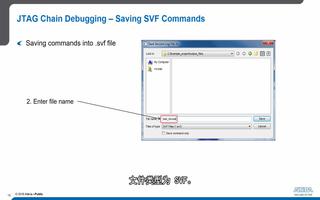

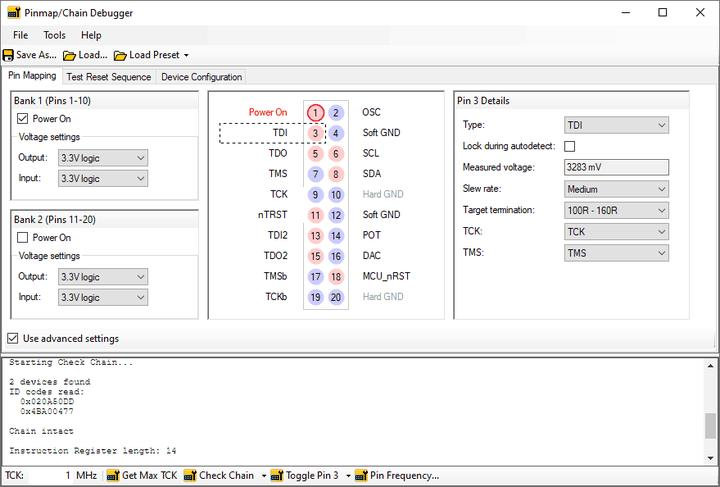

5 JTAG 鏈調試程序工具

2018-06-20 01:00:00 3687

3687

了解如何使用Xilinx AXI驗證IP有效驗證和調試AXI接口。

該視頻回顧了使用的好處,以及如何使用示例設計進行模擬。

2018-11-20 06:38:00 3561

3561 了解如何使用Vivado Design Suite IP Integrator有效地調試AXI接口。

本視頻介紹了如何使用該工具的好處,所需的調試步驟和演示。

2018-11-29 06:00:00 3680

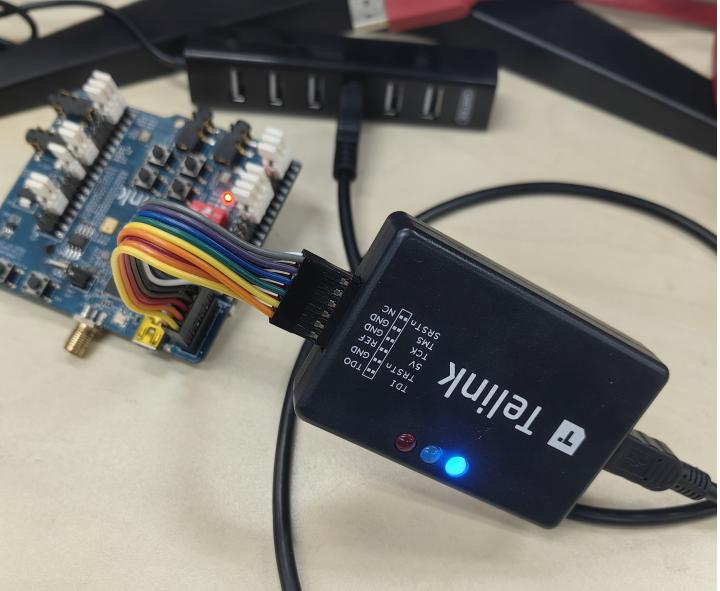

3680 產品名稱:Jtag調試小板

2019-11-13 09:53:10 2071

2071

RK3399系統調試架構,支持 JTAG/SW 和 TRACE_DATA 兩種輸出接口。這里主要介紹JTAG/SW 。

2019-12-17 16:40:39 19

19 bug 最有效直接的方式,今天我們要聊的是調試里最基礎的東西,即接口標準。ARM 內核原生支持 2 種業界通用的接口標準,分別是 JTAG 和 SWD。本節課痞子衡先給大家詳細講講 JTAG 接口。

2020-02-12 16:03:37 6072

6072

JTAG是Joint Test Action Group的縮寫,是IEEE 1149.1標準。使用JTAG的優點:JTAG的建立使得集成電路固定在PCB上,只通過邊界掃描便可以被測試。在ARM7TDMI處理器中,可以通過JTAG直接控制ARM的內部總線、I/O口等信息,從而達到調試的目的。

2020-08-10 16:42:33 2022

2022 JTAG是Joint Test Action Group的縮寫,是IEEE 1149.1標準。使用JTAG的優點:JTAG的建立使得集成電路固定在PCB上,只通過邊界掃描便可以被測試。

2020-08-27 14:18:48 2860

2860 在FPGA程序設計的很多情形都會使用到AXI接口總線,以PCIe的XDMA應用為例,XDMA有兩個AXI接口,分別是AXI4 Master類型接口和AXI-Lite Master類型接口,可通過

2020-10-30 12:32:37 3953

3953

新的賽靈思器件設計中不可或缺的一部分。充分了解其基礎知識對于賽靈思器件的設計和調試都很有幫助。 本篇博文將介紹賽靈思器件上的 AXI3/AXI4 的相關基礎知識。首先,我們將從一些通俗易懂的知識、理論

2020-09-27 11:06:45 5857

5857

器 簡單來說,下載調試器是將PC(例如通過USB協議)發送的命令轉換為MCU(負責MCU內部外圍設備)理解的語言(例如SWD或JTAG協議)的設備,加載代碼并精確控制執行。 2 調試器協議標準 1.什么是標準? 簡單來說,標準是一組規則和協議,特定行業中的每個參與者都同意遵循并執行。 2.調試器協議混亂現

2020-10-27 09:29:17 16100

16100

為 MCU(負責 MCU 內部外圍設備)理解的語言(例如 SWD 或 JTAG 協議)的設備,加載代碼并精確控制執行。 ? 2、調試器協議標準 1. 什么是標準? 簡單來說,標準是一組規則和協議,特定行業中的每個參與者都同意遵循并執行。 2. 調試器協議混亂現象 在 SWD 和 JTAG 之類的協

2022-11-28 11:44:06 3840

3840 在 AMBA 系列之 AXI 總線協議初探 中,了解到 AXI 總線交互分為 Master / Slave 兩端,而且標準的 AXI 總線支持不同的位寬,既然是總線,那么必須要支持總線互聯,多 Master,多 Slave的場景

2022-02-08 11:44:02 12802

12802 在 AMBA 系列之 AXI 總線協議初探 中,了解到 AXI 總線交互分為 Master / Slave 兩端,而且標準的 AXI 總線支持不同的位寬,既然是總線,那么必須要支持總線互聯,多 Master,多 Slave的場景

2021-02-23 06:57:00 45

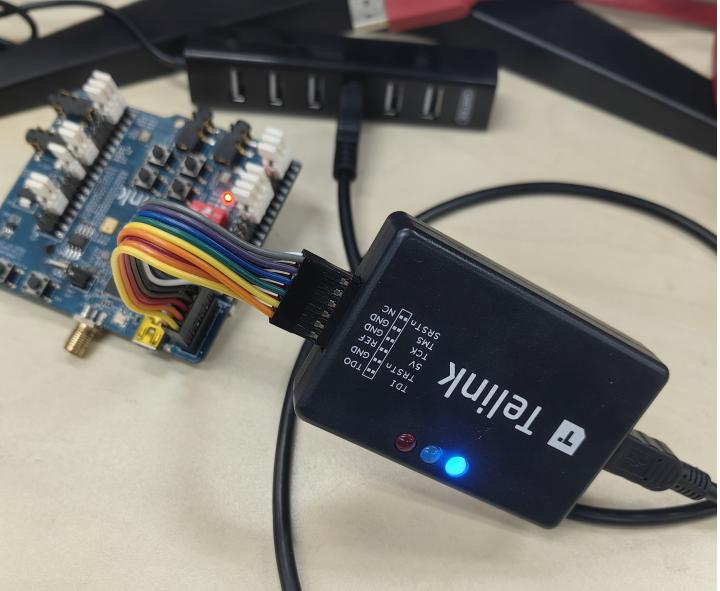

45 開發板(在本文中將其簡稱為“FPGA開發板”)和專用 JTAG 調試器(在本文中將其簡稱為“JTAG 調試器”)。

2021-03-23 10:00:28 41

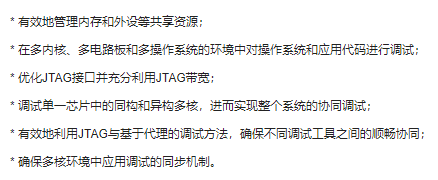

41 在傳統上,JTAG調試技術主要是用于硬件Bring-Up,如今也常常被用于配合基于代理的調試(agent-based debugging)。然而,在多核和多處理的環境中,片上調試(on-chip

2021-04-05 10:19:00 2988

2988

在一個項目中,當你使用microblaze作為控制器來進行系統調度的時候,一般是建議將所有模塊封裝成AXI形式的IP核,這樣好管理,也容易調試。

2021-04-27 11:17:36 5652

5652

STM32F103C8T6 核心板最小系統 Jtag調試下載接線圖如圖jtag模式1 VDD 棕3 TRST----PB4 紅5 TDI----PA15 橙7 TMS/SWDIO----PA13

2021-11-18 10:21:06 59

59 JTAG與SWD的含義與引腳前言一、JTAG二、SWD總結前言最近使用M0搭建了一個最基礎的SoC但是在使用keil進行軟件調試的過程中遇到了不小的問題,這里對常見的兩種調試方式做一個總結

2021-12-22 19:05:58 17

17 uart2axi_master_intf程序源碼:/**************************************************** Module Name

2021-12-28 20:04:42 14

14 對FPGA進行上板調試時,使用最多的是SignalTap,但SignalTap主要用來抓取信號時序,當需要發送信號到FPGA時,Jtag Master可以發揮很好的作用,可以通過Jtag Master對FPGA進行讀寫測試

2022-02-16 16:21:36 1900

1900

本文給大家提供利用axi_master接口指令端的幾個靜態參數的優化技巧,從擴展總線接口數量,擴展總線位寬,循環展開等角度入手。最核心的優化思想就是以資源面積換取高帶寬的以便并行計算。

2022-07-01 09:39:14 1015

1015 對 AXI master的全面討論變得困難。我還沒有(還)想出如何簡化材料來寫一篇關于如何構建通用 AXI master器的帖子,這已經夠難了——通常來說,尋址就是那么難。

2022-07-29 11:27:17 991

991 AXI IIC 和 PS IIC 控制器都符合 NXP IIC 總線規范。用戶必須確保其選擇使用的從設備的時序參數與UM10204 的第 48 頁上的“表 10”中的參數相同。

2022-08-25 10:29:08 1169

1169 AXI總線在FPGA設計中使用越來越頻繁,但初學的同學經常會因為對協議的理解不夠深入,寫出來的代碼經常會出現死鎖等問題,對FPGA設計與調試帶來很多不必要的麻煩。為了解決這個問題,我們可以

2022-10-08 16:07:11 3846

3846 JTAG鏈調試器(JTAG Chain Debugger),隨XJTAG的安裝包一起安裝,是一個功能強大的工具,旨在幫助您解決JTAG鏈的問題。

2023-07-19 14:41:07 319

319

?AXI接口雖然經常使用,很多同學可能并不清楚Vivado里面也集成了AXI的Verification IP,可以當做AXI的master、pass through和slave,本次內容我們看下AXI VIP當作master時如何使用。

2023-07-27 09:16:13 792

792

LogiCORE JTAG至AXI Master IP核是一個可定制的核,可生成AXIAXI總線可用于處理和驅動系統中FPGA內部的AXI信號。AXI總線接口協議可通過IP定制Vivado

2023-10-16 10:12:42 410

410

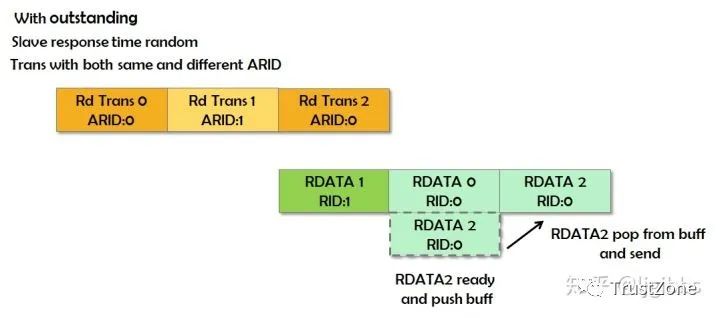

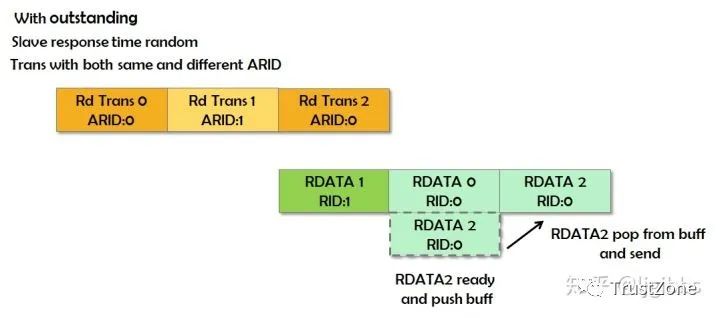

AXI的控制和數據通道分離,可以帶來很多好處。地址和控制信息相對數據的相位獨立,可以先發地址,然后再是數據,這樣自然而然的支持顯著操作,也就是outstanding 操作。 Master訪問

2023-10-31 16:53:09 432

432

Group”的縮寫,是一種硬件調試和測試技術,常被用于在集成電路中診斷和調試問題。JTAG的正式名稱為IEEE 1149.1標準,是一種通過掃描鏈(scan chain)實現的測試方法,該方法可以在不破壞芯片的情況下,對集成電路進行測試和調試。JTAG技術廣泛應用于數字集成電路、嵌入式系統和電路板等硬件開

2023-12-20 10:00:03 490

490

因為目前軟件的限制,RISCV的邏輯不能同時共用JTAG,所以如果想要同時去調試邏輯和RISCV的話,可以通過RISCV的soft Jtag來實現。soft Jtag就是通過GPIO來實現的軟件

2024-02-23 16:16:12 110

110

電子發燒友App

電子發燒友App

評論