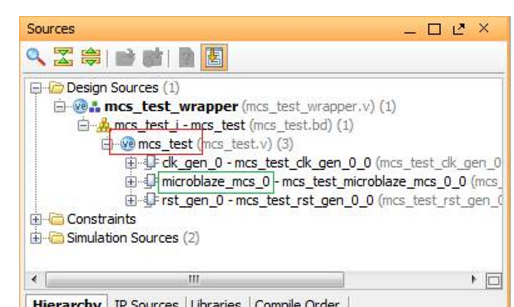

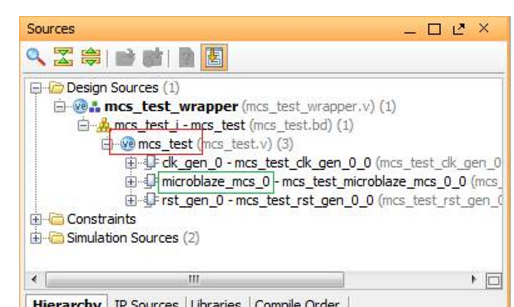

在我的 Vivado IP Integrator BD 設(shè)計(jì)中,有一個(gè) MicroBlaze MCS。

但當(dāng)我嘗試仿真時(shí),出現(xiàn)了類(lèi)似于以下情況的錯(cuò)誤:

2017-09-24 06:48:00 7937

7937

MicroBlaze是AMD-Xilinx提供的一個(gè)可以在FPGA中運(yùn)行的嵌入式軟核IP,其本質(zhì)是一個(gè)32位RISC處理器軟核。

2022-08-26 10:21:11 1234

1234 是否需要在512Mb之后開(kāi)始,因?yàn)楸忍亓魈岬降淖钚〕叽缡?12Mb2.如果我們選擇使用不同的microlaze圖像閃存(不是存儲(chǔ)比特流的圖像),我們可以使用FPGA和Vivado工具對(duì)此閃存進(jìn)行系統(tǒng)內(nèi)編程,還是需要預(yù)先編程的Flash?謝謝Sujith

2020-05-15 07:07:22

核,而如何針對(duì)特定的微處理器選擇合適的嵌入式操作系統(tǒng)是SOPC開(kāi)發(fā)的難點(diǎn)之一。本文針對(duì)Xilinx公司的MicroBlaze軟核,介紹了PetaLinux嵌入式操作系統(tǒng)及其移植方法,研究了PetaLinux的相關(guān)配置和啟動(dòng)方案。

2020-03-16 06:37:20

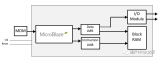

今天給大俠帶來(lái) MicroBlaze 串口設(shè)計(jì),開(kāi)發(fā)板實(shí)現(xiàn)使用的是Digilent basys 3,。話不多說(shuō),上貨。需要源工程可以在以下資料獲取里獲取。資料匯總|FPGA軟件安裝包、書(shū)籍、源碼

2023-08-24 20:13:39

普遍認(rèn)為開(kāi)發(fā)多處理器系統(tǒng)軟件的難度要大于單處理器系統(tǒng)。但實(shí)際情況并非總是如此。我們這個(gè)在 TRW 汽車(chē)公司下屬的咨詢(xún)部 TRW Conekt 工作的設(shè)計(jì)團(tuán)隊(duì)最近接管了一個(gè)項(xiàng)目,展示了如何根據(jù)手中的問(wèn)題發(fā)揮硬件的功能,并通過(guò)使用許多個(gè)處理器開(kāi)發(fā)出高效系統(tǒng)。

2019-10-23 08:00:03

64bit + Vivado2017.4版硬件平臺(tái):Xilinx-KC705本實(shí)例完整工程下載:請(qǐng)戳此處下面是兩個(gè)進(jìn)階工程,設(shè)計(jì)過(guò)程和本文要講的LED幾乎一樣,這里不在贅述。MicroBlaze控制1602_LCD下載:請(qǐng)戳此處MicroBlaze控制1602_LCD+LED+UART

2022-02-09 06:24:51

在進(jìn)行7A50T的MicroBlaze開(kāi)發(fā)時(shí),在SDK中運(yùn)行一個(gè)外設(shè)測(cè)試程序(測(cè)試LED),結(jié)果在下載程序(run)的時(shí)候,報(bào)下面紅色字體的錯(cuò)誤,還彈出一個(gè)紅框。該問(wèn)題的解決思路在何處,是否

2016-12-06 21:28:16

創(chuàng)建我自己的外圍設(shè)備,如明智。你可以幫助更多地了解如何使用microblaze處理器創(chuàng)建簡(jiǎn)單的算法。還有什么簡(jiǎn)單的教程嗎?

2020-03-30 10:28:17

VIVADO 2016.4microblaze + MIG,在SDK中讀寫(xiě)DDR3看到例程和網(wǎng)上一些帖子都會(huì)在操作前執(zhí)行xil_icacheenable(), xil_dcacheenable

2018-02-27 21:11:36

和microblaze都可以單獨(dú)對(duì)DDR3進(jìn)行正常的讀寫(xiě)操作,但是外部邏輯寫(xiě)入到DDR3中的數(shù)據(jù)在microblaze卻讀出不正確,讀出的是ddr3中默認(rèn)數(shù)據(jù),microblaze寫(xiě)到DDR3中的數(shù)據(jù)在外部邏輯

2017-03-21 14:01:12

處理器是怎樣與外部設(shè)備進(jìn)行通信的?有哪幾種方式?串行通信的數(shù)據(jù)傳輸方向是怎樣的?

2021-12-10 07:17:55

ARM處理器模式和ARM處理器狀態(tài)有何區(qū)別?

2022-11-01 15:15:13

我正在使用SDK 16.2調(diào)試微問(wèn)題。最初,Vivado 16.2沒(méi)有推出SDK 16.2,但是當(dāng)我手動(dòng)啟動(dòng)它時(shí),它無(wú)法調(diào)試microblaze。我嘗試使用SDK 15.4& Vivado 15.4和一切都工作得很好。

2019-09-27 09:49:17

STM32處理器與外部通信的兩種方式分別是什么?STM32的處理器是怎樣與外部進(jìn)行通信的?

2021-11-23 08:06:38

同一封裝中添加一個(gè)或多個(gè)MicroBlaze?處理器,只要能讓?xiě)?yīng)用受益就好。為什么要給處理功能已經(jīng)很強(qiáng)大的解決方案添加MicroBlaze呢?首先就是可靠性的問(wèn)題。單線程會(huì)大幅提高可靠性。您可以針對(duì)計(jì)算

2017-10-29 17:00:32

處理器IP核,將會(huì)大大減少開(kāi)發(fā)人員的工作量,從而對(duì)于提升工作效率,節(jié)約項(xiàng)目成本具有重大意義。采用FPGA和MicroBlaze進(jìn)行嵌入式系統(tǒng)設(shè)計(jì),可實(shí)現(xiàn)多片專(zhuān)用芯片的功能,有利于系統(tǒng)實(shí)現(xiàn)小型化、集成化

2020-10-16 16:28:50

ARM 處理器是一種低功耗高性能的 32 位 RISC(精簡(jiǎn)指令系統(tǒng))處理器。從結(jié)構(gòu) 入手對(duì)其進(jìn)行分析,并針對(duì)目前流行的 ARM920T 核詳細(xì)描述其硬件結(jié)構(gòu)和編程。ARM 處理器共有 31 個(gè)

2019-09-24 17:47:38

問(wèn)題一:在vivado中編寫(xiě)約束文件時(shí),由于nice接口的指令是由CPU、協(xié)處理器和內(nèi)存互相發(fā)送的,因此是否只需要約束clk和復(fù)位信號(hào)即可?

問(wèn)題二:從軟件示例程序中可知,數(shù)據(jù)是由軟件輸入的,那

2023-08-16 07:24:08

“Neitherthe MicroBlaze和PowerPC處理器在硬件中提供高速緩存一致性。當(dāng)兩個(gè)處理器訪問(wèn)相同的物理內(nèi)存時(shí),通過(guò)一個(gè)處理器更新內(nèi)存是另一方的緩存子系統(tǒng)沒(méi)有直接看到。如果需要,軟件就可以確保一致性

2019-03-04 13:41:13

嗨,我正在使用Kintex KC705評(píng)估板和Vivado 2016.3我有一個(gè)設(shè)計(jì)(DUT)需要針對(duì)所有各種輸入組合進(jìn)行廣泛測(cè)試,因?yàn)樗壳坝写蠹s150個(gè)輸入和大約80個(gè)輸出。我計(jì)劃將設(shè)計(jì)打包為

2018-11-05 11:32:16

在vivado中對(duì)示例代碼進(jìn)行仿真,可是協(xié)處理器的nice_req_valid等信號(hào)一直是0,請(qǐng)問(wèn)是什么原因?

2023-08-11 06:37:44

、SW撥碼開(kāi)關(guān)以下是官網(wǎng)提供的資料鏈接:arty a7開(kāi)發(fā)板資料Pmod DA4資料vivado安裝說(shuō)明board files添加基于microblaze的vivado開(kāi)發(fā)流程以下是在vivado2017.4_MicroBlaze_ArtyA735t上的開(kāi)發(fā)流程新建工程注:路徑不要有中文名,電

2022-01-18 08:09:43

多內(nèi)核是指在一枚處理器中集成兩個(gè)或多個(gè)完整的計(jì)算引擎(內(nèi)核),多核處理器是單枚芯片(也稱(chēng)為“硅核”),能夠直接插入單一的處理器插槽中,但操作系統(tǒng)會(huì)利用所有相關(guān)的資源,將它的每個(gè)執(zhí)行內(nèi)核作為分立的邏輯

2019-06-20 06:47:01

如何利用ARM9處理器如何設(shè)計(jì)一種SD卡電路呢?

2022-07-19 14:24:57

傅里葉變換、脈沖壓縮、線性預(yù)測(cè)編碼語(yǔ)音處理、高速定點(diǎn)矩陣乘法等,有較好的應(yīng)用前景和發(fā)展空間。那有誰(shuí)知道該如何利用FPGA實(shí)現(xiàn)級(jí)聯(lián)信號(hào)處理器嗎?

2019-07-30 07:22:48

SOPC技術(shù)是什么?多媒體廣告系統(tǒng)是由哪些構(gòu)成的?如何利用Nios II處理器去設(shè)計(jì)多媒體廣告系統(tǒng)?

2021-04-08 06:23:49

USART串口輸出該怎樣去使用呢?如何利用USART串口輸出實(shí)現(xiàn)外部設(shè)備與處理器的通信?

2022-02-18 06:29:10

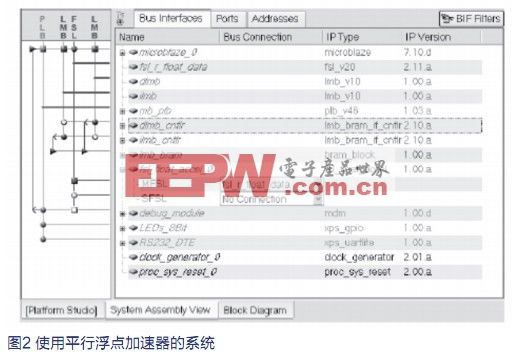

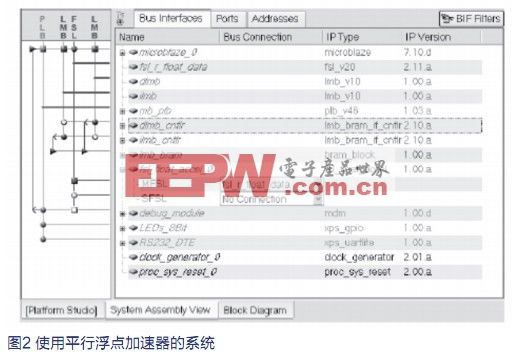

目前,越來(lái)越多的FPGA設(shè)計(jì)開(kāi)始采用嵌入式處理器,如PowerPC和賽靈思(Xilinx)的MicroBlaze處理器來(lái)完成控制任務(wù),采用C語(yǔ)言等軟件語(yǔ)言描述這些控制任務(wù),要比使用VHDL或

2019-09-17 07:42:45

我正在使用Atlys spartan 6 xc6slx45。我正在使用雙處理器系統(tǒng)。我創(chuàng)建了2個(gè)項(xiàng)目,其中一個(gè)包含microblaze0的代碼,其他包含microblaze1的代碼。當(dāng)我運(yùn)行代碼

2019-07-30 07:13:34

我喜歡使用verilog,vivado2017.1設(shè)計(jì)處理器(MIPS32),設(shè)備是Virtex7 vc707。我已經(jīng)使用BRAM作為主存儲(chǔ)器(.coe文件的init指令)在FPGA(Virtex7

2020-08-25 13:19:36

Vivado設(shè)計(jì)套件用戶(hù)指南:嵌入式處理器硬件設(shè)計(jì) 討論使用Vivado?IP集成器和Xilinx軟件開(kāi)發(fā)套件(SDK),使用Zynq?-7000 All Programmable(AP)SoC

2017-11-15 10:34:10

MicroBlaze是一款基于構(gòu)造的的嵌入式微處理器,它的顯著優(yōu)勢(shì)在于能滿(mǎn)足復(fù)雜應(yīng)用的需求,在除了運(yùn)行簡(jiǎn)單的通用應(yīng)用以外,還能運(yùn)行操作系統(tǒng)。

2019-10-11 07:08:34

怎么利用FPGA和嵌入式處理器實(shí)現(xiàn)低成本智能顯示模塊?

2021-04-28 07:10:33

介紹國(guó)家半導(dǎo)體公司(NS)的Geode TMGX1處理器及協(xié)同芯片,說(shuō)明如何利用該芯片組進(jìn)行嵌入式系統(tǒng)設(shè)計(jì),并討論一些設(shè)計(jì)難點(diǎn)的處理。

2019-09-05 07:30:36

如何利用LPC2292嵌入式微處理器設(shè)計(jì)監(jiān)護(hù)系統(tǒng)?

2019-07-31 06:10:30

怎么使用ARM處理器上的GPU進(jìn)行編程工作呢?有哪位大神可以解釋一下

2022-08-04 14:17:35

嗨,大家好,我正在使用Vivado 2014.4有沒(méi)有辦法使用Vivado本身為Microblaze創(chuàng)建FSL接口?如果是,我可以使用此FSL將FIFO連接到MB嗎?請(qǐng)建議。謝謝你們,提前。謝謝&問(wèn)候,專(zhuān)一

2020-04-06 17:25:00

嗨,我在一個(gè)TOP VHDL模塊下有一個(gè)Microblaze處理器和其他VHDL RTL。我在Microblaze處理器上寫(xiě)了一些固件C應(yīng)用程序。我正在編譯C代碼以獲得輸出精靈。整個(gè)系統(tǒng)按預(yù)期工作

2019-04-04 16:37:17

有沒(méi)有人推薦使用Vivado的好處理器?我目前有一個(gè)6核3.5GHz AMD設(shè)備,8GB內(nèi)存。我的設(shè)計(jì)不是很復(fù)雜(AXI總線,MIG,一些IP),但在Artix 100T上合成和實(shí)現(xiàn)大約需要25分鐘

2019-03-14 10:09:23

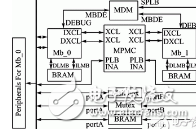

處理器間通信和中斷方面仍需進(jìn)一步的研究。本文在處理器間通信和中斷控制方面進(jìn)行了深入的研究。MicroBlaze是一個(gè)被優(yōu)化過(guò)的可以在Xilinx公司FPGA中運(yùn)行的軟核處理器,可以和其他外設(shè)IP核一起完成

2021-03-16 07:44:35

請(qǐng)問(wèn)一下怎么利用CPLD降低處理器功耗?

2021-05-06 07:50:46

嗨, 我使用帶有AXI BUS接口的Vivado 2016.1構(gòu)建了我的設(shè)計(jì)。我使用了2個(gè)BRAM控制器,1個(gè)Microblaze處理器。設(shè)計(jì)成功合成。但是Vivado工具并沒(méi)有走出ROUTING過(guò)程。任何人都可以幫助我們走出路由流程。下面我附上了警告信息截圖。

2020-05-13 08:49:52

嗨,大家好,我正在研究Vivado 2014.4,Xilinx KC705。我需要通過(guò)Microblaze讀取存儲(chǔ)在BRAM(coe文件)中的數(shù)據(jù)進(jìn)行計(jì)算。我是微博閱讀部分的新手。有人可以建議我

2020-05-20 08:38:21

怎樣設(shè)計(jì)FIR濾波器結(jié)構(gòu)?怎樣設(shè)計(jì)級(jí)聯(lián)型信號(hào)處理器?如何對(duì)級(jí)聯(lián)型信號(hào)處理器進(jìn)行仿真測(cè)試?

2021-04-28 07:04:01

請(qǐng)問(wèn)軟處理器屬不屬于IP core呀?比如MicroBlaze、Nios ii這些。

2014-11-08 18:47:00

的位置)進(jìn)行。而沒(méi)有必要計(jì)算出周期中點(diǎn)精確的位置。 圖1 - 并行的流水線,每個(gè)引擎由一個(gè)MicroBlaze處理器、專(zhuān)用存儲(chǔ)器和可選的減負(fù)器構(gòu)成

2008-09-25 17:17:55

嗨,大家好,我正在嘗試調(diào)試我的Microblaze應(yīng)用程序,但是當(dāng)我啟動(dòng)它并且讓時(shí)間過(guò)去時(shí)它會(huì)停止在XMD控制臺(tái)中顯示此消息:處理器無(wú)法停止錯(cuò)誤:MicroBlaze未被計(jì)時(shí)。檢查

2019-07-17 14:18:30

分析軟處理器MicroBlaze 的體系結(jié)構(gòu), 給出MicroBlaze 內(nèi)核在軟件無(wú)線電系統(tǒng)中的應(yīng)用, 實(shí)現(xiàn)SOPC(可編程系統(tǒng)芯片)。

2009-04-15 10:16:09 22

22 分析軟處理器MicroBlaze 的體系結(jié)構(gòu),給出MicroBlaze 內(nèi)核在軟件無(wú)線電系統(tǒng)中的應(yīng)用,實(shí)現(xiàn)SOPC

2009-11-30 15:02:14 31

31 摘要: 分析軟處理器MicroBlaze的體系結(jié)構(gòu),給出MicroBlaze內(nèi)核在軟件無(wú)線電系統(tǒng)中的應(yīng)用,實(shí)現(xiàn)SOPC(可編程系統(tǒng)芯片)。

關(guān)鍵詞: FPGA IP Core SOP

2009-06-20 10:47:52 3041

3041

采用硬件加速發(fā)揮MicroBlaze處理能力

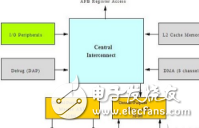

MicroBlaze處理器是賽靈思(Xilinx)在嵌入式開(kāi)發(fā)套件 (EDK) 中提供的兩款32位內(nèi)核之一,是實(shí)現(xiàn)硬件加速的靈活工具。圖1是MicroBlaze的

2010-03-10 10:24:16 1132

1132

MicroBlaze微控制器的理念簡(jiǎn)介

MicroBlaze是一款基于構(gòu)造的的嵌入式微處理器,它的顯著優(yōu)勢(shì)在于能滿(mǎn)足復(fù)雜應(yīng)用的需求,在除了運(yùn)行簡(jiǎn)單的通用應(yīng)用以

2010-05-04 10:29:07 1420

1420

本文介紹了一種可用于MicroBlaze處理器的嵌入式Linux操作系統(tǒng)——PetaLinux,并詳細(xì)討論了其內(nèi)核配置和啟動(dòng)方案。通過(guò)移植Peta-Linux,本文開(kāi)發(fā)的SOPC可以直接用于實(shí)際工程

2011-05-18 11:53:21 5149

5149

本設(shè)計(jì)已在Xilinx Spatan3 Starter Board 上進(jìn)行了驗(yàn)證,取得了良好的效果。通過(guò)本設(shè)計(jì)的實(shí)現(xiàn)可以看出, MicroBlaze 是一個(gè)功能強(qiáng)大、應(yīng)用靈活的嵌入式軟處理器,特別是其強(qiáng)大的用戶(hù)自定義

2011-06-07 17:03:40 51

51 MicroBlaze 核是嵌入在Xilinx FPGA之中的屬于32位RISC Harvard架構(gòu)軟處理器核。針對(duì)Xilinx MicroBlaze軟處理器的核間互連,實(shí)現(xiàn)多處理器核之間的快速通信的目的,采用了PLB和FSL總線混連的方法,

2011-07-20 17:22:21 68

68 MicroBlaze嵌入式處理器軟核是Xilinx公司推出的基于fpga的微處理器,它采用32位精簡(jiǎn)指令集(RISC)哈佛總線架構(gòu),具有運(yùn)行速度快、占用資源少、可配置性強(qiáng)等優(yōu)點(diǎn)。借助Xilinx EDK(嵌入式開(kāi)發(fā)

2011-11-16 11:54:22 66

66 大,我是否能夠利用Vivado HLS完成這項(xiàng)要求較高的運(yùn)算呢? 我開(kāi)始從軟件方面考慮這個(gè)轉(zhuǎn)換,我開(kāi)始關(guān)注軟件界面。畢竟,HLS創(chuàng)建專(zhuān)用于處理硬件接口的硬件。幸好Vivado HLS支持創(chuàng)建AXI slave的想法,同時(shí)工作量較少。 我發(fā)現(xiàn)Vivado HLS編碼限制相當(dāng)合理。它支持大多數(shù)C + +語(yǔ)言

2017-02-09 02:15:11 310

310 本文主要介紹MicroBlaze在 FPGA中的應(yīng)用,并結(jié)合實(shí)際工程介紹如何設(shè)計(jì)MicroBlaze微處理器與BPI Flash接口以及如何提高BPI Flash的燒寫(xiě)速度,同時(shí)也簡(jiǎn)單介紹利用

2017-11-17 09:41:05 3527

3527 在ISE下,對(duì)綜合后的網(wǎng)表進(jìn)行編輯幾乎是不可能的事情,但在Vivado下成為可能。Vivado對(duì)Tcl的支持,使得Tcl腳本在FPGA設(shè)計(jì)中有了用武之地。本文通過(guò)一個(gè)實(shí)例演示如何在Vivado下利用Tcl腳本對(duì)綜合后的網(wǎng)表進(jìn)行編輯。

2017-11-18 03:16:01 6899

6899

設(shè)計(jì)了一款基于雙MicroBlaze軟核處理器、面向嵌入式領(lǐng)域的SOPC系統(tǒng),在信息處理繁忙的情況下,實(shí)現(xiàn)兩軟核處理器之間的同步、通信和中斷功能,提高信息吞吐率和系統(tǒng)靈活性,降低設(shè)備尺寸。兩處理器

2017-11-18 03:50:27 3796

3796

封裝中添加一個(gè)或多個(gè)MicroBlaze處理器,只要能讓?xiě)?yīng)用受益就好。為什么要給處理功能已經(jīng)很強(qiáng)大的解決方案添加MicroBlaze呢?首先就是可靠性的問(wèn)題。單線程會(huì)大幅提高可靠性。

2017-11-18 10:19:30 5098

5098

通常基于傳統(tǒng)處理器的C是串行執(zhí)行,本文介紹Xilinx Vivado-HLS基于FPGA與傳統(tǒng)處理器對(duì)C編譯比較,差別。對(duì)傳統(tǒng)軟件工程師看來(lái)C是串行執(zhí)行,本文將有助于軟件工程師理解

2017-11-18 12:23:09 2377

2377

系統(tǒng)應(yīng)用,圍繞Xilinx 公司的MicroBlaze 微處理器,對(duì)其體系結(jié)構(gòu)、設(shè)計(jì)流程和相關(guān)開(kāi)發(fā)工具一一做出介紹,并且通過(guò)一個(gè)簡(jiǎn)單的實(shí)例來(lái)說(shuō)明以MicroBlaze 處理器為內(nèi)核的嵌入式系統(tǒng)的開(kāi)發(fā)過(guò)程。

2018-07-17 11:49:00 2242

2242

MicroBlaze是一款基于構(gòu)造的的嵌入式微處理器,它的顯著優(yōu)勢(shì)在于能滿(mǎn)足復(fù)雜應(yīng)用的需求,在除了運(yùn)行簡(jiǎn)單的通用應(yīng)用以外,還能運(yùn)行操作系統(tǒng)。 設(shè)計(jì)人員能夠在當(dāng)前所有的賽靈思架構(gòu)中實(shí)施

2017-11-24 19:09:01 975

975

MicroBlaze 是高度可配置的 IP 核,支持 70 多種配置選項(xiàng)。一些重要的配置選項(xiàng)為指令/數(shù)據(jù)高速緩存、浮點(diǎn)單元和存儲(chǔ)器管理單元等。用戶(hù)可使用高度靈活的可配置內(nèi)核,實(shí)現(xiàn)幾乎任何處理器使用案例

2018-03-16 16:10:26 10471

10471

MicroBlaze是一個(gè)被優(yōu)化過(guò)的可以在Xilinx公司FPGA中運(yùn)行的軟核處理器,可以和其他外設(shè)IP核一起完成可編程系統(tǒng)芯片的設(shè)計(jì)。它具有運(yùn)行速度快、占用資源少、可配置性強(qiáng)等優(yōu)點(diǎn),廣泛應(yīng)用于通信

2019-07-11 08:12:00 12686

12686

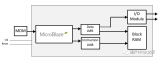

本文檔的主要內(nèi)容詳細(xì)介紹的是MicroBlaze(Vivado版)設(shè)置說(shuō)明詳細(xì)資料免費(fèi)下載開(kāi)始IP綜合設(shè)計(jì)(步驟)

1、在工作流導(dǎo)向面板中的IP Integrator中,點(diǎn)擊Create

2018-09-05 08:00:00 0

0 本文主要介紹Xilinx公司的MicroBlaze處理器的結(jié)構(gòu)及其原理。

該介紹MicroBlaze處理器時(shí),重點(diǎn)介紹了MicroBlaze處理器結(jié)構(gòu),MicroBlaze處理器信號(hào)接口,MicroBlaze處理器應(yīng)用二進(jìn)制接口和MicroBlaze指令集結(jié)構(gòu)。

2018-09-05 08:00:00 282

282 觀看此視頻,請(qǐng)參閱ARTY Board與Xilinx MicroBlaze軟核處理器的配合使用。

ARTY是一款基于Xilinx Artix-7 35T FPGA的99美元評(píng)估套件,它使用MicroBlaze作為其軟核處理器。

2018-11-27 06:26:00 2216

2216 了解如何從MicroBlaze處理器訪問(wèn)PS的內(nèi)部外設(shè)和DDR內(nèi)存控制器。

無(wú)需額外費(fèi)用即可討論硬件連接和軟件注意事項(xiàng)。

2018-11-27 06:21:00 3160

3160 了解如何使用Vivado中的Cadence IES Simulator在MicroBlaze IPI設(shè)計(jì)中運(yùn)行仿真。

我們將演示如何編譯仿真庫(kù),為IP或整個(gè)項(xiàng)目生成仿真腳本,然后運(yùn)行仿真。

2018-11-23 06:23:00 6174

6174 Xilinx公司的MicroBlaze 32位軟處理器核是支持CoreConnect總線的標(biāo)準(zhǔn)外設(shè)集合。MicroBlaze處理器運(yùn)行在150MHz時(shí)鐘下,可提供125 D-MIPS的性能,非常適合設(shè)計(jì)針對(duì)網(wǎng)絡(luò)、電信、數(shù)據(jù)通信和消費(fèi)市場(chǎng)的復(fù)雜嵌入式系統(tǒng)。

2018-12-05 17:18:05 13

13 在vivado中 ,如何查看各個(gè)模塊的資源占用情況呢?方法如下。以在xilinx官方評(píng)估板VC709的microblaze的軟核處理器例程為例。工程如下圖模塊組成。

2022-07-08 10:01:27 9568

9568 MicroBlaze CPU 是可修改的拖入式預(yù)設(shè) 32 位/64 位 RISC 微處理器配置系列。

2023-06-21 09:39:33 307

307

MicroBlaze? CPU 是可修改的拖入式預(yù)設(shè) 32 位/64 位 RISC 微處理器配置系列。

2023-06-26 09:14:29 553

553

Microblaze是32位/64位 RISC軟核處理器,可以用作微處理器、實(shí)時(shí)處理器和應(yīng)用處理器(Linux+MMU)。

2023-08-28 14:30:13 1220

1220

電子發(fā)燒友網(wǎng)站提供《MicroBlaze處理器參考指南.pdf》資料免費(fèi)下載

2023-09-14 15:02:40 1

1 電子發(fā)燒友網(wǎng)站提供《Vivado Design Suite教程:嵌入式處理器硬件設(shè)計(jì).pdf》資料免費(fèi)下載

2023-09-15 10:12:33 1

1

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論