摘 要:同步系統工作的好壞,在很大程度上決定了通信系統的質量。GPS接收機將天線接收到的衛星信號經射頻前端處理后變成了數字中頻信號,接收機對GPS衛星的信號處理過程,可依次分為捕獲、跟蹤、位同步和幀同步四個階段。針對GPS信號的BPSK調制和強度微弱等特點,模擬GPS 接收機基帶數字信號處理過程,首先介紹了科斯塔斯(Costas)接收機的工作原理,分析研究了基于FPGA的軟件無線電載波同步技術的實現方法,并采用Costas 環實現了載波同步,性能測試驗證了設計的正確性和可行性。

?

接收機對GPS衛星的信號處理過程,可以依次分為捕獲、跟蹤、位同步和幀同步四個階段。由于位同步、幀同步均需要以數據解調為前提條件,除了幅度調制及頻率調制可以采用非相干解調外,大部分調制方式都采用相干解調以獲取更好的性能,而進行相干解調,接收端就必須提取相干載波。載波同步的性能直接影響著通信系統的性能。針對GPS信號的BPSK 調制和強度微弱等特點,GPS 接收機鎖相環通常采用I/Q 解調法來幫助完成對輸入信號的下變頻、鑒相和數據解調等任務。自同步法是工程上廣泛應用的一種載波同步方式。自同步法主要有鎖相環、平方環、Costas環和判決反饋環等。目前工程上最常用的抑制載波跟蹤環是平方環和Costas環等。由于Costas 環不需要對接收信號進行平方變換,也不需要對鎖相環路中DDS 輸出的載波信號進行分頻處理,因此實現復雜度更小些,所耗費的硬件資源也更少。模擬GPS 接收機基帶數字信號處理過程,首先介紹了科斯塔斯(Costas)接收機的工作原理,分析研究了基于FPGA 的軟件無線電載波同步技術的實現方法,并采用Costas 環實現了載波同步,性能測試驗證了設計的正確性和可行性,對實際應用具有一定的指導價值。

1 Costas接收機的工作原理

目前的載波同步技術有多種電路,其中最常用的有平方環、Costas 環(同相―正交環)、判決反饋環等。J.P. Costas在1956 年首先提出采用同相―正交環來恢復載波信號,隨后Riter 證明跟蹤低信噪比的抑制載波信號的最佳裝置是Costas 環及平方環。傳統的模擬Costas 環因存在同相支路與正交支路的不平衡性從而使環路的性能受到一定影響,且模擬電路還存在直流零點漂移、難以調試等缺點,而采用全數字的實現方式,則可以有效避免這些問題。

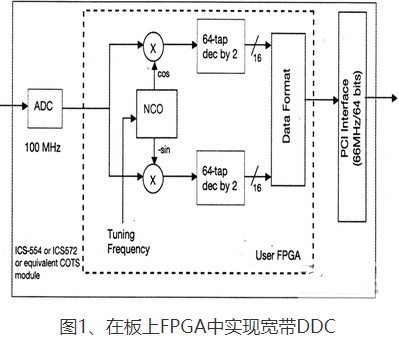

Costas環的工作原理如圖1 所示,主要由數字頻率合成器(DDS)、數字鑒相器(乘法器)、偽碼發生器(pn_gen)、低通濾波器(LPF 和環路濾波器(LF)組成。由于它是由輸入信號分別乘以同相和正交兩路載波信號,因此常稱這種環路為同相―正交環,亦稱科斯塔斯環(Costas)。輸入信號經上、下支路分別乘以同相和正交載波,然后再與偽碼進行相乘,并通過低通濾波器后再相乘,完成鑒相功能,最后經環路濾波器輸出控制本地振蕩器的誤差電壓。

2 系統設計與實現

2.1 參數選取

全數字載波環系統參數設計如下:

數據速率:4MHz;偽碼速率:10MHz;

載波頻率:70MHz;系統時鐘:100MHz;

中頻采樣后的載波頻率:6MHz;

信道帶寬:20MHz;調制方式:BPSK。

2.2 系統設計

1)直接數字頻率合成器的設計與實現直接數字頻率合成器的基本工作原理框圖如圖2 所示。

圖2 DDS 基本工作原理框圖

直接數字頻率合成器(direct digital frequency synthesizers,DDS,用于產生頻率及相位可控的正、余弦信號。DDS 的基本工作原理是在時鐘信號的驅動下讀取三角函數表。在FPGA實現中,通常采用ISE工具提供的DDS 核來實現。

DDS 的仿真波形如圖3 所示。系統仿真是由Modelsim10.1a 軟件實現的。

圖3 DDS 的仿真波形

2)偽碼發生器的設計與實現

GPS 從根本上講是一個基于碼分多址(CDMA)的擴頻(SS)通信系統。擴頻調制是通過偽隨機碼或偽隨機(PN)序列來實現的。GPS 采用的GOLD序列就是由m序列優選對產生的,其目的之一是用來實現碼分多址,目的之二是用來測距。

m 序列碼發生器是一種反饋移位型結構的電路,它由n 位移位寄存器加異或反饋網絡組成,其序列長度M =2n -1,只有一個冗余狀態即全0 狀態,所以稱為最大線性碼發生器。

由于其結構已定型,且反饋函數和連接形式都有一定規律,因此利用查表就可以設計出m 序列碼。表1 列出了部分m 序列碼的反饋函數和移位寄存器位數n 的對應關系。如果給定一個序列信號長度M,則根據M =2n-1 求出n,由n 查表便可得到相應的反饋函數。

考慮用長度m =5 的線性反饋移位寄存器產生一個m 序列。從表1 中選擇[3,5]作為反饋連接,編寫相應代碼進行仿真,結果如圖4 所示(初始狀態為00001)。系統仿真是由Modelsim10.1a 軟件實現的。通過仿真波形可以看出,偽碼發生器輸出的序列為1000010010110011111000110111010...,碼序列周期M=31。

圖4 偽碼發生器的仿真波形

3)低通濾波器的設計與實現

濾波器是數字信號處理中十分常用的模塊之一,一般來講,對于一些比較復雜的通用數字運算或處理需求,如果目標器件及開發工具提供相應的IP核,則一般選用IP核進行設計,這樣不僅可以提高設計效率,同時也可以保證系統的性能。

Xilinx 公司作為世界上最大的 FPGA/CPLD 生產商之一,多年來一直占據行業領先的地位。Xilinx 的FPGA/CPLD具有高性能、高集成度和高性價比的優點,而且它還提供了功能全面的開發工具和豐富的IP核、宏功能等。ISE(Intergrated synthesis Environment)是Xilinx FPGA/CPLD 的綜合性集成設計平臺,利用該平臺可完成從設計輸入、仿真、邏輯綜合、布局布線與實現、時序分析、程序下載與配置、功耗分析等整個FPGA/CPLD 的開發過程,其最新版本為ISE14.7 suit 系列。ISE13.1 提供了功能十分強大的FIR 核FIR Compiler v5.0。FIR 核進行配置后,即可以使用。

FIR Compiler v5.0核可根據用戶需要,選擇生成乘/ 加結構(Multiply Accumulate,MAC)或分布式結構(Distributed Arithmatic,,DA)的濾波器;最多可同時支持256個通道;抽頭系數從2~1024,輸入數據位寬及濾波器系數最多可支持49 比特,能夠自動發掘系數的對稱性來節省資源。

首先用 MATLAB 仿真低通濾波器系數,對濾波器系數進行n 位量化,并將濾波器系數存入FPGA所需的COE 文件。然后,用FIR 濾波器進行設計和實現。

低通濾波器(Lowpass filter,LPF)的仿真波形如圖5 所示。系統仿真由Modelsim10.1a 軟件實現。

圖5 低通濾波器的仿真波形

4)數字鑒相器的設計

數字鑒相器原理圖如圖6 所示。

圖6 數字鑒相器原理圖

根據圖1 Costas環的工作原理,鑒相器實際上是同相支路與正交支路的乘法運算。在FPGA 實現過程中,乘法運算不僅需要耗費較大的硬件資源,且運算速度也會受到一定限制。工程上通常取同相支路的符號位作為過零檢測脈沖,并與正交支路進行異或運算。

5)數字環路濾波器的設計

數字環路濾波器的結構如圖7 所示。

圖7 數字環路濾波器的結構圖

環路濾波器在Costas 接收機中起著非常重要的作用。它具有低通特性,一方面可以起低通濾波器的作用,更重要的是它對環路參數調整起著決定性的作用。在模擬電路中,常用的環路濾波器有RC積分濾波器、無源比例積分濾波器和有源比例積分濾波器。其中高增益的有源比例積分濾波器因其性能優良,是鎖相環中應用最為廣泛的濾波器(理想積分濾波器)。數字環路濾波器設計的關鍵問題在于獲取濾波器系數C1、C2。

對于理想積分濾波器來講,其數字化系統函數表示為

3 系統實現與仿真

圖8 為系統設計在Xilinx ISE開發平臺下實現后的仿真波形。系統仿真是由Modelsim10.1a軟件實現的。根據無線電技術的慣例,以二進制數“0”代表正電平(+1),以二進制數“1”代表負電平(-1)。從I、Q 支路輸出波形可以看出,BPSK調制后,在偽碼發生器輸出“0”時,載波相位狀態不變,在偽碼發生器輸出“1”時,載波相位會有180度 跳變。通過仿真波形還可以看出,對于不知道偽隨機碼(PN碼)的用戶而言,擴頻后的信號簡直就是噪聲。FPGA 實現后,可以在ISE 界面十分方便地查看到整個系統所占用的硬件資源及最高系統運算速度。其中, Slice Registers(寄存器資源)使用了759 個,占3%; Slice LUTs(查找表資源) 使用了631 個,占3%; Block RAM/FIFO使用了1 個,占3%;BUFG/BUFGCTRLs(全局時鐘資源) 使用了1 個,占3%;DSP48Es 使用了8個, 占25%。Minimum period:7.958ns{1} (Maximun frequency:125.660MHz) 最高系統時鐘頻率可達125.660MHz,顯然滿足設計要求的100 MHz。

圖8 系統仿真波形

4 結束語

GPS接收機對信號的跟蹤主要是借助載波環和碼環來完成的。載波環通過復制一個與接收載波信號的相位或頻率相一致的載波,然后讓接收信號與復制載波進行相乘混頻,以實現對輸入信號的下變頻,從中獲得對接收載波信號的相位或頻率的測量值,并且解調出接收信號上所調制的導航電文數據比特。載波同步的性能直接影響著通信系統的性能。全數字的載波同步環對GPS接收機來講就非常重要。

電子發燒友App

電子發燒友App

評論