一、前言 利用FPGA設(shè)計(jì)算法一直以來都是熱點(diǎn),同樣也是難點(diǎn)。將復(fù)雜的數(shù)學(xué)公式 模型通過硬件系統(tǒng)來搭建,在低延時(shí) 高并行性等優(yōu)勢(shì)背后極大提高了設(shè)計(jì)難度和開發(fā)周期。Xilinx公司的sysGen

2020-12-30 12:59:01 3171

3171

我是大數(shù)據(jù)方向的研究僧,導(dǎo)師讓加速一個(gè)基因組學(xué)的算法,需要用到FPGA,但因?yàn)閷?shí)驗(yàn)室并不是主攻這個(gè)方向的,所以不打算買開發(fā)板。請(qǐng)問各路大神,有沒有相關(guān)模擬器或仿真器可以讓我不買開發(fā)板就能跑程序的?

2018-05-29 15:31:04

ChipScope Pro組件應(yīng)用實(shí)例 685.7 FPGA設(shè)計(jì)的IP和算法應(yīng)用 745.7.1 IP核綜述 745.7.2 FFT IP核應(yīng)用示例 755.8 賽靈思 FPGA的專用HDL開發(fā)技巧 795.8.1

2009-04-09 18:28:46

電子工程師創(chuàng)新設(shè)計(jì)必備寶典系列之FPGA開發(fā)全攻略上,下兩冊(cè)

2016-04-24 21:11:22

ISE 是 Xilinx 公司提供的集成化 FPGA 開發(fā)軟件,它的主要功能包括設(shè)計(jì)輸入(DesignEntry)、綜合(Synthesis)、仿真(Simulation)、實(shí)現(xiàn)

2018-09-27 09:29:57

685.6.1 ChipScope Pro組件應(yīng)用實(shí)例685.7FPGA設(shè)計(jì)的IP和算法應(yīng)用745.7.1 IP核綜述745.7.2 FFT IP核應(yīng)用示例755.8 賽靈思 FPGA的專用HDL開發(fā)

2012-02-27 15:44:02

FPGA設(shè)計(jì)之浮點(diǎn)DSP算法實(shí)現(xiàn),DSP算法是很多工程師在設(shè)計(jì)過程中都會(huì)遇到的問題,本文將從FPGA設(shè)計(jì)的角度來講解浮點(diǎn)DSP算法的實(shí)現(xiàn)。FPGA設(shè)計(jì)之浮點(diǎn)DSP算法實(shí)現(xiàn)是賽靈思工程師最新力作,資料不可多得,大家珍惜啊1FPGA設(shè)計(jì)之浮點(diǎn)DSP算法實(shí)現(xiàn)[hide][/hide]

2012-03-01 15:23:56

你好: 我是一個(gè)購買的帳戶,所以我的許可證應(yīng)該允許訪問所有內(nèi)容。但是當(dāng)我使用System Generator for DSP時(shí),系統(tǒng)說我的SysGen簽出許可證失敗了。有人知道怎么解決嗎?謝謝

2019-01-28 07:16:36

錯(cuò)誤:System Generator for DSP(SysGen)的許可證簽出失敗。無法聯(lián)系Xilinx許可證管理器。請(qǐng)檢查以下內(nèi)容:(1)XILINX環(huán)境變量指向有效的ISE安裝(2

2018-12-29 10:35:12

FPGA中的數(shù)字控制器是什么?System Generator中的PID控制器是如何設(shè)計(jì)的?

2021-04-08 06:51:46

大家好,這是我第一次使用System Generator工具,如果有人能夠解決一個(gè)不讓我繼續(xù)參與我的硬件協(xié)同仿真項(xiàng)目的問題,我想。我正在使用Matlab R2013b,Xilinx ISE 14.7

2020-03-23 06:53:11

根據(jù)我的理解,System Generator是MatLab到RTL的轉(zhuǎn)換,因此不包括Vivado的優(yōu)化過程。問題1--是真的。確實(shí),Vivado中的優(yōu)化將大大改變系統(tǒng)描述,而系統(tǒng)描述不會(huì)向后兼容

2019-04-25 12:47:45

HI,我正在使用System Generator 2014.4 30天評(píng)估包,Matalb 2014B。簡單地說我想使用FIR編譯器,當(dāng)我嘗試編輯它的參數(shù)時(shí),我得到了兩個(gè)錯(cuò)誤: - 1.“來自MEX

2020-03-24 09:01:59

ATK-Mini Linux開發(fā)板-EMMC

2023-03-28 13:05:54

ATK-Mini Linux開發(fā)板-NAND

2023-03-28 13:05:54

ATK-MiniSTM32F103開發(fā)板 DEVB_80X100MM 5V

2023-03-28 13:05:53

TI CC2541開發(fā)套件

2023-03-25 01:27:25

/fpga-design/simulink-with-xilinx-system-generator-for-dsp.htmlhttp://www.mathworks.cn/searchresults/?c%5B%5D

2013-10-05 11:59:34

USE和System Generator何時(shí)才能勝任64位Windows 7?以上來自于谷歌翻譯以下為原文When will ISE and System Generator be qualified for 64 bit Windows 7?

2018-11-26 15:05:56

最近在搞system generator仿真,發(fā)現(xiàn)getway in這個(gè)模塊參數(shù)設(shè)置變化導(dǎo)致MATLAB閃退問題,貼圖如下其中g(shù)etway in 這個(gè)模塊數(shù)據(jù)類型換成定點(diǎn)有符號(hào)或者無符號(hào)數(shù)都不得行,換成布爾值又會(huì)出現(xiàn)錯(cuò)誤,不知為何啊!求教。

2018-01-05 21:43:53

N32G430C8L7_STB開發(fā)板用于32位MCU N32G430C8L7的開發(fā)

2023-03-31 12:05:12

高性能32位N32G4FRM系列芯片的樣片開發(fā),開發(fā)板主MCU芯片型號(hào)N32G4FRMEL7

2023-03-31 12:05:12

HiHope 滿天星智能家居開發(fā)套件

2023-03-28 13:07:10

潤和滿天星系列Pegasus智能小車開發(fā)套件,基于海思Hi3861V100芯片,支持OpenHarmony輕量系統(tǒng),實(shí)現(xiàn)巡線、避障功能通過尋跡模塊獲取路面軌道數(shù)據(jù),運(yùn)用尋跡算法使得智能小車可以按照固定軌道運(yùn)行

2023-03-28 13:07:10

STM32開發(fā)板 STM32F103RCT6最小系統(tǒng)板 ARM 一鍵串口下載 液晶屏

2023-04-04 11:05:04

STM32F401CCU6 411CEU6開發(fā)板 32F4核心小系統(tǒng)板 學(xué)習(xí)板

2023-04-04 11:05:04

STM32F407VET6開發(fā)板工控學(xué)習(xí)板帶485 雙CAN 以太網(wǎng) 物聯(lián)網(wǎng) STM32

2023-04-04 11:05:03

Verilog HDL數(shù)字系統(tǒng)設(shè)計(jì)篇教程預(yù)覽地址:鏈接:http://pan.baidu.com/s/1pK8TlcJ密碼:ojrjETree的開發(fā)板開發(fā)了下面17種verilog圖像算法下圖為ETree的FPGA視頻音頻開發(fā)板,在淘寶店:shop397545458.taobao.com

2017-11-28 22:20:11

翻譯成verilog,在FPGA里面實(shí)現(xiàn),即system generator。altera有沒有類似的接口,與matlab可以互連,直接在matlab里設(shè)計(jì)我所需要的算法,在翻譯成verilog?

2015-01-14 14:20:50

. But when it comes on selecting Matlab version for System generator 10.1 it displays both versions

2019-05-27 06:30:15

本帖最后由 xianer317 于 2014-6-21 19:30 編輯

《電子工程師創(chuàng)新設(shè)計(jì)必備寶典系列之FPGA開發(fā)全攻略》FPGA

2014-06-21 19:25:36

組的FPGA實(shí)現(xiàn)7.7 本章小結(jié)第8章基于System Generator的DSP系統(tǒng)開發(fā)技術(shù)8.1 System Generator的簡介與安裝8.1.1 System Generator簡介

2012-04-24 09:23:33

獵頭推薦職位:FPGA開發(fā)工程師工作職責(zé):1. 編寫設(shè)計(jì)方案,完成算法的封裝固化;2. 基于FPGA硬件開發(fā)平臺(tái),調(diào)試、驗(yàn)證負(fù)責(zé)視頻編碼算法和圖像處理算法;3. 利用***log/VHDL硬件描述

2017-07-04 15:27:02

獵頭職位:FPGA開發(fā)工程師工作職責(zé):1.基于FPGA硬件開發(fā)平臺(tái),調(diào)試、驗(yàn)證負(fù)責(zé)視頻編碼算法和圖像處理算法;2.編寫設(shè)計(jì)方案,完成算法的封裝固化;3.利用Verilo***L硬件描述語言實(shí)現(xiàn)相關(guān)

2017-07-17 15:15:12

獵頭職位:FPGA開發(fā)工程師工作職責(zé):1.基于FPGA硬件開發(fā)平臺(tái),調(diào)試、驗(yàn)證負(fù)責(zé)視頻編碼算法和圖像處理算法;2.編寫設(shè)計(jì)方案,完成算法的封裝固化;3.利用Verilo***L硬件描述語言實(shí)現(xiàn)相關(guān)

2017-09-11 15:59:18

,使用System Generator有三大優(yōu)勢(shì):第一,圖形化操作,簡單易用;第二,實(shí)現(xiàn)的算法能確保與仿真結(jié)果相符;第三,無需為仿真和實(shí)現(xiàn)建立不同的模型。因此,利用 System Generator可以大幅度減少用FPGA設(shè)計(jì)DSP的工作量,縮短開發(fā)周期。

2019-06-21 06:25:23

各位好,最近在使用system generator 搭建一個(gè)ifft設(shè)計(jì)模塊,使用ise調(diào)用,但是在下載到板子后,示波器輸出波形去在沒有輸入的情況下仍然有波形,確定不是噪聲,波形還是很規(guī)律,求解釋呀!

2016-07-13 13:21:30

使用system generator導(dǎo)入xilinx模塊時(shí),只要連線兩個(gè)模塊,matlab就崩潰,有知道原因的大佬嗎?

2018-01-19 17:54:57

`例說FPGA連載66:AV視頻采集之In-SystemSources and Probes概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2017-01-09 16:03:46

Suite下。在我的PC上,Xilinx System Generator嵌套在Vivado下。可以使用基于Vivado的System Generator來開發(fā)ISE系統(tǒng)嗎?或者是否有必須安裝

2018-12-27 10:55:34

大家好,我正在使用具有Virtex-4 FX100的定制板。在內(nèi)部,有一個(gè)基于VHDL的框架,它將定制板上的不同部分與“DSP內(nèi)核”連接,后者是在System Generator下開發(fā)的。在這

2019-01-15 10:39:11

在system generator中,我把(-128~127),變?yōu)椋?1~1),但是下載到硬件中,使用chipscope抓取到的數(shù)據(jù)確實(shí)(-128~127),請(qǐng)問是怎么回事

2016-08-10 15:32:38

有做System Generator處理圖像的嗎?遇到一些問題,一起商量下

2020-09-28 19:04:58

嗨,我正在嘗試學(xué)習(xí)如何使用System Generator來創(chuàng)建自己的IP核。首先,我在DocNav中找到了一個(gè)ug948-vivado-sysgen-tutorial文檔。我在哪里可以找到本文檔中描述的示例?我在安裝目錄中的“examples”文件夾中找不到完全相同的示例。提前致謝馬丁

2020-05-22 07:22:09

各位大佬,我在安裝System Generator時(shí),跟著教程走,發(fā)現(xiàn)在vivado中沒有出現(xiàn)System Generator for DSP這個(gè)選項(xiàng),請(qǐng)問是我哪里安裝得不對(duì)嗎?

2023-09-26 21:54:58

當(dāng)我完成SDx 2017.2的安裝時(shí),沒有安裝System Generator的選項(xiàng)。我正在運(yùn)行從Xilinx下載的安裝程序:https://www.xilinx.com/member/forms

2019-01-07 10:59:00

你好,我叫Joaquín。有人知道,我可以在Matlab / Simulink中使用System Generator創(chuàng)建一個(gè)雙向(inout)端口。我正在嘗試為Xilinx的外部存儲(chǔ)器創(chuàng)建一個(gè)接口

2019-05-09 14:36:24

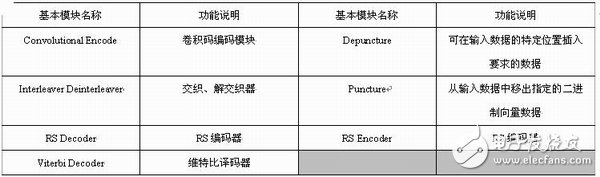

最近在使用system generator設(shè)計(jì)一個(gè)rs編碼譯碼的模型,總的思想是在rs編碼產(chǎn)生信號(hào)后,插入一個(gè)誤碼,然后作為信號(hào)源進(jìn)行解碼,看是否能夠正常的進(jìn)行解碼,求解是怎么才能把rs編碼后的信號(hào)存儲(chǔ)起來作為信號(hào)源

2016-07-20 20:13:59

有用Xilinx的system generator做圖像處理的嘛?求交流 。我正在用這個(gè)做圖像處理,已經(jīng)用了3個(gè)月了,在做一些算法,遇到一些困難,求一起交流學(xué)習(xí)。發(fā)現(xiàn)用這個(gè)開發(fā)的人真不多啊。

2014-05-09 14:57:21

`第一章、為什么工程師要掌握FPGA開發(fā)知識(shí)? 5第二章、FPGA基本知識(shí)與發(fā)展趨勢(shì) 72.1 FPGA結(jié)構(gòu)和工作原理 72.1.1 夢(mèng)想成就偉業(yè) 72.1.2 FPGA結(jié)構(gòu) 82.1.3 軟核

2014-11-21 15:08:56

以前,我們有Matlab 2006a和ISE 8.2i,并且正在使用System Generator。我們不得不重新安裝Matlab 2006a以啟用新的工具箱,但現(xiàn)在Simulink中沒有

2018-11-19 14:42:56

億海微6系 EQ6HL45型可編程邏輯芯片開發(fā)平臺(tái)采用核心板加擴(kuò)展板的模式,方便用戶對(duì)核心板的二次開發(fā)利用,為前期驗(yàn)證和后期應(yīng)用提供了可能。相信這樣的一款產(chǎn)品非常適合從事FPGA開發(fā)的工程師、科研人員等群體。

2022-02-16 17:06:51

System Generator for DSP 是一款具有高抽象層的設(shè)計(jì)工具,為算法開發(fā)人員和系統(tǒng)架構(gòu)師從 Simulink 算法參考模型過渡到FPGA 硬件實(shí)施技術(shù)提供了一種高效的途徑,且無需任何 HDL 編碼工作

2010-06-10 08:21:19 29

29

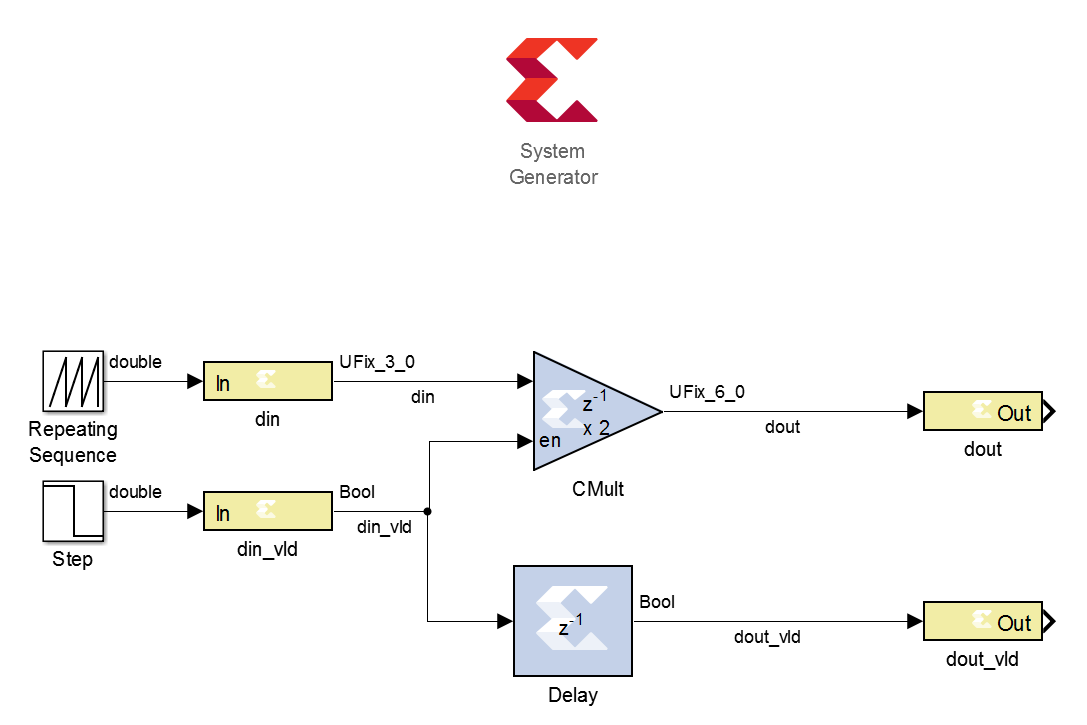

采用Gardner算法,對(duì)QPSK調(diào)制解調(diào)系統(tǒng)中的位同步系統(tǒng)進(jìn)行設(shè)計(jì)與實(shí)現(xiàn),大大提高了系統(tǒng)性能和資源利用率。重點(diǎn)闡述采用FPGA開發(fā)環(huán)境System Generator系統(tǒng)設(shè)計(jì)工具進(jìn)行位同

2010-07-21 16:12:40 26

26 Intel Agilex? F系列FPGA開發(fā)套件Intel Agilex? F系列FPGA開發(fā)套件設(shè)計(jì)用于使用兼容PCI-SIG的開發(fā)板開發(fā)和測試PCIe 4.0設(shè)計(jì)。該開發(fā)套件還可通過硬核處理器

2024-02-27 11:51:58

用matlab來實(shí)現(xiàn)fpga功能的設(shè)計(jì)

摘要:System Generator for DSP是Xilinx公司開發(fā)的基于Matlab的DSP開發(fā)工具?熗?時(shí)也是一個(gè)基于FPGA的信號(hào)處理建模和設(shè)計(jì)工具。

2008-01-16 18:10:54 11207

11207

深入了解賽靈思System Generator中的時(shí)間參數(shù)

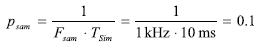

基于模型的設(shè)計(jì)(MBD)因其在縮小實(shí)時(shí)系統(tǒng)抽象的數(shù)學(xué)建模和物理實(shí)現(xiàn)之間差距方面的光明前景而備受關(guān)注。通過使用相同的

2009-12-29 11:40:30 1300

1300

HDL設(shè)計(jì)和驗(yàn)證與System Generator相結(jié)合

Xilinx®SystemGeneratoRForDSP是用來協(xié)助系統(tǒng)設(shè)計(jì)的MATLABSimulink模塊集。SystemGeneratorforDSP在熟悉的MATLAB環(huán)境中引入XilinxFPGA對(duì)象,讓您能夠

2010-01-06 14:39:30 1181

1181

System Generator 工具由 MathWorks 與 Xilinx 合作開發(fā)而成,DSP 設(shè)計(jì)人員可使用 MATLAB 和Simulink 工具在 FPGA 內(nèi)進(jìn)行開發(fā)和仿真來完善 DSP 設(shè)計(jì)。 該工具為系統(tǒng)級(jí) DSP 設(shè)計(jì)與 FPGA 硬件實(shí)現(xiàn)的融合起

2011-05-11 18:36:23 224

224 該設(shè)計(jì)是基于System Generator設(shè)計(jì)平臺(tái),在Matlab/Simulink環(huán)境下搭建系統(tǒng)模型,再進(jìn)行功能仿真和驗(yàn)證,完成QPSK調(diào)制器的設(shè)計(jì)。仿真結(jié)果表明,所設(shè)計(jì)的調(diào)制器能產(chǎn)生正確QPSK波形,達(dá)到了預(yù)期效果

2011-10-17 16:10:51 65

65 最全面的fpga開發(fā)板電路圖,一共有10多份fpga開發(fā)板電路圖。

2012-04-19 12:50:50 133

133 本書系統(tǒng)地論述了Xilinx FPGA開發(fā)方法、開發(fā)工具、實(shí)際案例及開發(fā)技巧,內(nèi)容涵蓋Xilinx器件概述、Verilog HDL開發(fā)基礎(chǔ)與進(jìn)階、Xilinx FPGA電路原理與系統(tǒng)設(shè)計(jì)

2012-07-31 16:20:42 11268

11268

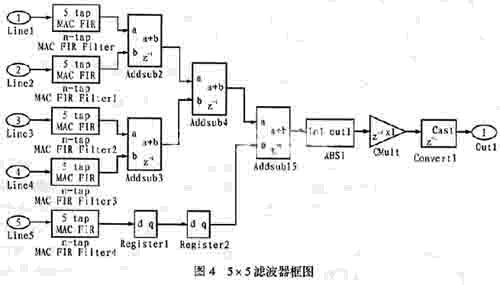

Xilinx公司推出的DSP設(shè)計(jì)開發(fā)工具System Generator是在Matlab環(huán)境中進(jìn)行建模,是DSP高層系統(tǒng)設(shè)計(jì)與Xilinx FPGA之間實(shí)現(xiàn)的橋梁。在分析了FPGA傳統(tǒng)級(jí)設(shè)計(jì)方法的基礎(chǔ)上,提出了基于System Generator的

2013-01-10 16:51:24 58

58 Xilinx FPGA工程例子源碼:System Generator的設(shè)計(jì)實(shí)例

2016-06-07 14:41:57 22

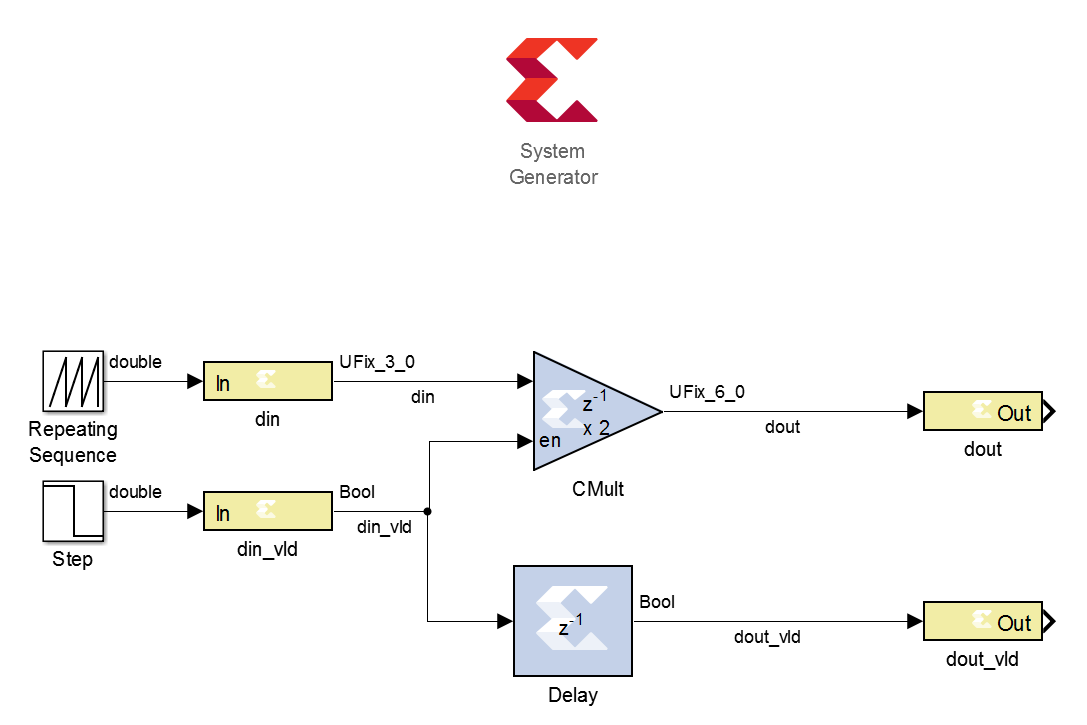

22 環(huán)境 ?Matlab 2014 a ?Vivado 2014.4 ?System generator 2014.4 實(shí)現(xiàn)步驟 1、模型搭建與仿真 在simulink環(huán)境下工程搭建如下 圖3 四路加

2017-02-08 01:10:08 473

473

提供支持。SDAccel允許開發(fā)人員用 OpenCL?、C和C++語言描述他們的算法,并直接編譯到賽靈思FPGA加速板。托管的賽靈思SDAccel? 開發(fā)環(huán)境不僅會(huì)加速FPGA開發(fā)進(jìn)

2017-02-08 16:06:08 228

228 最新版System Generator支持快速開發(fā)和實(shí)現(xiàn)基于All Programmable FPGA、SoC和MPSoC的無線電設(shè)計(jì) 賽靈思日前宣布推出高級(jí)設(shè)計(jì)工具System Generator

2017-02-09 01:23:41 279

279 一直都在System Generator下做圖像處理相關(guān)的算法,感覺SysGen挺強(qiáng)大的,前幾天突發(fā)奇想,能否直接用SysGen實(shí)現(xiàn)數(shù)據(jù)的通信呢,畢竟一句HDL代碼都不寫對(duì)于做FPGA的人來說卻是很有吸引力的。

2017-02-10 19:51:11 2618

2618

前一陣一直在忙,所以沒有來得及寫博文。弄完雜七雜八的事情,又繼續(xù)FPGA的研究。使用Verilog HDL語言和原理圖輸入來完成FPGA設(shè)計(jì)的方法都試驗(yàn)過了,更高級(jí)的還有基于System Generator和基于EDK/Microblaze的方法。

2017-02-11 03:10:11 8192

8192

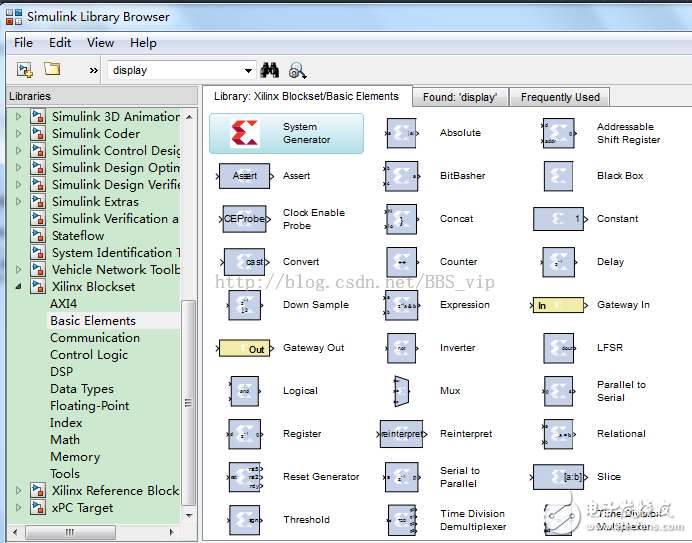

System Generator是Xilinx公司進(jìn)行數(shù)字信號(hào)處理開發(fā)的一種設(shè)計(jì)工具,它通過將Xilinx開發(fā)的一些模塊嵌入到Simulink的庫中,可以在Simulink中進(jìn)行定點(diǎn)仿真,可是設(shè)置

2017-02-11 11:53:11 3778

3778

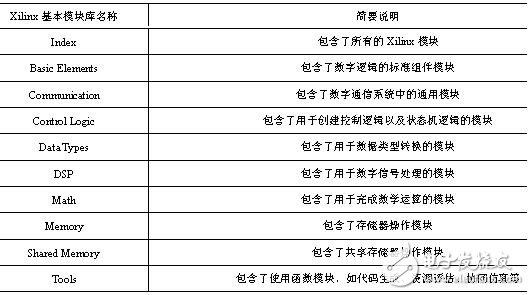

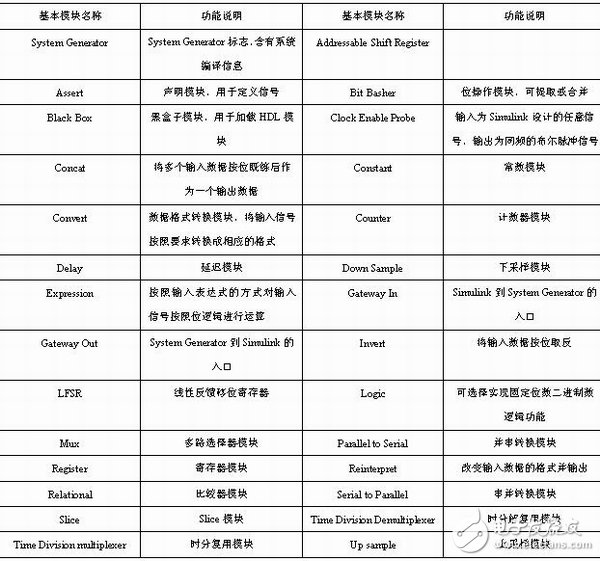

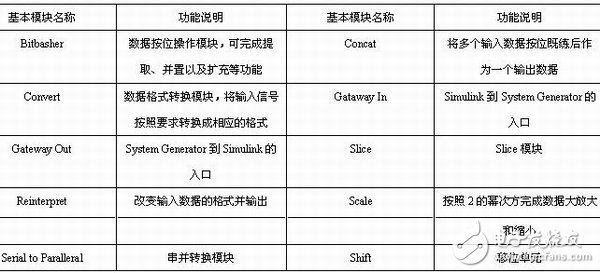

system generator是xilinx公司的系統(tǒng)級(jí)建模工具,它是擴(kuò)展mathworks公司的MATLAB下面的simulink平臺(tái),添加了XILINX FPGA專用的一些模塊。加速簡化了FPGA的DSP系統(tǒng)級(jí)硬件設(shè)計(jì)。

2017-02-11 19:21:33 7386

7386

利用System Generator軟件平臺(tái),實(shí)現(xiàn)基于模塊化建模方法的變換器建模,并簡化語言編寫控制系統(tǒng)的復(fù)雜過程。研究了從MATLAB-Xilinx環(huán)境中導(dǎo)出使用模塊化建模方法搭建的控制算法。通過

2017-11-15 14:31:34 4985

4985

在FPGA平臺(tái)上應(yīng)用System Generator工具實(shí)現(xiàn)了高精度頻率估計(jì)Rife算法。不同于傳統(tǒng)的基于HDL代碼和IP核的設(shè)計(jì)方法,采用System Generator工具可以使復(fù)雜算法

2017-11-18 09:01:51 2208

2208

Xilinx System Generator 是專門為數(shù)字信號(hào)算法處理而推出的模型化設(shè)計(jì)平臺(tái),可以快速、簡單地將DSP系統(tǒng)的抽象算法轉(zhuǎn)換成可綜合的、可靠的硬件系統(tǒng),彌補(bǔ)了大部分對(duì)C語言以及Matlab工具很熟悉的DSP工程師對(duì)于硬件描述語言VHDL和Verilog HDL認(rèn)識(shí)不足的缺陷。

2018-07-19 09:32:00 3716

3716

PLD/FPGA 常用開發(fā)軟件System Generator 9.10。 業(yè)內(nèi)領(lǐng)先的高級(jí)系統(tǒng)級(jí)FPGA開發(fā)高度并行系統(tǒng)。

2017-11-26 11:34:56 12

12 了解如何將Vivado HLS設(shè)計(jì)作為IP模塊整合到System Generator for DSP中。

了解如何將Vivado HLS設(shè)計(jì)保存為IP模塊,并了解如何將此IP輕松整合到System Generator for DSP的設(shè)計(jì)中。

2018-11-20 05:55:00 2940

2940 了解如何在System Generator中使用多個(gè)時(shí)鐘域,從而可以實(shí)現(xiàn)復(fù)雜的DSP系統(tǒng)。

2018-11-27 06:42:00 3450

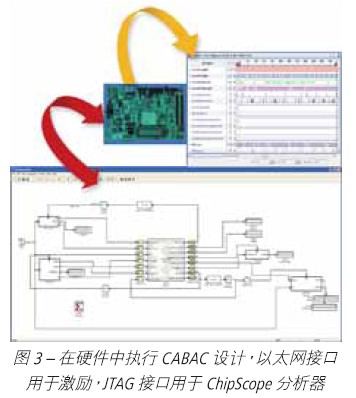

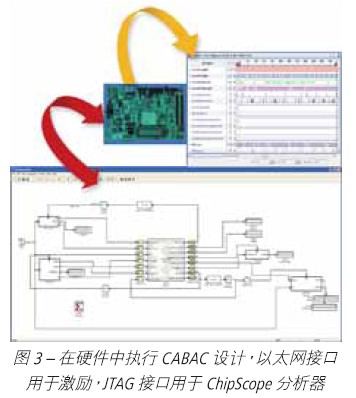

3450 了解如何使用Vivado System Generator for DSP進(jìn)行點(diǎn)對(duì)點(diǎn)以太網(wǎng)硬件協(xié)同仿真。

System Generator提供硬件協(xié)同仿真,可以將FPGA中運(yùn)行的設(shè)計(jì)直接整合到Simulink仿真中。

2018-11-23 06:02:00 4262

4262 System Generator 數(shù)字上下變頻 (DUC/DDC)模塊集的易用性大幅提升,使得更加便于無線算法開發(fā)。這些新型模塊還添加了有助于加速驗(yàn)證和編譯運(yùn)行時(shí)間的增強(qiáng)功能,所有這些模塊提供了七八種參數(shù)設(shè)置。

2019-07-31 09:22:49 2293

2293 FPGA的設(shè)計(jì)流程就是利用EDA開發(fā)軟件和編程工具對(duì)FPGA芯片進(jìn)行開發(fā)的過程。FPGA的開發(fā)流程一般包括功能定義/器件選型、設(shè)計(jì)輸入、功能仿真、邏輯綜合、布局布線與實(shí)現(xiàn)、編程調(diào)試等主要步驟。

2019-11-06 15:17:28 2224

2224 本篇博文是面向希望學(xué)習(xí) Xilinx System Generator for DSP 入門知識(shí)的新手的系列博文第一講。其中提供了有關(guān)執(zhí)行下列操作的分步操作方法指南。

2022-02-16 16:21:36 1578

1578

Xilinx FPGA開發(fā)實(shí)用教程資料包免費(fèi)下載。

2022-04-18 09:43:46 24

24 開發(fā)FPGA設(shè)計(jì),最終的產(chǎn)品是要落在使用FPGA芯片完成某種功能。所以我們首先需要一個(gè)帶有Intel FPGA芯片的開發(fā)板。

2023-07-14 09:42:11 2052

2052

FPGA開發(fā)板與Linux開發(fā)板是兩種不同的硬件開發(fā)平臺(tái),各自具有不同的特點(diǎn)和應(yīng)用場景。在以下的文章中,我將詳細(xì)介紹FPGA開發(fā)板和Linux開發(fā)板的區(qū)別。 基本概念和原理 FPGA

2024-02-01 17:09:31 385

385 FPGA開發(fā)板是一種基于FPGA(現(xiàn)場可編程門陣列)技術(shù)的開發(fā)平臺(tái),它允許工程師通過編程來定義和配置FPGA芯片上的邏輯電路,以實(shí)現(xiàn)各種數(shù)字電路和邏輯功能。FPGA開發(fā)板通常包括FPGA芯片、時(shí)鐘模塊、電源模塊、輸入輸出接口等組件,并提供相應(yīng)的編程軟件和開發(fā)工具,方便工程師進(jìn)行電路設(shè)計(jì)和調(diào)試。

2024-03-14 18:20:29 553

553 配置內(nèi)部的邏輯門和連接關(guān)系來實(shí)現(xiàn)特定的電路功能。因此,FPGA開發(fā)實(shí)質(zhì)上是一種將軟件算法或硬件電路轉(zhuǎn)化為可編程邏輯結(jié)構(gòu)的過程,以實(shí)現(xiàn)各種復(fù)雜的邏輯和數(shù)據(jù)處理任務(wù)。

2024-03-15 14:28:56 76

76

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論