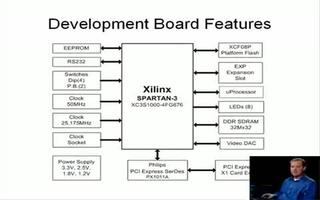

賽靈思 Spartan-3開發板成為作者改進其軟件教育用的Oberon 編程語言和編譯器的基礎。

1988 年,Jürg Gutknecht 和我一起完成并出版了Oberon 編程語言[1,2],其為我職業生涯早期開發的另外兩種編程語言Pascal 和Modula-2 的后續版本。與Modula-2 相比,我們最初設計Oberon 編程語言力求更加精簡和高效,以便能夠更好地幫助教學人員為計算機科學專業的學生教授系統編程。我們再接再勵,于1990 年針對可采用windows 系統和具有字處理能力的工作站開發了Oberon 操作系統(OS),以此作為工作站的現代實現方式。接著,我們出版了一本書,名為《Project Oberon》,詳細講解了Oberon 編譯器以及與之同名的操作系統。此外,書中還包括詳細的指令和源代碼。

幾年前,我的朋友Paul Reed 建議我重新修訂并再次出版這本書,不僅因為這本書對系統設計教學具有重要價值,同時還因為這本書可以作為良好的切入點,幫助那些想要成為創新者的人們從零基礎構建可靠的系統。

然而,我當時實際上是遇到了很大的困難。我最初開發的編譯器是將已基本消失了的處理器作為目標。因此,我的解決辦法就是為現代處理器重新編寫編譯器。但在做了不少研究之后,我無法找到一款能夠在清晰度、規律性和簡潔性上符合我標準的處理器。因此,我自己設計了這款編譯器。而我之所以能夠將該想法付諸實現,都是因為現代FPGA 能夠幫助我設計硬件以及系統軟件。更重要的是,選擇賽靈思FPGA 能幫助我更新系統,同時讓設計盡可能接近自1990 年以來的原始版本。

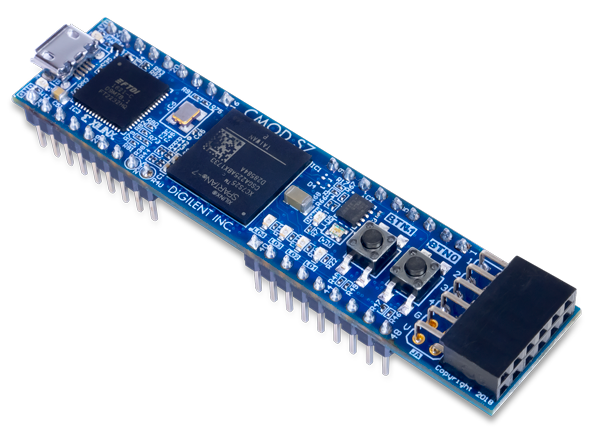

實現在低成本Digilent Spartan?-3開發板上的新型處理器RISC 負責托管1MB 靜態RAM (SRAM) 內存。我唯一添加的系統硬件就是一個鼠標接口和一個用來替換舊系統中硬盤驅動器的SD 卡。

這本書和面向整個系統的源代碼可在projectoberon.com[3,4,5] 中查閱,也可在該網站上名為 S3RISCinstall.zip. 的單個文件中進行查閱。該文件包含指令、SD 卡文件系統圖像和FPGA 配置比特文件(對于Spartan-3開發板的 Platform Flash,此為PROM文件形式),以及SD 卡/ 鼠標接口硬件的構造詳圖。

RISC處理器

該處理器由算術邏輯單元、由16 個32 位寄存器組成的陣列和帶指令寄存器、IR 及程序計數器PC 的控制單元組成。Verilog 模塊RISC5 就是該處理器的典型代表。

該處理器具有20 種指令:4 種用于移動、偏移和旋轉;4 種用于邏輯運算;4 種用于整數運算;4 種用于浮點運算;2 種用于存儲器訪問;2 種用于分支。

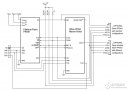

RISC5 通過運行環境RISC5Top導入。該運行環境包括到各種(內存映射)器件和SRAM(256M×32 位)的接口。整個系統(圖1)包括以下Verilog 模塊(見行統計):

?

圖1 – 該系統及其所含Verilog模塊的方框圖

?

?

我將內存映射到黑白VGA 顯示器中,這樣它只占用1024×768×1位/ 像素=98304 字節,基本上占 1MB 可用主內存的10%。該SD 卡將取代初始系統中80MB 的硬盤驅動器,其可通過能夠接受并序列化字節或32 位字的標準SPI 接口進行存取。鍵盤和鼠標通過標準PS-2 串行接口連接。此外,還提供一根串行異步的RS-232 線和一個通用8 位并行的I/O接口。模塊RISC5Top 還帶有一個每毫秒采用增量式計數的計數器。

OBERON操作系統

該操作系統軟件由包括內存分配器(帶垃圾回收器)的內核、文件系統以及引導載入程序、文本系統、瀏覽器系統和文本編輯器組成。

名為“Oberon”的模塊是中心任務調度程序,而“System”是基礎命令模塊。通過點擊顯示器上任何瀏覽器文本“M.P”上的中間按鈕即可觸發動作,其中P 是模塊M 聲明的程序名。如果M 不存在,則會自動加載。但是,大多數文本編輯命令是通過簡單的鼠標點擊觸發的。其中,左邊一欄按鈕用來設置" 脫字" 符,標記文本位置,右邊一欄按鈕用來選擇文本字段(text stretch)。

“Kernel”模塊包括磁盤存儲管理和垃圾回收器。我保證觀察瀏覽器是平鋪的,不重疊。標準布局顯示了多個瀏覽器的兩條垂直軌跡。只需拖動標題欄,就可以放大、縮小或移動它們。圖2 顯示了在顯示器上運行的用戶界面以及Spartan-3 開發板、鍵盤及鼠標。

?

圖2 - 顯示用戶界面的顯示器(Spartan-3開發板在右側)

加載時系統占用模塊空間112640字節(21%),占堆(heap) 的16128字節(3%)。系統包括所以下幾個模塊(見行統計),如圖3 所示:

?

圖3 - 系統及其模塊

?

?

值得注意的是,該系統在加電或重置時,完成初始化僅需兩秒鐘。這包括文件目錄中垃圾回收掃描。

OBERON編譯器

系統自帶的編譯器采用簡單的自上而下遞歸下降分析法。用戶使用ORP.Compile @ 命令即可激活模塊選定的源文本上的編譯器。 包解析器通過掃描儀輸入各種符號,包括識別符、數字和特殊符號(如BEGIN、END、+等)。該方案已被證明在許多應用中有效且均表現不凡。這點在我著的書《編譯器結構》[6,7] 中有詳細說明。

該包解析器調用代碼生成程序模塊中的程序。這些程序直接將指令添加在代碼陣列上。如果已知所有分支目的地,向前跳轉指令(forwardbranch instructions)在模塊編譯結束時則會提供跳轉地址(修正)。

所有可變地址都與基址寄存器關聯。這就是用于局部變量(運行時設置在程序輸入)的R14(堆棧指示器)或用于全局和輸入變量的R13。

基址地址按要求通過地址保存在寄存器R12 內的系統全局模塊表載入。R15 用于RISC 架構確定的返回地址(鏈接)。因此,R0-R11 可用于表達式評估和傳遞過程參數。

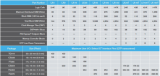

整個編譯器由4 個相對較小的有效模塊組成(見行統計):

?

編譯器占用115912 字節(22%)的模塊空間和17508 字節(4%)的堆空間(編譯之前)。其源代碼長約65KB。編譯器自身的編譯在25 MHzRISC 處理器上只需幾秒鐘[8]。

編譯器通常使用值為NIL 的指示檢查數組索引和基準值。如果違反規定,這會造成陷阱。這種技術具有高度的安全性,防止錯誤和崩潰。事實上,只能通過采用偽模塊SYSTEM 中的操作,即PUT 和COPY,才能防礙系統的完整性。這些操作必須局限于接入器件接口的驅動模塊。在輸入列表中,通過SYSTEM 很容易識別它們。整個系統采用Oberon 編程,無需使用匯編碼。

我選擇Digilent Spartan-3 開發板是由于其成本低、操作簡便,這使其適于教育機構,以獲得整套課堂教學套件。一個重大優勢就是該開發板上有靜態RAM,使得接口連接非常簡單直觀(甚至用于字節選擇)。遺憾的是,所有新開發板均采用動態RAM,雖然存儲空間更大,但接口連接復雜得多,因此刷新和初始化(校準)需要電路。這一電路與帶靜態RAM 的整個處理器一樣復雜。即使控制器以單片式提供,這有悖于我們的開放檢查原則。

最后的想法

40 多年前,C.A.R. Hoare 說,在科學技術的所有分支學科中,學生在被要求用實驗嘗試自己的想法之前,容易受到許多示范性設計實例的影響。編程和軟件設計與這種明智模式形成了鮮明對比。這里,在閱讀任何實例之前,要求學生從一開始就編寫程序。

這種可怕事實的原因就是:幾乎不存在大小合適的示范實例。因此,我決定稍微修正這種情形,我在1975年編寫了《算法與數據結構》一書。隨后(與J. Gut-knecht)負責操作系統教學任務,我設計了Oberon 系統(1986-88)。

此后,編程教學并沒有明顯提高,而系統的規模和復雜性顯著增加。雖然開源的努力頗受歡迎,但它并沒有真正改變這種形勢,因為大多數程序已經建成“運行”,但卻沒有真正投入使用。

我繼續大膽提議,應重新設計所有程序,不光是計算機,還有讀取方式。這些程序應是可發行的。即便這種方法正確而有效,但這是一項比創建可執行程序更為艱難的任務。這意味著,沒有任何部分必須用匯編碼指定。

忽略在這種“人為因素”的結果就是,在許多地方,新的應用沒有得到精心設計,而是通過消除程序中錯誤來實現,其結果有時是令人擔憂的。要做到“易懂”的關鍵就是堅持簡單性和規律性,放棄不必要的修飾,避免花里胡哨,正確區分傳統與便捷。

該系統所占空間小,是小資源實現大作為的見證。雖然Oberon 系統包含一個文件系統、文本編輯器和瀏覽器(Windows)管理程序,但相比多數現代操作系統而言,其占用的空間少得可憐。意外的是它僅僅依靠一些簡單規則,因此便于學習如何使用。

最后,這種簡單的系統的另一大優勢就是,用戶可以在該基礎系統上安全構建所需程序,而不必擔心是否存在未知特征與功能,如后門程式(back door)。從系統完整性易受到攻擊的角度看,這是一個基本屬性,是關鍵安全型應用不可或缺的。值得注意的是,我們的系統硬件沒有這種隱藏元件。畢竟,在如此之大而又沒人能夠完全了解的基礎上構建的任何系統也不能予以保證。

致謝

我衷心感謝Paul Reed 所做的寶貴貢獻。他建議我重新編撰《Oberon 項目》一書,還建議在FPGA 上重新實現整個系統。Paul 一直激勵著我。他想到過用SD 卡替代磁盤,他為SPI、PS-2 和Verilog 中的VID 接口做出了卓越貢獻。

?

電子發燒友App

電子發燒友App

評論