摘要:在高性能雷達(dá)信號(hào)處理機(jī)研制中,高速串行總線(xiàn)正逐步取代并行總線(xiàn)。業(yè)界廣泛使用的Xilinx公司Virtex-6系列FPGA支持多種高速串行通信協(xié)議,本文針對(duì)其中較為常用的Aurora 8B/10B和PCI Express 2.0,Serial RapidIO 2.0三種協(xié)議進(jìn)行了測(cè)試及對(duì)比分析。首先搭建了基于Virtex-6 FPGA的高速串行協(xié)議測(cè)試平臺(tái);然后設(shè)計(jì)并分別實(shí)現(xiàn)了三種協(xié)議的高速數(shù)據(jù)通信,測(cè)算了協(xié)議的實(shí)際傳輸速率;最后結(jié)合測(cè)試結(jié)果,從協(xié)議層次結(jié)構(gòu)、鏈路數(shù)目、鏈路線(xiàn)速率、數(shù)據(jù)傳輸方式、協(xié)議開(kāi)銷(xiāo)、拓?fù)浣Y(jié)構(gòu)、設(shè)備尋址方式、應(yīng)用領(lǐng)域等方面對(duì)三種協(xié)議進(jìn)行了比較。本文研究工作可為三種協(xié)議的選用、測(cè)試和工程實(shí)現(xiàn)提供參考。

1 引言

隨著雷達(dá)帶寬和AD采樣率的提高,在高性能雷達(dá)信號(hào)處理機(jī)研制中,系統(tǒng)對(duì)數(shù)據(jù)傳輸帶寬的要求不斷增加,高速串行總線(xiàn)正逐步取代傳統(tǒng)的并行總線(xiàn)。

Xilinx公司推出的Virtex-6系列FPGA,在片上集成了固化的GTX模塊,以提供高速串行通信支持。同時(shí)Xilinx公司提供有多種串行通信協(xié)議IP核,便于用戶(hù)進(jìn)行開(kāi)發(fā)。Aurora 8B/10B,PCI Express 2.0和Serial RapidIO 2.0是其中較為常用的三種協(xié)議。目前已有眾多文獻(xiàn)涉及到三種協(xié)議基于FPGA的實(shí)現(xiàn)方案[2][3][4]。然而這些方案未能充分發(fā)揮協(xié)議性能,存在線(xiàn)速率較低(僅為2.5Gb/s)或未實(shí)現(xiàn)多通道綁定。針對(duì)上述問(wèn)題,本文基于Virtex-6 FPGA,分別實(shí)現(xiàn)了三種協(xié)議在4x鏈路,5.0Gb/s線(xiàn)速率模式下的數(shù)據(jù)通信,測(cè)得協(xié)議的實(shí)際傳輸速率,并對(duì)三種協(xié)議的特點(diǎn)與應(yīng)用進(jìn)行了對(duì)比分析。

2 測(cè)試平臺(tái)簡(jiǎn)介

本文以實(shí)驗(yàn)室自行開(kāi)發(fā)設(shè)計(jì)的PCIe光纖接收處理板(以下簡(jiǎn)稱(chēng)測(cè)試電路板)為測(cè)試平臺(tái)。測(cè)試電路板的結(jié)構(gòu)圖和實(shí)物圖分別如圖1,圖2所示。其中,F(xiàn)PGA選用XC6VLX240T-2FF1156,該芯片含20個(gè)GTX收發(fā)器,鏈路線(xiàn)速率可達(dá)6.6Gb/s。DSP選用TMS320C6678,該芯片含有SRIO接口,支持1x、2x和4x鏈路。光電轉(zhuǎn)換模塊選用FCBG410QB1C10,它包含4條鏈路,帶寬可達(dá)40Gb/s。故而測(cè)試電路板的硬件設(shè)計(jì)符合本測(cè)試對(duì)數(shù)據(jù)傳輸速率的要求。

?

圖1 測(cè)試電路板模塊結(jié)構(gòu)和鏈路連接圖

?

?

如圖3所示,將測(cè)試電路板插入服務(wù)器主板的PCIe插槽中,并將光纖接入測(cè)試電路板,完成測(cè)試平臺(tái)的搭建。本測(cè)試中,PCI Express 2.0協(xié)議用于實(shí)現(xiàn)FPGA與服務(wù)器的數(shù)據(jù)通信,Serial RapidIO 2.0協(xié)議用于實(shí)現(xiàn)FPGA與DSP的數(shù)據(jù)通信,Aurora 8B/10B協(xié)議用于實(shí)現(xiàn)FPGA的光纖自發(fā)自收通信。由于三種協(xié)議都在物理層進(jìn)行8B/10B編碼,故在本測(cè)試工作模式下,它們的極限速率均為。

? ? ? ? ? ? ? ? ?

3 AURORA 8B/10B通信測(cè)試

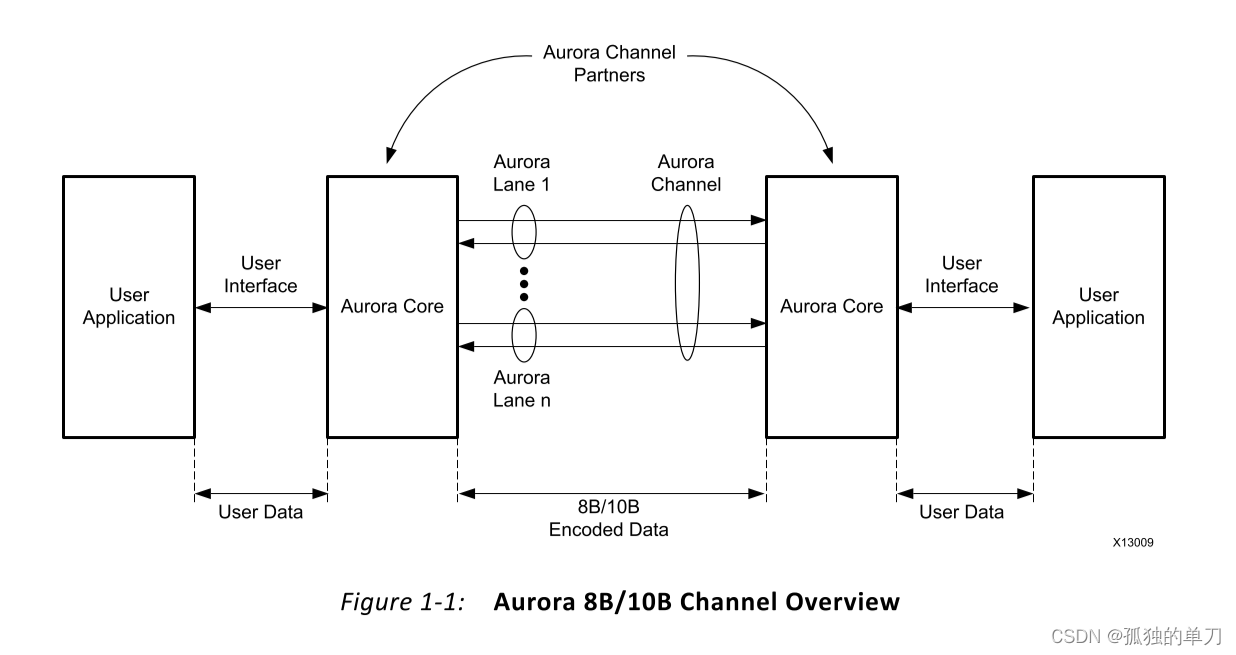

Aurora 8B/10B協(xié)議是Xilinx公司針對(duì)高速傳輸開(kāi)發(fā)的一種可裁剪的輕量級(jí)鏈路層協(xié)議,通過(guò)一條或多條串行鏈路實(shí)現(xiàn)兩設(shè)備間的數(shù)據(jù)傳輸。協(xié)議Aurora協(xié)議可以支持流和幀兩種數(shù)據(jù)傳輸模式,以及全雙工、單工等數(shù)據(jù)通信方式[5]。

本測(cè)試中,Aurora 8B/10B IP核配置為雙工、流模式,參考時(shí)鐘頻率250MHz。

使用ChipScope軟件觀察FPGA相關(guān)信號(hào)如圖4所示。觀察RX_SRC_RDY_N可以發(fā)現(xiàn),平均每4992周期出現(xiàn)7個(gè)周期的數(shù)據(jù)無(wú)效信號(hào)。由于接收數(shù)據(jù)時(shí)鐘頻率為250MHz,數(shù)據(jù)位寬為64bit,故本測(cè)試中,Aurora 8B/10B協(xié)議單向傳輸速率為:

?

下面分析協(xié)議理論傳輸速率和實(shí)際通信效率。該協(xié)議的幀格式比較簡(jiǎn)單,除2字節(jié)的起始標(biāo)志,2字節(jié)終止標(biāo)志和至多1字節(jié)的填裝字符外,其余為數(shù)據(jù)部分。本測(cè)試采用的流模式是以無(wú)結(jié)尾的幀方式實(shí)現(xiàn)。故協(xié)議除8B/10B編碼外,基本上不存在其他開(kāi)銷(xiāo)。故根據(jù)(1)式可得,協(xié)議的理論速率為2.0GB/s,協(xié)議的實(shí)際通信效率為99.75%。

4 PCI Express 2.0通信測(cè)試

PCI Express(簡(jiǎn)稱(chēng)PCIe)總線(xiàn)技術(shù)是取代PCI的第三代I/O技術(shù)。PCIe采用串行點(diǎn)對(duì)點(diǎn)互連,允許每個(gè)設(shè)備擁有專(zhuān)屬的一條連接,不爭(zhēng)奪帶寬資源,同時(shí)保證了數(shù)據(jù)的完整性。PCI Express 2.0協(xié)議的鏈路線(xiàn)速率達(dá)到5Gb/s,最高支持32x鏈路。

本測(cè)試中,PCIe 2.0通信測(cè)試通過(guò)FPGA對(duì)服務(wù)器內(nèi)存的DMA讀/寫(xiě)操作來(lái)實(shí)現(xiàn)。

服務(wù)器方面,本測(cè)試選用Windriver軟件進(jìn)行PCIe驅(qū)動(dòng)程序的開(kāi)發(fā)。利用該軟件提供的PCIe驅(qū)動(dòng)程序及用戶(hù)接口函數(shù),編寫(xiě)符合本測(cè)試功能需求的程序。

FPGA方面,本測(cè)試通過(guò)設(shè)計(jì)用戶(hù)模塊,實(shí)現(xiàn)對(duì)PCIe IP核的控制,完成DMA讀/寫(xiě)操作。FPGA模塊結(jié)構(gòu)如圖5所示。

?

圖5 PCIe 2.0通信測(cè)試FPGA模塊結(jié)構(gòu)

為便于服務(wù)器對(duì)測(cè)試電路板FPGA進(jìn)行控制,在FPGA的PCIe存儲(chǔ)空間模塊中,定義了若干控制/狀態(tài)寄存器,這些寄存器的作用有:DMA讀/寫(xiě)初始化,控制DMA讀/寫(xiě)的啟動(dòng)與停止,標(biāo)志一次DMA傳輸是否完成,設(shè)置一次DMA傳輸?shù)臄?shù)據(jù)量等。

服務(wù)器通過(guò)PCIe接口對(duì)測(cè)試板FPGA控制/狀態(tài)寄存器進(jìn)行讀/寫(xiě)操作,來(lái)控制DMA的進(jìn)程。每次DMA完成后,處理板FPGA會(huì)向服務(wù)器CPU發(fā)送一次中斷。服務(wù)器對(duì)測(cè)試電路板FPGA DMA傳輸?shù)目刂屏鞒倘鐖D6所示。

?

圖6 PCIe 2.0 DMA傳輸控制流程圖

本測(cè)試將TLP包載荷數(shù)設(shè)為256Bytes(IP核允許的最大值),每次DMA傳輸?shù)腡LP包的數(shù)量為16384,故每次DMA傳輸?shù)臄?shù)據(jù)量為4MB。使用ChipScope軟件觀察FPGA內(nèi)部的PCIe 2.0 DMA讀/寫(xiě)相關(guān)信號(hào),如圖7,圖8所示。本測(cè)試開(kāi)發(fā)了PCIe讀寫(xiě)功能測(cè)試軟件,實(shí)現(xiàn)PCIe傳輸數(shù)據(jù)量和傳輸速率的實(shí)時(shí)顯示。傳輸速率通過(guò)1s內(nèi)DMA傳輸完成的次數(shù)來(lái)計(jì)算。測(cè)試結(jié)果如圖9(a)、(b)所示。PCIe 2.0 DMA讀的數(shù)據(jù)傳輸速率為1.770GB/s,DMA寫(xiě)的數(shù)據(jù)傳輸速率為1.820GB/s。

?

圖7 PCIe 2.0 DMA讀測(cè)試信號(hào)波形

?

?

圖8 PCIe 2.0 DMA寫(xiě)測(cè)試信號(hào)波形

?

?

圖9 PCIe 2.0 DMA讀寫(xiě)速率測(cè)試結(jié)果

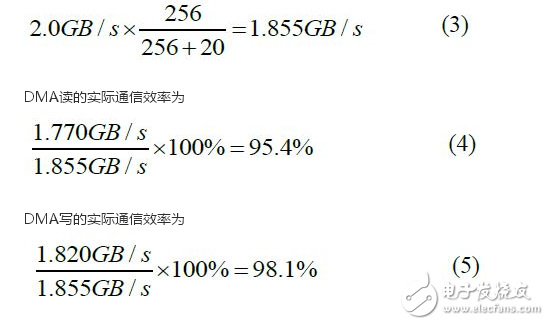

下面分析并計(jì)算本測(cè)試條件下PCIe 2.0 DMA讀/寫(xiě)的理論傳輸速率和實(shí)際通信效率。

PCIe 2.0協(xié)議主要開(kāi)銷(xiāo)為8B/10B編碼開(kāi)銷(xiāo)和數(shù)據(jù)包傳送開(kāi)銷(xiāo)[6]。PCIe總線(xiàn)以包的形式在不同器件之間交換信息。數(shù)據(jù)在進(jìn)入處理層后會(huì)被封裝一個(gè)包頭,該包頭長(zhǎng)度在32bit地址下為12字節(jié)(本測(cè)試采用32bit地址)。當(dāng)數(shù)據(jù)包進(jìn)入數(shù)據(jù)鏈路層后,會(huì)添加2字節(jié)的序列號(hào)和4字節(jié)的LCRC字段。數(shù)據(jù)包進(jìn)入物理層后,使用1字節(jié)的開(kāi)始字符和1字節(jié)的結(jié)束字符將其封裝成幀。

在DMA寫(xiě)測(cè)試中,F(xiàn)PGA每發(fā)送一次存儲(chǔ)器寫(xiě)報(bào)文(含256字節(jié)數(shù)據(jù))會(huì)帶來(lái)20字節(jié)的額外開(kāi)銷(xiāo)。在DMA讀測(cè)試中,F(xiàn)PGA向服務(wù)器發(fā)送存儲(chǔ)器讀報(bào)文,并由服務(wù)器返回完成報(bào)文(含256字節(jié)數(shù)據(jù))。每返回一次完成報(bào)文會(huì)帶來(lái)20字節(jié)的額外開(kāi)銷(xiāo)。由于PCIe 2.0定義了流量控制緩存管理機(jī)制,允許服務(wù)器返回完成報(bào)文的同時(shí)接收FPGA發(fā)來(lái)的存儲(chǔ)器讀報(bào)文,故DMA讀測(cè)試中可忽略FPGA發(fā)送存儲(chǔ)器讀報(bào)文帶來(lái)的開(kāi)銷(xiāo)。

故PCIe 2.0 DMA讀/寫(xiě)的理論速率相同,均為

5 Serial RapidIO 2.0通信測(cè)試

RapidIO是針對(duì)嵌入式系統(tǒng)芯片間和板間互連而設(shè)計(jì)的一種開(kāi)放式的基于包交換的高速串行標(biāo)準(zhǔn),已在電信、國(guó)防等行業(yè)大量使用。

Serial RapidIO(簡(jiǎn)稱(chēng)SRIO)是物理層采用串行差分模擬信號(hào)傳輸?shù)腞apidIO標(biāo)準(zhǔn)。SRIO 2.0協(xié)議性能進(jìn)一步增強(qiáng),鏈路線(xiàn)速率可達(dá)6.25Gb/s,在電氣層支持熱插拔,并新添了控制符號(hào)和空閑模式功能。

本測(cè)試以測(cè)試電路板FPGA作為發(fā)起端,以測(cè)試電路板DSP作為目標(biāo)端。通過(guò)FPGA向DSP發(fā)送SWRITE包,進(jìn)行SRIO 2.0寫(xiě)測(cè)試,通過(guò)FPGA向DSP發(fā)送NREAD包,DSP向FPGA返回RESPONSE包,進(jìn)行SRIO 2.0讀測(cè)試。

FPGA模塊結(jié)構(gòu)如圖10所示。通過(guò)VIO控制模塊,可對(duì)包事務(wù)類(lèi)型、包載荷、發(fā)送地址等參數(shù)進(jìn)行設(shè)置。本測(cè)試將包載荷設(shè)為256字節(jié),讀/寫(xiě)內(nèi)存空間設(shè)為DSP的MSM(Multi-core Shared Memory)空間。

?

圖10 SRIO 2.0通信測(cè)試FPGA模塊結(jié)構(gòu)

DSP方面,需要進(jìn)行相關(guān)寄存器的配置,完成SRIO的初始化,使DSP作為目標(biāo)端處理FPGA發(fā)來(lái)的SRIO讀/寫(xiě)請(qǐng)求。DSP主要配置流程包括使能SRIO接口,串并轉(zhuǎn)換模塊,鏈路數(shù)目,鏈路線(xiàn)速率,設(shè)備ID等參數(shù)的設(shè)置。

使用ChipScope軟件觀察FPGA相關(guān)信號(hào),如圖11,圖12所示。

?

圖11 SRIO 2.0讀測(cè)試信號(hào)波形

?

?

圖12 SRIO 2.0寫(xiě)測(cè)試信號(hào)波形

本測(cè)試中,F(xiàn)PGA每連續(xù)發(fā)送16384個(gè)SWRITE或NREAD包后,都會(huì)向DSP再發(fā)送1個(gè)門(mén)鈴消息。因此,可以通過(guò)計(jì)算DSP收到的相鄰兩個(gè)門(mén)鈴的時(shí)間間隔來(lái)計(jì)算SRIO讀/寫(xiě)速率。

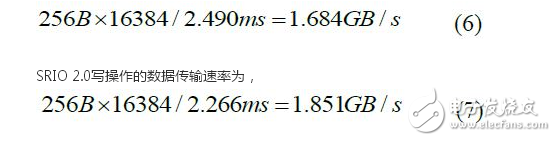

經(jīng)測(cè)算,當(dāng)FPGA執(zhí)行SRIO讀/寫(xiě)操作時(shí), DSP接收的相鄰兩個(gè)門(mén)鈴的平均時(shí)間間隔為分別為2.490ms,2.266ms。故SRIO 2.0讀操作的數(shù)據(jù)傳輸速率為,

?

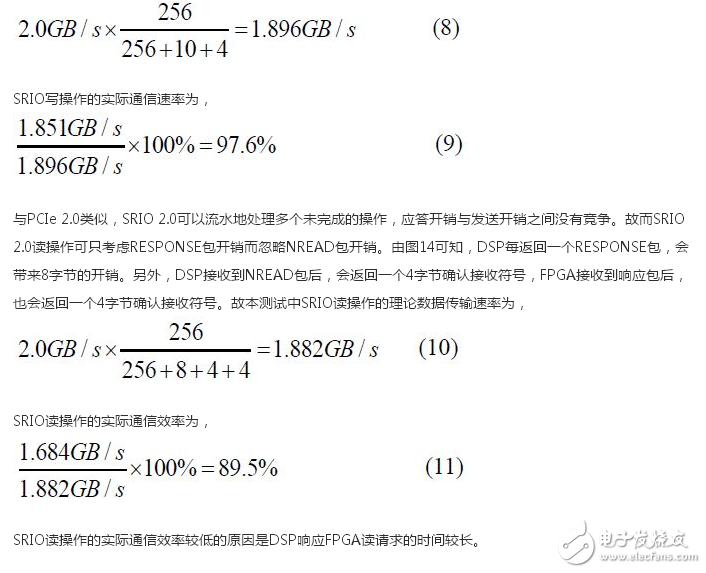

下面計(jì)算本測(cè)試條件下SRIO讀/寫(xiě)的理論數(shù)據(jù)傳輸速率和實(shí)際通信效率。

SRIO 2.0協(xié)議的主要開(kāi)銷(xiāo)為物理層編碼開(kāi)銷(xiāo)和數(shù)據(jù)包開(kāi)銷(xiāo)。本測(cè)試采用8位路由和34位偏移地址。該條件下SWRITE事務(wù)、RESPONSE事務(wù)的數(shù)據(jù)包結(jié)構(gòu)分別如圖13、圖14所示。

?

圖13 SRIO 2.0 SWRITE包結(jié)構(gòu)

?

?

圖14 SRIO 2.0 RESPONSE包結(jié)構(gòu)

由圖13可知,F(xiàn)PGA每發(fā)送一個(gè)SWRITE包,會(huì)帶來(lái)10字節(jié)的開(kāi)銷(xiāo),另外,DSP會(huì)返回一個(gè)4字節(jié)確認(rèn)接收符號(hào)。故本測(cè)試中SRIO寫(xiě)操作的理論數(shù)據(jù)傳輸速率為,

6 三種協(xié)議的分析比較

本測(cè)試中,Aurora 8B/10B、PCIe 2.0、SRIO 2.0均實(shí)現(xiàn)了在4x模式下的高速數(shù)據(jù)傳輸。下面將結(jié)合測(cè)試結(jié)果和協(xié)議的具體內(nèi)容,從以下各方面對(duì)三種協(xié)議進(jìn)行比較。

(1)協(xié)議分層結(jié)構(gòu)

Aurora 8B/10B協(xié)議僅定義了鏈路層和物理層。屬于較為底層的協(xié)議。SRIO 2.0協(xié)議定義了物理層,傳輸層和邏輯層,PCIe 2.0協(xié)議定義了物理層,數(shù)據(jù)鏈路層,事務(wù)層和軟件層,這兩種協(xié)議的內(nèi)容和功能均比Aurora 8B/10B協(xié)議復(fù)雜。

(2)鏈路數(shù)目和鏈路線(xiàn)速率

Aurora 8B/10B協(xié)議在鏈路數(shù)目和鏈路線(xiàn)速率選擇上比較靈活,鏈路數(shù)目可以在1x至16x之間自由選擇,鏈路線(xiàn)速率可以在0.5Gb/s到6.6Gb/s間自由選擇。PCIe 2.0支持1x,2x,4x,8x,12x,16x,32x鏈路,鏈路線(xiàn)速率支持2.5Gb/s和5.0Gb/s。SRIO 2.0支持1x、2x、4x、8x和16x鏈路,鏈路線(xiàn)速率支持1.25Gb/s、2.5Gb/s、3.125Gb/s、5.0Gb/s和6.25Gb/s。

綜上可知,在鏈路線(xiàn)速率選擇范圍的廣泛性和靈活性上,

Aurora 8B/10B>Srio 2.0>Pcie 2.0,

鏈路數(shù)目選擇的靈活性上,

Aurora 8B/10B>Pcie 2.0>Srio 2.0。

最大允許的鏈路數(shù)目上,

Pcie 2.0>Aurora 8B/10B=Srio 2.0。

(3)數(shù)據(jù)傳輸方式

Aurora 8B/10B協(xié)議在數(shù)據(jù)封裝過(guò)程中未添加地址,設(shè)備號(hào)等信息,不能對(duì)目標(biāo)設(shè)備的存儲(chǔ)空間進(jìn)行讀寫(xiě)。

PCIe 2.0可通過(guò)Memory Write,Memory Read,I/O Write,I/O Read事務(wù)對(duì)目標(biāo)設(shè)備地址空間進(jìn)行讀寫(xiě),但必須具備對(duì)目標(biāo)設(shè)備地址空間的可見(jiàn)性。

SRIO 2.0數(shù)據(jù)傳輸方式更為靈活。在具備對(duì)目標(biāo)設(shè)備地址空間可見(jiàn)性的情況下,可通過(guò)NWRITE,NWRITE_R,SWRITE,NREAD,ASTOMIC等事務(wù)對(duì)目標(biāo)設(shè)備的地址空間進(jìn)行直接讀寫(xiě)。在不具備目標(biāo)設(shè)備地址空間可見(jiàn)性的情況下,SRIO還提供了消息傳遞機(jī)制。用戶(hù)將數(shù)據(jù)和信箱號(hào)通過(guò)MESSAGE事務(wù)發(fā)至目標(biāo)設(shè)備,目標(biāo)設(shè)備根據(jù)信箱號(hào)與自身存儲(chǔ)空間的映射關(guān)系將數(shù)據(jù)寫(xiě)入存儲(chǔ)空間。

綜上可知,數(shù)據(jù)傳輸方式的靈活性上,SRIO 2.0>PCIe 2.0>Aurora 8B/10B。

(4)協(xié)議開(kāi)銷(xiāo)和數(shù)據(jù)傳輸速率

三種協(xié)議均在物理層有20%的8B/10B編碼開(kāi)銷(xiāo)。Aurora 8B/10B協(xié)議除此之外基本上無(wú)其它開(kāi)銷(xiāo),而PCIe 2.0,SRIO 2.0還存在數(shù)據(jù)包開(kāi)銷(xiāo)。與PCIe 2.0相比,SRIO 2.0的數(shù)據(jù)包格式更為簡(jiǎn)潔,在相同的包載荷大小下,開(kāi)銷(xiāo)更低。以256B包載荷為例,SRIO 2.0的數(shù)據(jù)包開(kāi)銷(xiāo)最低為5.4%(SWRITE事務(wù)),而PCIe 2.0的數(shù)據(jù)包開(kāi)銷(xiāo)最低為7.3%(Memory Write事務(wù))。然而,PCIe 2.0協(xié)議最大允許的包載荷為4KB,而SRIO最大允許的包載荷為256B。故PCIe 2.0協(xié)議可通過(guò)增大包載荷來(lái)達(dá)到更低的數(shù)據(jù)包開(kāi)銷(xiāo)。(4KB包載荷下,PCIe 2.0的數(shù)據(jù)包開(kāi)銷(xiāo)為0.5%)

協(xié)議的理論傳輸速率由通道帶寬和協(xié)議開(kāi)銷(xiāo)決定,而協(xié)議的實(shí)際傳輸速率還受設(shè)備本身性能的影響。本測(cè)試中, PCIe 2.0 DMA讀操作數(shù)據(jù)傳輸速率速率高于SRIO 2.0 NREAD的主要原因是服務(wù)器對(duì)FPGA的PCIe讀請(qǐng)求的響應(yīng)要快于DSP對(duì)FPGA的SRIO讀請(qǐng)求響應(yīng)。

(5)設(shè)備尋址

PCIe協(xié)議中,各設(shè)備共享一個(gè)PCIe地址空間。整個(gè)PCIe地址空間先被分成塊,根據(jù)后來(lái)的下級(jí)總線(xiàn)這些塊再進(jìn)一步劃分。樹(shù)形結(jié)構(gòu)中的每個(gè)設(shè)備在整個(gè)地址空間映射中被指定一個(gè)地址空間,通過(guò)執(zhí)行全部地址譯碼來(lái)查找設(shè)備。在支持帶有大容量存儲(chǔ)器的設(shè)備系統(tǒng)中,這種設(shè)備尋址機(jī)制不適合靈活拓展。

SRIO采用基于設(shè)備ID尋址的方案[8]。采用該方案,使得拓?fù)浣Y(jié)構(gòu)的變化僅需要更新事務(wù)路徑中的設(shè)備,從而使系統(tǒng)的拓展與拓?fù)浣Y(jié)構(gòu)的更改比PCIe協(xié)議更為靈活。

Aurora 8B/10B協(xié)議未定義設(shè)備尋址機(jī)制。

(6)網(wǎng)絡(luò)拓?fù)?br /> PCIe規(guī)定了生成樹(shù)拓?fù)浣Y(jié)構(gòu),這種結(jié)構(gòu)適合于單個(gè)主機(jī),多個(gè)外圍設(shè)備通信模式,但限制了端點(diǎn)數(shù)量,且不支持任意節(jié)點(diǎn)與節(jié)點(diǎn)間直接通信。PCIe的典型網(wǎng)絡(luò)拓?fù)浣Y(jié)構(gòu)如圖15所示[9]。

?

圖15 PCIe網(wǎng)絡(luò)拓?fù)浣Y(jié)構(gòu)

SRIO的拓?fù)浣Y(jié)構(gòu)比PCIe更為靈活,可設(shè)計(jì)成網(wǎng)型,星型,雛菊鏈或樹(shù)形拓?fù)浣Y(jié)構(gòu),支持節(jié)點(diǎn)對(duì)節(jié)點(diǎn)通信,各節(jié)點(diǎn)間可對(duì)等的發(fā)起數(shù)據(jù)傳輸。

Aurora 8B/10B協(xié)議不支持網(wǎng)絡(luò)拓?fù)浣Y(jié)構(gòu)。

(7)應(yīng)用領(lǐng)域

Aurora 8B/10B協(xié)議作為Xilinx公司開(kāi)發(fā)的輕量級(jí)鏈路層協(xié)議,協(xié)議開(kāi)銷(xiāo)小,鏈路數(shù)目和鏈路線(xiàn)速率選擇靈活,適用于兩片Xilinx FPGA之間的數(shù)據(jù)流傳輸。用戶(hù)也可在其基礎(chǔ)上開(kāi)發(fā)高層協(xié)議。但其應(yīng)用范圍較為有限,尚未見(jiàn)在其他芯片中使用。

PCIe 2.0作為PCI總線(xiàn)的繼承,帶寬,拓展靈活性大大提高,適合于主機(jī)與外部設(shè)備的互聯(lián),在PC/Server平臺(tái)、VPX平臺(tái)有廣泛應(yīng)用,如聲卡、顯示卡、網(wǎng)絡(luò)設(shè)備(包括以太網(wǎng)、Modem)、光纖接口卡、磁盤(pán)陣列卡等。

SRIO 2.0作為一種高性能包交換的互連技術(shù),數(shù)據(jù)傳輸方式和拓?fù)浣Y(jié)構(gòu)靈活,為多處理器系統(tǒng)的實(shí)現(xiàn)提供便利,廣泛用于嵌入式系統(tǒng)內(nèi)的微處理器、DSP、通信和網(wǎng)絡(luò)處理器、系統(tǒng)存儲(chǔ)器之間的高速數(shù)據(jù)傳輸。

7 結(jié)束語(yǔ)

本文基于Virtex-6 FPGA芯片,對(duì)Aurora 8B/10B,PCIe2.0,SRIO 2.0三種串行通信協(xié)議進(jìn)行了速率測(cè)試,并通過(guò)分析協(xié)議開(kāi)銷(xiāo)和協(xié)議的流控制機(jī)制,計(jì)算了三種協(xié)議的理論傳輸速率和協(xié)議實(shí)際通信效率。結(jié)合測(cè)試結(jié)果和三種協(xié)議的具體內(nèi)容,對(duì)三種協(xié)議的相關(guān)參數(shù)和應(yīng)用領(lǐng)域進(jìn)行了對(duì)比分析。本文測(cè)試模塊結(jié)構(gòu)的設(shè)計(jì)可為三種協(xié)議的工程實(shí)現(xiàn)提供借鑒,協(xié)議實(shí)際傳輸速率的測(cè)算和協(xié)議理論傳輸速率的分析計(jì)算可為三種協(xié)議在不同平臺(tái)和工作模式下的測(cè)試提供參考。在進(jìn)行雷達(dá)信號(hào)處理機(jī)數(shù)據(jù)傳輸方案的設(shè)計(jì)時(shí),可參照本文對(duì)三種協(xié)議的性能分析,根據(jù)系統(tǒng)自身的特點(diǎn)及對(duì)數(shù)據(jù)傳輸速率的要求,合理選擇協(xié)議類(lèi)型和協(xié)議的工作模式。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論