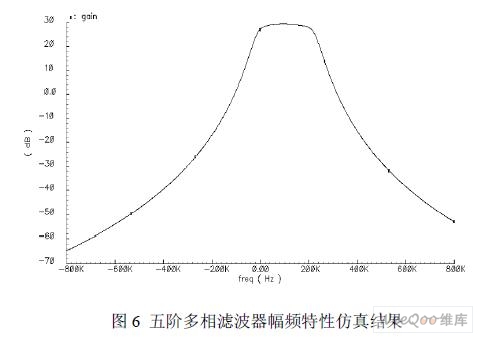

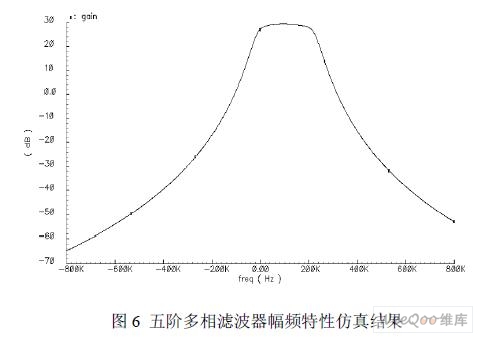

本文介紹了基于FPGA、以并行多相濾波結構為算法基礎的超寬帶數字下變頻技術。設計過程包括高速AD信號降速預處理,應用SysGen開發環境完成的數字混頻、多相濾波和數據抽取,并通過仿真驗證了算法

2014-02-22 10:23:41 3144

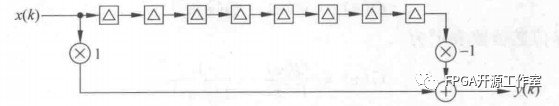

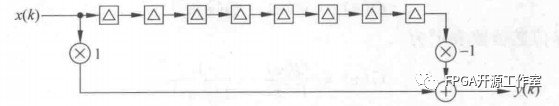

3144 sample rate convert 和 down sample rate convert 的FPGA實現打下基礎。 1 梳狀濾波器 圖1 梳狀濾波器結構 梳狀濾波器的兩端為1和-1的權值,具有簡單

2020-11-21 09:57:00 5220

5220

本帖最后由 eehome 于 2013-1-5 10:03 編輯

fpga實現濾波器在利用FPGA實現數字信號處理方面,分布式算法發揮著關鍵作用,與傳統的乘加結構相比,具有并行處理的高效性特點

2012-08-11 18:27:41

fpga實現濾波器fpga實現濾波器在利用FPGA實現數字信號處理方面,分布式算法發揮著關鍵作用,與傳統的乘加結構相比,具有并行處理的高效性特點。本文研究了一種16階FIR濾波器的FPGA設計方法

2012-08-12 11:50:16

進行的配置:1、當用命令濾波來使芯片進入TX狀態時,進入是否成功取決于CCA MODE的配置,CCAMODE指示了那種情況可認為是信道空閑:CCAMODE 信道空閑的標準00 總是空閑的01 接受

2016-04-12 14:21:38

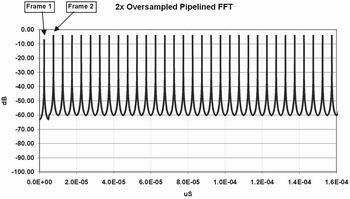

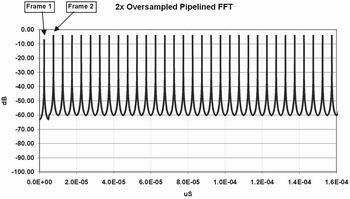

本文將對FFT和多相位DFT濾波器組進行比較,包括穩定狀態和瞬時條件的情況。同時也簡要地分析了過抽樣和所謂的“最小相位”濾波器的內容。

2021-04-12 07:01:58

實現各種數字信號處理算法的工程方法。本書將理論與實踐相結合,給出了相應算法的硬件結構,并配有時序圖,以幫助讀者深入理解設計思路。第1章 現場可編程邏輯門陣列(FPGA)技術現狀1.1 FPGA已進入

2012-04-24 09:33:23

的信號全概率接收的接收機,而基于多相結構的信道化接收機相對于傳統意義上的信道化接收機對同一頻段信號而言所需硬件資源更少,且更易于實現。其相對傳統的信道化接收機憑借其高效的多相結構,使其在多信道處理方面得到了廣泛應用,是接收機的發展趨勢。

2019-09-30 08:05:43

)、離散余弦變換(DCT)、小波變換、數字濾波器(有限脈沖響應(FIR)、無限脈沖響應(IIR)和自適應濾波器)以及數字上下變頻器。這些算法中,每一種都有一些結構性的元件可以用并行方法實現。而FPGA

2021-12-15 06:30:00

基于多相濾波結構的雷達信號檢測技術

2012-08-20 13:00:33

【作者】:袁江南;湯碧玉;陳輝煌;【來源】:《廈門大學學報(自然科學版)》2010年02期【摘要】:給出了一種自適應濾波器的設計和FPGA的實現方法.簡要分析了最小均方誤差(LMS)、歸一化最小均方

2010-04-24 09:01:12

CIC(Cascade IntegratorComb)濾波器最早由Hogenauer提出,后來出現了很多改進的結構形式。隨著芯片技術的快速發展、多相濾波技術的廣泛應用以及無線通信市場的迅速

2019-09-23 07:22:30

器的響應越好。然而這里有折衷的情況,由于大量的抽頭增加了對邏輯的需求、增加了計算的復雜性,增加了功耗,以及可能引起飽和/溢出。多相技術可以用于實現濾波器,擁有與傳統FIR濾波器可比的結果,而且使用了較少

2019-07-08 08:01:03

處理器(FPGA,DSP)是一個“瓶頸”;基于多相濾波的信道化接收機抽取在濾波之前,運算量小,且輸出速率低,便于FPGA實現,這使得在一片FPGA中實現數字信道化成為可能。

2019-08-22 08:01:34

使用了較少的邏輯、需要較少的計算資源、更低的功耗,并減少了可能的飽和/溢出。可怎么辦,才能用中檔FPGA實現多相濾波器?

2019-08-06 07:12:39

如何用中檔FPGA實現多相濾波器?

2021-04-29 06:30:57

本文首先介紹了FIR濾波器和脈動陣列的原理,然后設計了脈動陣列結構的FIR濾波器,畫出電路的結構框圖,并進行了時序分析,最后在FPGA上進行驗證。結果表明,脈動陣列的模塊化和高度流水線的結構使FIR

2021-04-20 07:23:59

),濾波器的響應越好。然而這里有折衷的情況,由于大量的抽頭增加了對邏輯的需求、增加了計算的復雜性,增加了功耗,以及可能引起飽和/溢出。多相技術可以用于實現濾波器,擁有與傳統FIR濾波器可比的結果,而且

2019-10-22 06:55:44

倍數關系。那我們該如何設計寬帶數字接收機的信道化?如何解決延遲與抽取的問題?并完成整個復多相濾波器的FPGA設計呢?

2019-08-07 08:01:57

,有可能丟失信號。而改進后的無盲區多相濾波器的信道數與抽取倍數不再相等。一般的旋轉開關方法實現延遲和抽取只適用于信道數與抽取倍數相等的情況,而無法適應改進后的算法。但是,信道數和抽取因子之間往往存在倍數關系。那么我們該如何設計寬帶數字接收機的信道化?完成整個復多相濾波器的FPGA設計呢?

2019-08-06 06:26:05

本文介紹了一種采用級聯結構在FPGA上實現IIR數字濾波器的方法。

2021-04-15 06:16:32

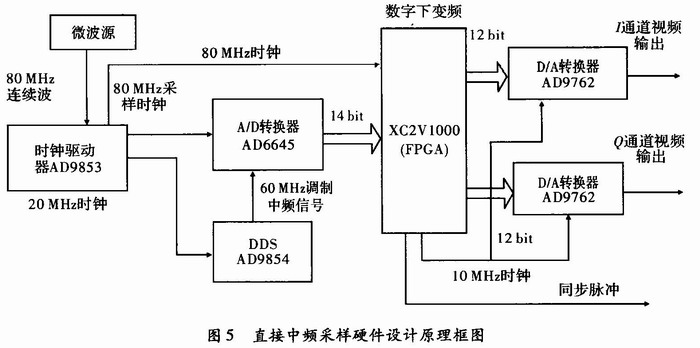

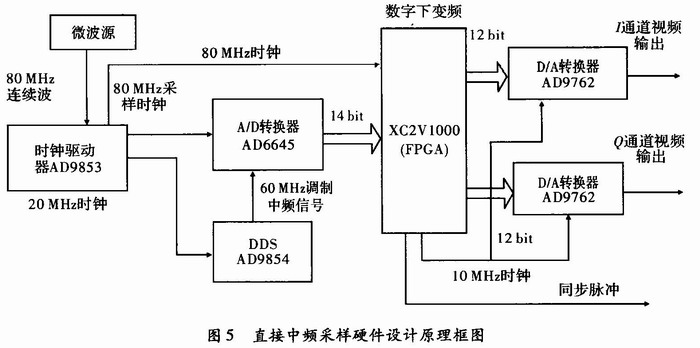

( DDC) 技術。所以數字下變頻技術在寬帶短波信道模擬器的數字化和軟件化過程中起到了重要的作用。FPGA 具有較高的處理速度和很強的穩定性,而且設計靈活、易于修改和維護,同時可以根據不同的系統要求,采用不同的結構來完成相應的功能,大大提高系統的適用性及可擴展性。因此,FPGA 逐漸成為實現DDC 的首選。

2019-07-22 06:27:47

并行流水結構FIR的原理是什么基于并行流水線結構的可重配FIR濾波器的FPGA實現

2021-04-29 06:30:54

怎么實現基于FPGA的無線信道模擬器的設計?

2021-05-25 06:09:47

本文提出的一種數字信道化IFM接收機方案結合了數字信道化接收機高效結構和相位差分瞬時測頻方法,從而降低了系統復雜度,提高了實時處理能力,仿真結果表明該方案具有較好的信號檢測能力。用現代技術來實現寬帶

2021-02-23 07:05:58

老板出了個這樣的題,但是單速率數字信道化,沒找到什么相關的資料,于是就求到論壇了,請各位大神指點明路,謝謝大家了哇~

2014-03-04 20:33:48

, 這就要求信道選擇濾波器能夠克服臨道比本道高40 dB的干擾, 于是在設計的時候要求信道選擇濾波器在兩倍頻處有大于45 dB的抑制。 根據UHF RFID接收機結構的特點, 在多讀寫器環境中, 接收機將

2019-05-29 07:46:53

AD9361支持的信道帶寬是是200KHZ-56MHZ,但是對于有些應用,信道間距可能只有20-50KHZ,對于這樣的信號這種濾波器無法實現對一個信道內信號進行濾波了。那這個芯片是不是支持這樣信道

2018-10-09 17:39:16

數字信道化原理是什么?怎樣去設計一種寬帶信道化接收機?如何對寬帶信道化接收機進行仿真?

2021-05-31 06:50:55

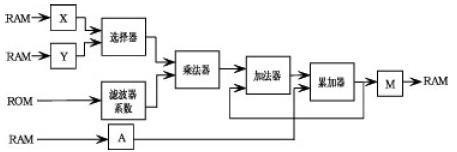

,得到相應階數的濾波器系數,量化并進行16進制轉換供FPGA使用。 前面說了,多相結構的FIR濾波器是在算法上下功夫,所以本身濾波器的設計過程就是普通濾波器的設計過程,并沒有什么不同,下面再來看多相

2015-08-29 15:37:11

手機電視/移動多媒體廣播 廣播信道幀結構、信道編碼和調制、無線射頻特性

本標準是手機電視/移動多媒體廣播系列標準之一,該系列標準的名稱及結構如下:1) 手

2008-07-22 14:48:36 29

29 移動多媒體廣播 第1 部分:廣播信道幀結構、信道編碼和調制Mobile Multimedia Broadcasting Part 1: Framing Structure, Channel

2008-10-21 15:59:48 7

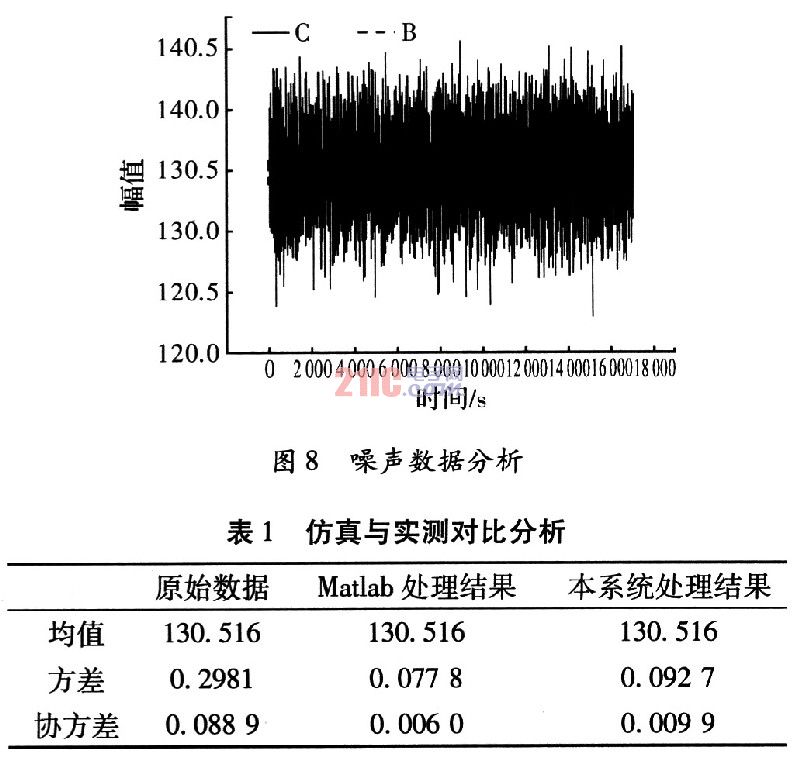

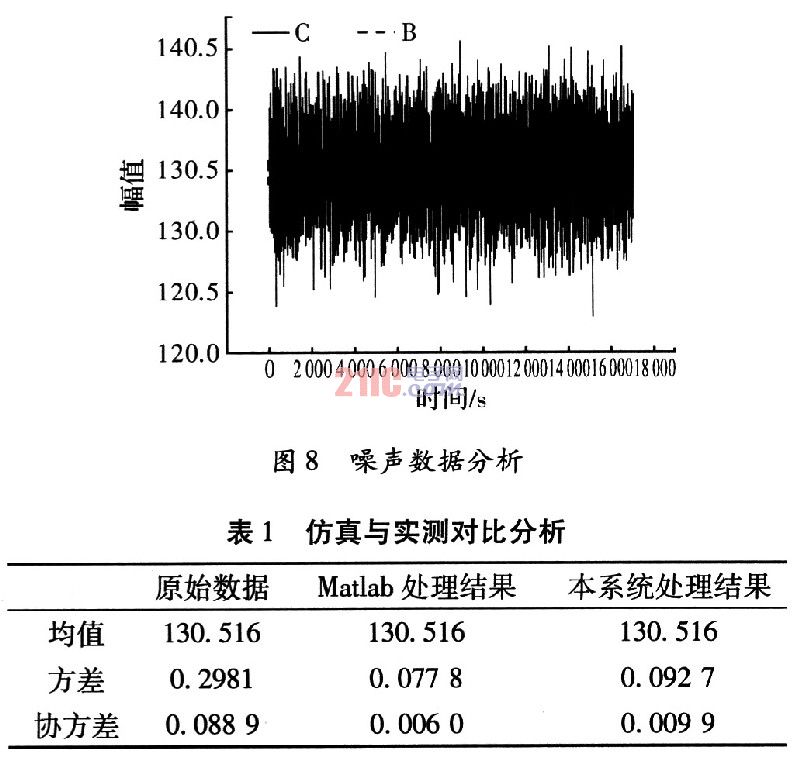

7 提出了一種多相濾波的寬帶數字化接收機的設計技術;討論了多相濾波的基本原理、設計及現場可編程門陣列實現,給出了多相濾波的中頻數字化接收機的實現方案。計算機仿真

2009-02-21 11:46:21 22

22 本文以cdma的兩個主要技術——碼分技術和多址技術為基礎,圖文并茂的介紹了cdma(IS95和20001x)技術體制的信道編碼和信道結構。信道編碼技術包括沃爾什碼(WalshCode)、長短PN碼(偽

2009-06-10 15:30:48 40

40 本文以cdma的兩個主要技術——碼分技術和多址技術為基礎,圖文并茂的介紹了cdma(IS95和20001x)技術體制的信道編碼和信道結構。信道編碼技術包括沃爾什碼(WalshCode)、長短PN碼(偽

2009-06-17 18:10:22 20

20 基于FPGA對稱型FIR濾波器的設計與實現:在基于FPGA的對稱型FIR數字濾波器設計中,為了提高速度和運行效率,提出了使用線性I相位結構和加法樹乘法器的方法,并利用Altera公I司的FPG

2009-09-25 15:38:38 30

30 基于漸消Ka lman濾波的M IMO2OFDM信道估計:針對快時變信道明顯的頻率選擇性,提出了采用Kalman漸消記憶濾波的估計方法.信道采用AR模型建模,并利用LS算法估計時變信道的衰減因子. 仿真

2009-10-25 12:14:32 7

7 在OFDM 系統中,信道的快速時變性破壞了子載波間的正交性,從而導致子載波間干擾(ICI),降低了系統性能。該文針對雙選擇信道的時變特性,提出了一種新的Kalman 濾波信道估計算法

2009-11-17 14:11:41 8

8 多相濾波器組信道化接收機的FPGA 仿真實現趙偉 王靜 李偉偉(大連海事大學 信息工程學院 遼寧 大連 116026)摘要:軟件無線電理論中的信道化接收機理論在多信號同時提取

2009-12-15 15:04:51 33

33 本文詳細討論了利用新版本FPGA 輔助設計軟件QuartusII6.0 中提供的浮點運算功能模塊實現IIR 濾波器的方法,與采用FPGA 的乘法模塊的同類設計相比,此濾波器設計結構簡單,容易擴

2009-12-19 15:44:27 38

38 基于多相濾波結構的分級濾波處理軟件無線電下變頻能夠解決以前存在的瓶頸問題,進行實時有效處理,算法的改進能更快速的執行二次采樣過程并進一步減少硬件資源的損耗,濾

2010-01-20 14:31:19 22

22 用于標清視頻信道的有源濾波器設計技巧關鍵詞:濾波器 模擬 數字信號摘要:當今的高速運算放大器使得在視頻應用中,采用有源濾波器來設計比采用無源電感電容(LC)濾

2010-02-06 10:34:07 16

16 如何設計用于標清視頻信道的有源濾波器作者:Steven O Smith關鍵詞:運算放大器,濾波器,PCB摘要:本文中的設計采用飛兆半導體的高速雙運算放大器(FHP3230),來構造一個可

2010-02-06 10:43:30 22

22 針對傳統數字正交變換存在A/D采樣速率要求比較高導致后續的數字低通濾波成為瓶頸、運算數據量大、需要正交本振等方面的不足,提出了一種基于軟件無線電多相濾波的數字正交

2010-07-10 15:55:28 12

12 設計一個由現場可編程門陣列(FPGA)控制的濾波器。該濾波器主要由3個模塊組成:前置放大、濾波電路、FPGA顯示與控制電路等利用FPGA作為放大器及程控濾波器電路中繼電器組的控制模

2010-07-17 18:00:09 45

45 針對寬帶陣列偵收系統,設計一種基于FPGA的信道化接收機實現方案,并對各模塊具體的實現進行了分析、設計,特別是基于FPGA的信道化模塊。整個系統具有子信道頻帶窄、利于對信

2010-07-21 15:59:59 18

18 為了解決電子偵察接收機中同時到達信號的接收問題,從傳統的低通濾波器結構出發,給出了一種無盲區高效數字信道化接收模型。信道化之后進行瞬時幅度和相位差提取。通過系

2010-11-17 11:43:44 25

25 摘要:本文簡要地論述了FFT和多相位DFT濾波器組在響應方面的差異。一般而言,多相位DFT(甚至包括任何濾波器組,比如PFT)在穩態條件下有著很好的相鄰信道抑制性能,而瞬態響應卻很糟糕。這符合了濾波器沖激響應結論。

2006-03-11 13:17:03 2056

2056

IIR數字濾波器設計-在FPGA上實現任意階IIR數字濾波器

摘 要:本文介紹了一種采用級聯結構在FPGA上實現任意階IIR數字濾波器的方法。此

2008-01-16 09:45:39 2276

2276

基于FPGA的二次群分接器的結構分析及實現

1.引言

為了提高傳輸速率,擴大通信容量,減少信道數量,通常把多路信號復用成一路信號進行傳輸。在多種復

2009-12-08 09:54:42 653

653 基于GSM 接收機的集成多相濾波器設計

摘要:本文介紹了用于GSM接收機的低中頻多相濾波器的設計,采用有源RC電路架構且單片全集成。設計采用TSMC 0.18um CMOS工藝,

2010-01-08 11:08:24 1945

1945

基于FPGA的星地信道模擬系統的研究與設計

1 引 言

衛星移動通信系統所能提供的業務的可行性與質量在很大程度上受到衛星與移動終端

2010-03-10 11:49:28 546

546

FPGA的Kalman濾波器的設計

摘要:針對電路設計中經常碰到數據的噪聲干擾現象,提出了一種Kalman濾波的FPGA實現方法。該方法采用了TI公司的高精度模數轉換

2010-04-13 13:32:46 2566

2566

DNLMS濾波器的FPGA設計方案

自適應濾波算法的研究始于20世紀50年代末,Widrow和Hoff等人最早提出最小均方算法(LMS)。算法由于結構簡單,計算量小,易于實

2010-05-10 10:06:23 622

622

介紹一種利用帶通采樣定理及多相濾波的方式實現數字相干檢波的方法,由于采用數字信號處理的方式獲取I、Q基帶信號

2010-11-09 09:53:22 1301

1301

本文設計的信道選擇濾波器用于UHF RFID閱讀器接收機模擬基帶部分, 接收機采用I/Q 兩支路正交的零中頻結構, 圖1是接收機模擬基帶結構圖。

2011-02-23 09:47:16 1880

1880

本文介紹了一種有理數采樣率變換器的高效多相結構,并結合FPGA芯片的結構進行了實現與優化。文中的一些方法也適用于其他多采速率系統的設計。

2011-03-02 10:04:34 2161

2161

為解決現代電子戰對接收機處理帶寬寬、靈敏度高及實時性處理的要求,提出一種數字信道化接收機的設計方法。在推導高效信道化接收機模型的基礎上,采用多相濾波器結構實現的數字信道化接收機。該接收機利用超高速A/D對數據進行高速采樣,然后由高性能FPGA進行

2011-03-07 15:28:33 61

61 本文介紹用RC多相濾波器實現鏡像抑制的原理,推導出電阻電容誤差對鏡像抑制影響的數學表達式,通過仿真驗證表明,計算值與仿真值較為接近,并應用RC 多相濾波器來實現高鏡像抑

2011-08-23 14:51:14 46

46 基于多速率信號處理原理,設計了用于下變頻的CIC抽取濾波器,由于CIC濾波器結構只用到加法器和延遲器,沒有乘法器,很適合用FPGA來實現,所以本文分析了CIC濾波器的原理,性能及影

2011-08-26 15:12:11 160

160 無線信道仿真和均衡器的FPGA設計與實現

2011-10-09 18:11:37 40

40 針對軌道電路信號(FSK信號)的檢測提出了基于多相濾波器組的頻譜細化(ZFFT)分析方法,該方法利用多相濾波器組將待分析的移頻信號按照不同載頻分解成多個子帶,經過子帶選擇,再進

2011-10-10 15:09:01 37

37 多相DFT濾波器組是實現信道化接收機的一種高效結構,但是該結構要求信道數目與抽取倍數必須相等,限制了接收機參數設計的靈活性。該文將WOLA濾波器組引入信道化接收機,以信號的

2011-11-08 18:00:39 27

27 基于多相濾波的信道化接收機抽取在濾波之前,運算量小,且輸出速率低,便于FPGA實現,這使得在 一片FPGA中實現數字信道化成為可能。本文利用信道頻率重疊的方法連續覆蓋整個瞬時

2012-05-23 10:43:04 3538

3538 信道化接收技術是解決寬帶信號檢測等問題的一種有效方式。信道化接收機因其具備較大的瞬時帶寬、能夠檢測和處理同時到達的信號、具有準確的參數測量能力和一定的信號識別能力

2012-08-18 11:35:49 2186

2186

描述了基于FPGA的FIR濾波器設計。根據FIR的原理及嚴格線性相位濾波器具有偶對稱的性質給出了FIR濾波器的4種結構,即直接乘加結構、乘法器復用結構、乘累加結構、DA算法。在本文中給

2012-11-09 17:32:37 121

121 研究了一種采用FPGA實現32階FIR濾波器硬件電路方案;討論了窗函數的選擇、濾波器的結構以及系數量化問題;研究了FIR濾波器的FPGA實現,各模塊的設計以及如何優化硬件資源,提高運行

2017-11-10 16:41:57 15

15 為了減少信道化接收機的資源消耗,對低通濾波器組實現信道化接收機的結構進行了研究。在前人將HB濾波器和FIR濾波器設計為多通道并采用時分復用方法的基礎上,將NCO和CIC濾波器也做了同樣處理,并在

2017-11-17 05:38:02 3382

3382

,其頻率截獲概率與分辨力的矛盾難以解決,無法實現全概率信號截獲。而多信道化的頻率檢測技術屬于瞬時測頻,其架構是采用多個頻率窗口(多個信道彼此銜接相鄰)來覆蓋接收機的整個頻段.

2017-11-18 10:51:17 5139

5139

對一種單圖像向導濾波器的高性能FPGA設計結構進行了分析,發現其中的均值濾波器存在設計缺陷,據此提出了一種向導濾波器的整數FPGA設計結構。通過改變均值濾波器的數據累加順序,減少了存儲資源

2017-11-22 15:43:12 12

12 ,有可能丟失信號,而改進后的無盲區多相濾波器的信道數與抽取倍數不再相等,信道數和抽取因子之間往往存在倍數關系。

2017-12-09 17:29:40 4221

4221

用FPGA實現抽取濾波器比較復雜,主要是因為在FPGA中缺乏實現乘法運算的有效結構,現在,FPGA中集成了硬件乘法器,使FPGA在數字信號處理方面有了長足的進步。本文介紹了一種采用Xilinx公司的XC2V1000實現FIR抽取濾波器的設計方法。

2018-04-28 11:50:00 1073

1073

的自適應調整是通過控制算法對信道中的信號進行快速檢測,然后將結果和濾波器的輸出結果進行差值計算進行反饋調節。利用Quartus II和DSP Builder設計基于FPGA的16階系數可調FIR濾波

2018-07-23 17:21:00 2372

2372

用FPGA實現抽取濾波器比較復雜,主要是因為在FPGA中缺乏實現乘法運算的有效結構,現在,FPGA中集成了硬件乘法器,使FPGA在數字信號處理方面有了長足的進步。本文介紹了一種采用Xilinx公司的XC2V1000實現FIR抽取濾波器的設計方法。

2020-09-25 10:44:00 3

3 針對Σ△ADC輸出端存在的高頻噪聲問題,設計了一種 Sinc數字抽取濾波器,實現了Σ-△調制器輸出信號的高頻濾波。分析了Sinc濾波器的結構原理,基于 Spartan6FPGA進行濾波器的設計與實現

2020-08-26 17:12:00 14

14 WCDMA中規定了小區搜索的時隙同步過程采用匹配濾波器的方法實現,本論文主要研究匹配濾波器原理及FPGA實現結構。

2021-01-26 16:22:43 12

12 提出了一種基于多相濾波器的并行有限脈沖響應(finite impulse response,FIR)濾波器結構,可以有效提高濾波器運算的吞吐率,與傳統的串行濾波器結構比,并行濾波器運算速度可以提高

2021-01-28 17:22:00 15

15 提出了一種基于多相濾波器的并行有限脈沖響應(finite impulse response,FIR)濾波器結構,可以有效提高濾波器運算的吞吐率,與傳統的串行濾波器結構比,并行濾波器運算速度可以提高

2021-01-28 17:22:00 7

7 針對電子戰中的寬帶偵察數字信道化接收機,提出了基于短時傅里葉變換的寬帶數字信道化接收機的改進方法,給出了該方法的FPGA實現。該方法采用多相濾波結構,通過先對時域抽取信號進行傅里葉變換,再對變換結果

2021-02-05 17:35:51 27

27 針對高速率QPSK數據傳輸鏈系統,比較分析了數字中頻接收與零中頻接收的優、缺點,并提出了一種基于多相濾波的寬帶中頻正交采樣數字零中頻接收方案。基于FPGA對此數字零中頻正交變換方案進行了實現和驗證,同時,對一種全數字零中頻QPSK信號的高速解調算法及其FPGA硬件實現進行了介紹。

2021-03-19 17:43:12 11

11 提出一種新的高階FIR濾波器的FPGA實現方法。該方法運用多相分解結構對高階FIR濾波器進行降階處理,采用改進的分布式算法來實現降階后的FIR濾波器。設計了一系列階數從8到1 024的FIR濾波

2021-03-23 15:44:54 30

30 :針對高速率 QPSK 數據傳輸鏈系統,比較分析了數字中頻接收與零中頻接收的優、缺點,并提出了一種基

于多相濾波的寬帶中頻正交采樣數字零中頻接收方案。基于 FPGA 對此數字零中頻正交變換方案

2022-12-12 15:44:36 3

3

電子發燒友App

電子發燒友App

評論