過去三十多年來,FPGA 技術已從最初帶有少量寄存器的可編程邏輯陣列演變為如今我們所看到的高級集成式系統器件。大約在十多年前,各大廠商首次開始在他們的FPGA器件中采用8位、16位和32位的軟核處理器,以提高處理與可編程邏輯之間的集成度與功能性。隨后他們開始實現這些處理器的硬化版本(hardened version),為客戶帶來了更多系統優勢。賽靈思的Zynq?-7000 All Programmable SoC就是此類器件中的佼佼者。

Zynq SoC在單個器件中集成ARM?雙核Cortex?-A9 MPCore處理系統、FPGA架構和外設,這樣軟/硬件實現了前所未有的緊密連接,從而將系統級集成和功能提升到了全新的高度。但是這種更加緊密的集成也模糊了軟硬件設計之間的界限,因為它將FPGA設計引入到了軟件領域,同時又將應用軟件開發引入到了FPGA領域。

我們TOPIC Embedded Systems公司開發的IP模塊能顯著縮減在Zynq SoC上進行系統開發所需的時間和成本。Dyplo系統的中間件能有效彌補軟硬件設計之間的缺口,有助于實現一套完整的基于軟件的開發流程。Dyplo 具有自動部分重配置功能。這是一種高級設計技術,可即時修改FPGA布局的硬件配置,讓 FPGA 針對特定應用發揮出最佳性能。用戶可利用圖形化工具將功能拖到各個分區,然后判斷它們是否在邏輯或處理器上達到最佳運行效果。

DYPLO:動態流程載入程序

Dyplo 是一種中間件IP模塊。該模塊通過標準 AXI 接口可連接各個FPGA流程與處理器執行的軟件流程之間的可擴展數據流。

從開發角度可以最好地闡述Dyplo的原理。當啟動一個設計項目時,首先必須確定設計要求,將客戶需求定義為抽象條款)。在此階段,修改設計要求相對來說不會造成太大影響。下一步您需要將設計要求轉化為設計規范,此時要制定一個架構實現藍圖。在此架構制定過程中,您需要確定哪些功能應在硬件中實現哪些在軟件中實現,并設定時間目標。在很多情況下會有多種架構可供選擇,但由于預算和時間方面的制約,通常只能對一種架構方案進行研究(如果您運氣好的話,可以是兩個)。在這個階段修改設計要求會帶來較大的成本損失。

完成架構定義后,就要開始設計各種功能。在設計環節您通常會發現一些疏漏,即需要在軟硬件之間互換實現內容。這種互換通常會增加開發工作量,因為您要開始解決DSP類型數據流程中的突破性控制功能等原本不屬于這些相關領域的問題。隨著客戶對設計復雜性理解的深入,他們的洞察力也在增強,因此這種情況就變得相當普遍。因此,設計人員需要一種有效的機制以便在硬件與軟件之間進行功能互換。

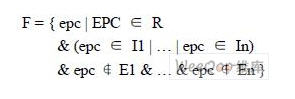

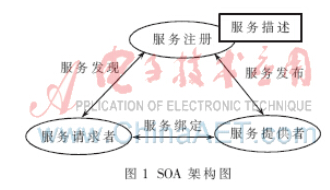

圖1所示的是一種把流程映射到FPGA硬件和軟件的常見任意調度情景。圖(a)未采用通用分配方案。因此,需要在軟件與硬件之間建立一種更加結構化和可預測的基礎結構。Dyplo實現了這種基礎結構,如圖(b)圖所示。

圖1 – (a)圖中有兩個獨立的流程,即硬件設計人員將HDL輸入Zynq SOC的邏輯模塊,軟件設計人員將軟件輸入處理器。與此不同的是,Dyplo為硬件和軟件功能創建了一個統一的代碼輸入點,如(b)圖所示,這樣便于在Linux環境下實現系統級協同設計與驗證。

Dyplo為用戶提供了用于連接硬件與軟件流程的數據流接口。既可以采取軟件流程之間的通信,也可以是硬件流程之間的通信,還可以是軟硬件流程混合通信。您可以利用Dyplo在可重配置分區內定義硬件流程。要實現給定的硬件功能,需要在某個可重配置分區上激活它,然后對通往該分區的輸入輸出數據流進行初始化,并將這些數據流連接到軟件流程或其他硬件流程。除了同步數據流外,還可以對幀邊界、離散樣本矩和軟件任務對齊等事件進行流程同步。

軟件流程的數量取決于設計所針對的操作系統以及流程通信的組織方式。硬件流程的數量則取決于FPGA上所保留的可重配置分區的數量。可重配置分區的數量、大小和位置可以由用戶定義,也可以自動選擇。

Dyplo通過具有可擴展性能的軟硬件通信背板來處理流程通信與同步。例如,默認配置下允許四個HDMI視頻流同時處于工作狀態,同時利用處理器保持完全的數據交換功能。

Dyplo基礎架構、映射到可重配置分區上的功能以及完整Linux分布的生成都通過兼容于標準Vivado? 設計套件項目流程的圖形工具流程來實現。

您可以在設計過程中即時停止執行軟件和硬件流程,在替換流程功能后繼續執行。對于軟件流程這并不重要,設計人員可以加強代碼(僅受到設計人員針對項目所選操作系統的功能限制)。對于硬件流程,需通過執行部分重配置來取代部分FPGA的功能,同時不會影響其他可編程邏輯或外部物理接口的執行。同時自動正確加載和驗證邏輯模塊。

這樣,Dyplo在軟件環境中融入硬件流程的執行,同時為軟件編程人員無縫提供FPGA的功能優勢。Zynq SoC能帶來硬件系統級集成度方面的諸多優勢。所有功能都能用于全軟件式可編程平臺。然而從應用角度出發,需要一個中間件才能獲得這種架構優勢。這就是Dyplo作用所在。

利用部分重配置的價值

Dyplo可充分利用FPGA的部分重配置功能。 部分重配置對于設計人員來說絕不是微不足道的工作,原因在于加載和管理部分比特流文件的復雜性高,而且需要在更改PFGA元件的時候保持設計的連續性。此外,物理元件的布局布線問題需要相當高的FPGA設計經驗。

Dyplo提供直接可用的集成式部分重配置支持。根據所需分區數量和可重配置分區的邏輯復雜性等配置參數來保留可重配置分區的默認區域。在提供可重配置模塊等HDL功能描述后, Dyplo 可自動生成部分比特文件。

作為軟件應用的一部分,可重配置模塊通過發出簡單的軟件指令來獲取功能。Dyplo負責完成執行硬件功能所需的所有步驟,例如終止當前正在執行的功能、編寫新的功能、數據流連接、模塊配置以及功能激活。

為硬件工程師帶來的好處

集成Dyplo架構能為FPGA設計工程師帶來哪些優勢?它可以實現與處理器環境的集成,同時將底層軟件的支持需求降到最低,從而使設計工作變得更輕松。這意味著您可以集中精力實現設計功能。FPGA的優勢在高速接口設計、高數據帶寬電路和加速算法處理這些應用中的作用尤為明顯。設計接口與高帶寬電路時需要手動參與,并要求對于FPGA器件的技術優勢有深刻理解。對于加速算法處理應用來說,系統級綜合工具(例如Vivado HLS)將扮演越來越重要的角色。然而,在使用高層次綜合時,需要具備一定設計經驗來確保實現效果。

有了Dyplo基礎架構,很容易嵌入算法處理模塊,這樣為算法處理模塊、I/O模塊和處理器執行功能之間通信搭建了一個高速可配置的流程間通信網絡。這些處理模塊經過精心架構,非常適用于部分重配置。模塊有明確的接口,例如符合AXI4接口標準的流數據接口,采用高速互聯結構和簡化的處理器總線,可直接連接處理系統。到其他FPGA邏輯或器件I/O的鏈路則通過專用的可擴展接口來實現。Dyplo的性能足以支持多個1080p輸入和輸出視頻流,而且只需簡單配置就可實現視頻流連接。

FPGA為軟件工程師帶來的優勢

設計團隊利用Dyplo可以顯著簡化HDL編碼工作,而在系統軟件設計方面也能獲得更多的優勢。Dyplo使設計團隊能夠在硬件實現過程中分離軟件功能,在軟件中完成原型設計,再將它們轉換到硬件中,并保持相同的接口行為。反過來,不同功能可在軟件控制下共享相同的FPGA架構。這種方案所需的器件更小,能降低FPGA成本,效果可與軟件線程相媲美。

從軟件系統的角度來看,可將單個流程與連接之間的相關性看作是具有數據與事件同步機制的流程網絡。圖2 給出了軟件和硬件流程與Dyplo基礎架構之間的關聯方式。

圖2 – 球形、 方塊和金字塔代表能夠在FPGA硬件或軟件中運行的功能或流程。各個流程都被密封在Dyplo蓋布(圖形四周的方框)中。箭頭代表從輸入端經不同流程流到輸出端的數據流。Dyplo界面負責管理整個流程。

這種方法還能帶來動態性能擴展,因為可根據系統執行環境實現相同功能的多個實例。這樣做的結果是使GPU加速流程的執行更靈活,而且具備更高性能。這種技術還可以讓FPGA更多地為軟件工程師所用,原因在于接口協議比較簡單而且可將復雜設計拆分為復雜程度可控的多個模塊。更為重要的是,由于接口兼容,使得Dyplo與Vivado HLS能實現完美匹配,這種方式非常適用于基于軟件的開發流程。

采用Dyplo后測試工作也更加簡單。將流向和來自HDL模塊的數據流存儲在HDL測試平臺用來生成模式的文件中。這意味著驗證過程中開發團隊可以集中對所需功能進行測試。

測試與調試環境

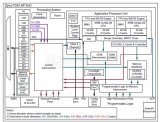

復雜的系統集成非常耗時,而且驗證工作的難度更大。我們開發了Dyplo基礎架構后,都知道設計的測試與集成工作占用了大部分開發時間,而且是開發流程中最枯燥的環節。在配置過程中,基本Dyplo 環境會生成驗證所用的測試平臺模板。例如,Dyplo環境為架構中的每個可重配置模塊生成一個功能測試平臺模板,實現文件或正規表達式的流輸入與輸出以及用以實現CPU接口的總線功能模型(見圖3)。這樣,設計人員就可以采用基于測試的設計方法。這種基礎架構允許設計團隊對設計方案采取單步調試以找出問題,并執行背板性能分析,以便實現結構中所有相關狀態信息的可視化。該理念非常靈活,以至于停止Dyplo基礎架構的HDL邏輯將會自動同步軟件執行。此功能是確定與解決接口和動態問題的關鍵。

圖3 – 采用功能測試模板實現數據流輸入與輸出,同時由總線功能模型實現CPU接口。

填補缺口

總部位于荷蘭的TOPIC Embedded Systems 公司多年來一直開發嵌入式系統,所涉及的項目通常集成有各種類型的FPGA和處理器。日積月累,我們已經成為高級FPGA設計技術(包括部分重配置)方面的專家。Zynq SoC作為一種采用嵌入式FPGA技術的多核平臺,可以顯著提高嵌入式系統設計效率。但很多設計團隊面前的挑戰是如何根據軟硬件工程設計人員的專業技術情況最充分發揮Zynq SoC豐富功能集的作用。

我們的Dyplo中間件可以填補這一缺口。可在FPGA架構上實現面向GPU設備的應用,所需的工作量相同,而且靈活性更高。充分利用重配置技術使得FPGA架構的重用從軟件應用角度來說變得非常簡單,而且有助于降低產品成本。在開發FPGA設計和軟件設計過程中自動執行很多底層設計、集成與測試任務,可以有效簡化設計流程。簡而言之,由Dyplo中間件系統所實現的生產力、靈活性和性能優化效果能幫助設計團隊將Zynq SoC的性能發揮到極致并且更快速地將創新系統設計推向市場。2013年12月1日將推出面向限定用戶的試用版(beta版)。如果您希望參與試用項目,請與我們聯系。商用版將于2014年3月1日推出。

電子發燒友App

電子發燒友App

評論