隨著無線數據傳輸量呈爆炸性成長,數字訊號處理技術和無線電設備在提升效能方面都面臨巨大的壓力。目前全球的重點都聚焦在4G LTE,而且在世界各地均有大規模部署,而業界也已展開5G網絡的早期研發工作,目標是要將5G網絡的數據傳輸量提升至4G網絡的千倍以上。這種新興的技術發展為系統商帶來不斷演進的的全新要求,其中包括提升系統整合度和系統效能、降低系統材料列表(BOM)成本、提高設計靈活度,以及加速產品上市時程等。

傳統ASIC組件支持的硬件解決方案雖然尚可符合功耗和成本目標,但其所需的一次性工程費用(NRE)極高、缺乏靈活性,讓產品的上市時程變得非常緩慢。為了因應市場的全新需求和克服以上種種挑戰,賽靈思推出All Programmable SoC (APSoC)架構,并成功建置在Zynq-7000產品系列中。Zynq-7000組件采用賽靈思APSoC架構,透過硬件、軟件和I/O可編程能力全面提升系統級的差異化、整合度和靈活性(如圖一)。

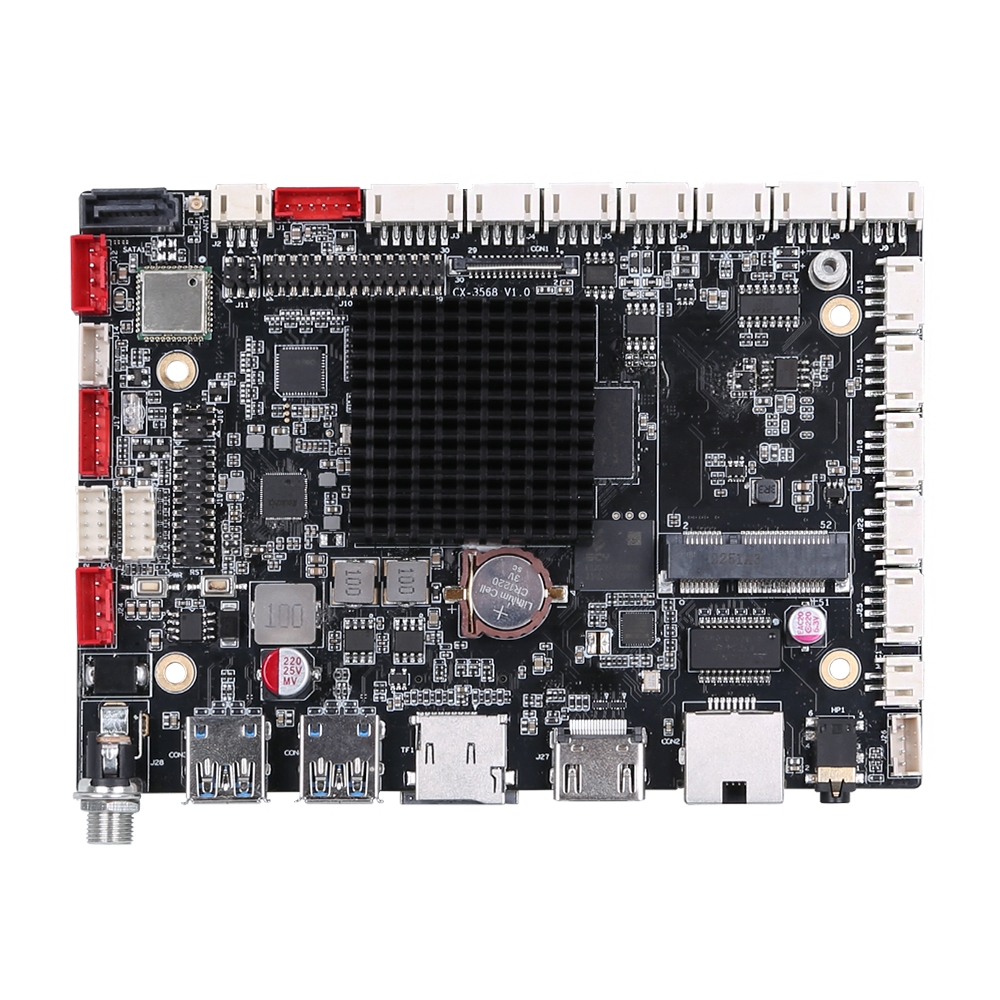

圖一 Zynq-7000 All Programmable SoC架構

賽靈思自2011年12月推出Zynq-7000組件以來,已廣泛應用于通訊、數據中心、汽車、工業、航天與國防等眾多領域。對通訊市場(尤其是無線應用領域)而言,Zynq-7000提供獨特的優勢:

其整合式可編程邏輯針對數字訊號處理提供高度優化;其采用的ARM Cortex A9處理子系統可有效建置典型無線設備(例如遠程無線電和無線回程單元)的控制功能。

在采用Zynq APSoC組件設計無線應用時,必須選擇能滿足應用需求的操作系統。而在針對不同的無線應用時,必須考慮以下幾個關鍵因素:

1. 電信級運作能力:電信級系統一般都要達到99.999%系統可靠度,也就是系統的正常運行時間要達到這么的水平。從系統運作的角度來看,這代表對系統各項特性的支持,例如冷/暖重開機、故障監測、偵測和處理,以及冗余,都要達到這程度。

2. 實時處理:實時不僅意味著速度要「非常快」,而且要有可預測的反應時間。相較于無線回程處理,遠程無線電有不同的實時處理要求。無線電設備訊號處理任務繁重,因此支持訊號處理的處理器必須能滿足嚴格的時序預算要求。

3. 診斷:為了支持現場診斷和事后診斷,需要收集和儲存大量效能衡量數據和日志數據,藉此可追蹤和管理無線應用的關鍵指標,例如效能衡量與統計數據、CPU使用率和故障監控、操作系統任務切換和事件歷史等指標。

4. 工具與協定整合:除錯與診斷環境全面整合,以及一些操作系統廠商提供的特定網絡協議堆棧,都有助于設計人員開發有效率的系統和維護高效的系統運作。

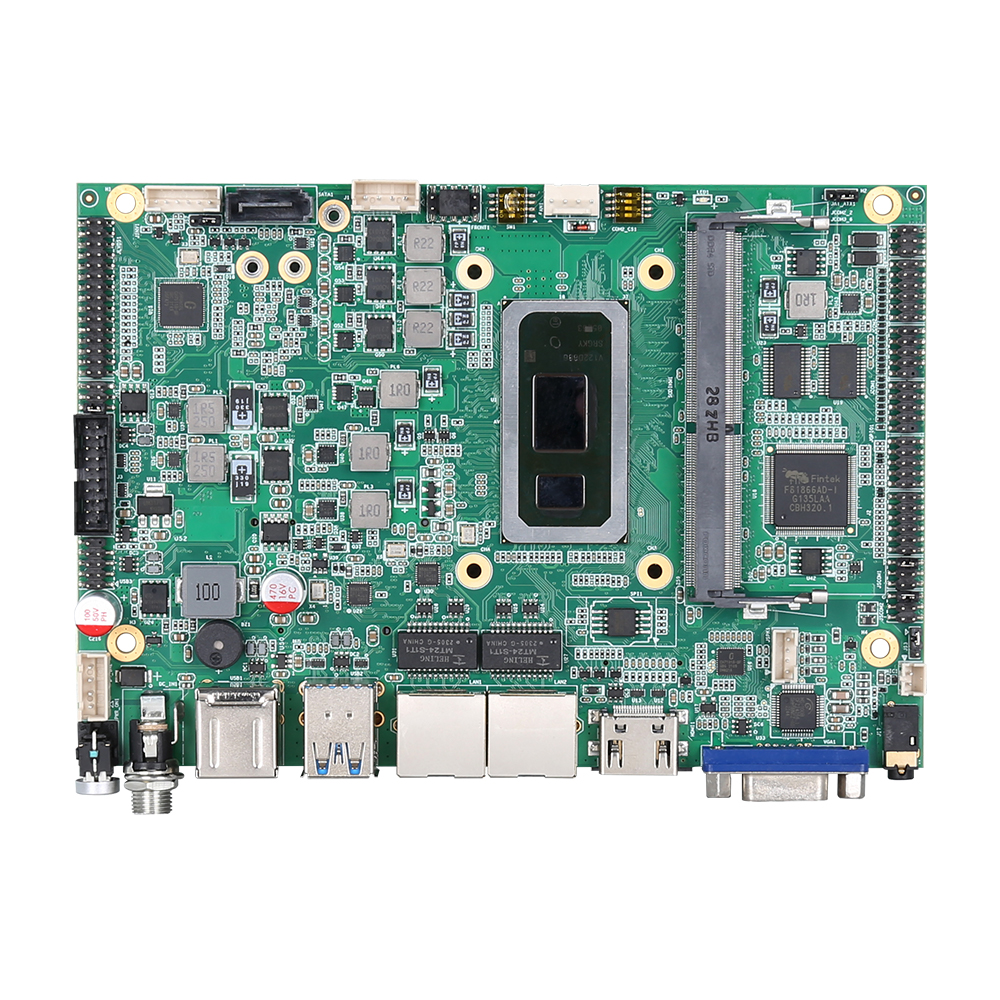

Zynq SoC整合了兩顆ARM Cortex A9核心。軟件設計師需要在可支持這款ARM核心的SMP(對稱多處理架構)或AMP(非對稱多處理架構)多處理器架構之間做出選擇。如圖二所示,在SMP系統架構中,兩顆以上完全相同的處理器共同在單一操作系統實例中共享資源。

?

圖二 SMP與AMP之比較

理論上,這種架構在同一個操作系統實例中會平等對待所有處理器。相反地,在有或沒有操作系統實例和處理器互相不知彼此存在的情況下,AMP架構會對個別處理器有不同的待遇,而沒有執行操作系統的核心則可能會執行一個被視為「裸機」實例的微程序代碼。

通常SMP為較高階的應用提供統一的操作系統平臺。軟件架構師在操作系統上建置應用時,無需考慮兩顆核心之間共享資源和跨行程的通訊問題。此外,SMP的效能消耗會對時間要求嚴格的無線應用造成影響。相較于SMP,AMP備有操作系統實例的輕量級軟件幾乎完全沒有消耗的問題,但需要精心客制的軟件設計來實現處理器資源共享和處理器之間的通訊。

使用Zynq APSoC組件可有效建置多種重要的無線應用,其中包括無線電和無線回程。每種無線應用有不同的效能要求,而且需要操作系統支持不同的特性。無線電應用就是一個很好的Zynq應用案例,因為透過Zynq可建置包括所有數字前端處理功能的完整軟硬件整合解決方案。

無線電數字前端應用是4G無線網絡中典型遠程無線電頭端設備(RRH)的主要部分。這種應用的處理要求可分為訊號處理和控制處理。在訊號處理領域,Zynq可用以建置于高采樣率濾波器,可達到數字升/降頻變頻、波峰因子抑制(CFR)和數位預失真(DPD)。然而,DPD是一個特例,需要同時使用Zynq的PS和PL。

DPD處理可細分為高速數據路徑和更新路徑。更新路徑用于定期更新濾波器組的系數,非常適合用于ARM Cortex A9核心。一般來說,系數更新必須在幾毫秒到幾十毫秒內完成。由于計算的算術復雜性,可使用A9核心和嵌入式NEON SIMD向量運算單元來因應所需的高效能。此外,Zynq PL也可為各種需要大量處理器頻率周期的功能提供硬件加速,因而Zynq PL、ARM A9核心和NEON協同處理器可進行協同作業。

無線電的控制處理一般用于初始的無線電校準、配置、警告、排程和從網絡終止訊息。這樣的作業一般在無線電應用中并不需要高效能,因此使用Zynq組件內建的單一ARM A9核心就能輕松管理。選擇合適的架構來支持DPD應用和控制處理應用是非常重要,因為合適的架構會決定整體效能、可靠度和維護的容易度。

AMP模式是無線電應用的通用架構。在此模式下,可透過裸機模式提供一顆完整的ARM核心進行DPD處理作業,因而可提供更多運算余量以滿足各種DPD系數更新所需的時間要求。而第二顆由操作系統控制的ARM A9核心則可執行控制和OAM等所有其應用。

在這種架構中,由于操作系統只能控制兩顆ARM核心中的其中一顆,因此必須在兩顆獨立的核心之間建立建立處理器之間的通道,例如使用OCM (On Chip Memory)或共享內存。這對某些重要的控制應用尤其重要,例如用于監控DPD模塊狀況的應用。這種行程間的通訊(IPC)解決方案并沒有標準可循,而是必須在AMP模式中單獨開發。

SMP架構非常簡單明確,就是使用單一操作系統實例同時控制兩顆ARM核心,進而控制所有應用。IPC、除錯、支持工具鏈都在相同的操作系統下運作。為了確保DPD應用有專屬的資源,可在軟件應用中使用「核心親和性」(Core Affinity) 和「中斷遮蔽」等特殊技術。在前面的案例中,DPD應用只在一個核心上執行,也就是除了操作系統排程器消耗外,DPD應用不會跟其他作業共享資源。而在后面的案例中,除了因DPD應用所需的執行作業外,各種中斷服務會直接轉由第二顆核心執行。如此一來, DPD應用可充分運用所有資源。

由此可見,Zynq APSoC是支持AMP或SMP架構的理想平臺。如圖三所示,Zynq整合兩顆ARM核心的處理器、12.5Gb/s序列器/解除序列器 (SerDes)、可靠度更高的500MHz+ DSP,并能提供完整的數字前端功能,諸如DPD、CFR、DUC/DDC和CPRI/JESD接口等。這個解決方案無需在處理器和獨立的FPGA組件之間設立接口,從而簡化PCB設計。

從獨立式多芯片解決方案轉移到Zynq平臺的單芯片整合方案是相當簡單明了的。賽靈思提供全面的軟硬件解決方案,其中更包括用于DUC、DDC、CFR和DPD的數字訊號處理IP庫,有助多芯片方案順利轉移到Zynq平臺。此外,賽靈思也提供對多種操作系統解決方案的支持,包含組件驅動程序、啟動加載程序、BSP范例和常用的工具。當設計方案成功轉移到Zynq平臺后,系統效能即可大幅提升,也可節省整體功耗,并降低材料清單(BOM) 成本。

圖三 從獨立式解決方案轉移到Zynq解決方案

以上,我們探討了為無線應用選擇操作系統的主要考慮因素、無線應用的建置架構和其中AMP與SMP比較的考慮因素,以及可直接運用賽靈思Zynq 7000組件的應用。總之,賽靈思提供的高階組件能讓基礎架構設備設計人員在實現軟硬件可編程性的同時,也可提升效能和系統整合度、降低材料清單 (BOM) 總成本與整體系統功耗,以及實現高可靠度和加速產品上市時程。設計人員現在不僅能加快開發設備,而且還能在設備部署完成后繼續可提供現場更新,排除了與ASSP和ASIC等組件相關的風險。

電子發燒友App

電子發燒友App

評論