隨著人們越來越注重安全問題,監控開始向小型化、家庭化發展。為了實現全方位多角度監控,需要采用多路攝像及多個顯示器來顯示實時信息,同時多路存儲的容量需求比較大。為了在容量有限的情況下存儲更多數據, 需要對多路視頻進行相關處理,將多路視頻合成一路視頻信號再進行壓縮存儲和顯示。

1 系統組成及工作原理

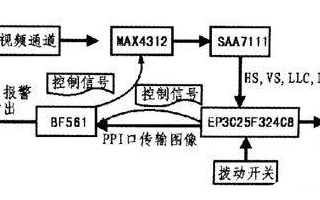

綜合考慮視頻圖像的實時性以及功耗體積等因素,采取以下方案:由4路并行的視頻模數轉換芯片TVP5154將4路視頻信號轉換成數字格式的視頻信號,并用FPGA進行合成處理[1],再送給ARM模塊進行進一步壓縮、存儲等處理。圖1為系統的FPGA部分的硬件結構圖。

采用Xilinx公司Spartan 3E系列中的XC3S500E芯片,該芯片具有功耗低、成本低等優點。采用TVP5154模數芯片主要是考慮到它是4路并行的,可節省板級空間,也方便控制,它可以將輸入的4通道NTSC/PAL/SECAM 格式的視頻數據轉換成4通道的8位ITU-R BT.656[2]格式的數字視頻輸出供FPGA進行處理。FPGA包含I2C[3]通信模塊、視頻采集模塊、處理模塊、存儲控制模塊以及ARM通信模塊。

2 模塊設計

2.1 I2C通信模塊

FPGA通過I2C總線[4]實現對TVP5154的配置,完成4路視頻的AD轉換。將I2CA0和I2CA1接地,把從機地址設為B8h。系統上電后,設備處于一個輸出未定義的未知狀態,直到它接收到RESET 命令。在系統上電或硬件重啟后,遵循以下自檢過程:

(1)等待1 ms,4個解碼通道的寄存器(7Fh)必須寫入00h 值。

(2)等待1 ms,讀出4個解碼通道的寄存器(81h)的版本值。

(3)驗證讀出來的值是否為54h。

(4)如果讀出的值不為54h,則需要重啟。

重復此過程,直到4個通道讀寄存器(81h)的值均為54h。

自檢完成之后,FPGA向TVP5154的 FEh寄存器寫入0Fh,讓4個解碼器同時接收FPGA的寫事務,輸出設置成標準含嵌入式同步信號的ITU-R BT.656格式的數字視頻信號,如圖2所示,包括3路同步信號:場、水平、豎直同步信號,并有一路時鐘信號,頻率為27 MHz。

2.2 視頻采集模塊

視頻采集模塊主要是將ITU656格式的視頻數據進行緩存和有效數據抽取。首先提取視頻有效數據,送入FIFO(深度為2k,可存儲一行有效數據)進行緩存。接著通過控制讀取FIFO的數據來進行行列1/2抽取。

Modelsim上截取的采集狀態轉換圖如圖3所示。先對場同步信號FID進行采樣,下降沿啟動狀態機,從NULL狀態進入ST_IDLE狀態,然后開始檢測同步信號(FF0000 XXh),出現FF狀態機跳轉到ST_FF,再出現00則跳轉到ST_00,如果檢測到還為00則跳轉到ST_START。此時根據XX的值來確定是否為有效數據,如果是非有效數據,則跳回ST_IDLE,再次跳轉;如果是有效數據,則根據XX判斷奇偶場,開始采集計數,根據要求選取采集深度,全采為1 440 B。

合成的圖像4路按順序分別位于左上、右上、左下、右下。由于視頻為隔行掃描,為實現行1/2抽取,將4路視頻信號分為兩組,其中前兩路采集偶場數據,后兩路采集奇場數據。接著分時讀取組內兩個FIFO實現列1/2抽取,以實現行列1/2抽取。抽取時需要注意的是, ITU656為YUV422格式的,視頻數據按照Cb0,Y0,Cr0,Y1,Cb1,Y2,Cr1,…輸出,每兩個像素點共享紅藍色差信息,加上亮度信息,共4 B,處理時需要將兩個像素點作為一個整體。仿真結果如圖4所示。

圖4為偶場數據處理,奇場相同。偶場有效數據在FF000080h之后,設17個有效數據,前16個數據第1路為00h~0fh,第2路為10h~1fh,第17個數據任意,采集深度為16,最后一個數據被丟棄。當FIFO1數據存入4個(或更大)之后產生FIFO讀信號flag_e開始讀取兩個FIFO的數據(為實現兩路視頻數據的同步)。flag_e作為有效數據的同步信號,由于讀操作延遲一個周期,因此調整一個時鐘周期得到flag。dout1是從FIFO1中讀取的數據,dout2是從FIFO2中讀取的數據。檢測到flag_t上升沿count清零開始計數,并用count[2]作為2選1 MUX的控制端,dout1和dout2為輸入,dout_e為輸出。奇場的數據處理是同樣的過程,得到輸出dout_o。由于奇偶場是分開的,dout分時輸出dout_e和dout_o。

2.3 視頻存儲控制模塊

選取的SRAM容量為2 MB×8,共有21根地址線,地址線分為行地址和列地址[5]。ITU656標準的視頻一幀有效數據分辨率為576×720,共576行,選擇地址線高10位adr[20..11](0~1 024)為行地址,每行720個像素點,每個像素點為2 B,每行共1440 B,選擇地址線低11位adr[10..0](0~2 048)為列地址。

行地址row[9..0]操作通過檢測同步信號flag下降沿,數據有效時同步信號為高電平,當一行有效數據存儲完成之后flag變低,行地址加1。

有效數據采集模塊輸出數據為兩路信號交替出現,需交替產生存儲地址,如下:0、1、2、3、720、721、722、723、4、5、6、7…。如果分辨率有其他要求,可根據所需來確定第2路地址的起始位置。

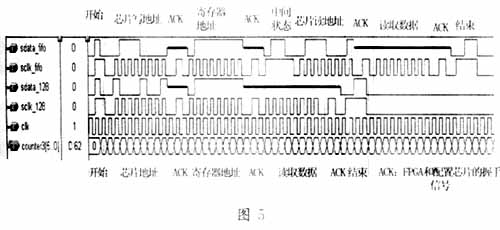

仿真中以16個數據為例,波形如圖5所示。初始賦值adr_ 2為720(第2路的起始地址,根據需要設置,16個數據設為8),其余兩個地址adr_v和adr_1賦值為0。Flag出現高時adr_v開始計數,由于兩路數據間隔4個周期,所以設置adr_v為3位,檢測最高位選擇對1、2兩個地址中一個進行+1運算,然后以adr _v[2]作為2選1 MUX控制端,列地址column作為輸出,得到所需的列地址序列。在flag下降沿之后行地址row加1,得到所需的寫地址。

乒乓緩沖的切換邏輯只需檢測行地址,當行地址達到576即第576行(對應行地址為575)數據已經存入SRAM,拉高ready信號,然后將row清零。切換兩個SRAM的操作方向,將SRAM1總線接至后面的合成模塊,而SRAM2則接至地址產生邏輯的輸出等待寫入。

2.4 視頻處理模塊

視頻處理模塊主要實現4路視頻的合成處理。根據ITU656格式,調用一個IP生成一個ROM,存入視頻幀的第一行數據,EAV和SAV為8 B,EAV后280 B為消隱數據,SAV后1 440 B為消隱數據,共1 728 B。其中EAV為FF0000B6h,SAV為FF0000ABh。

根據存儲模塊的切換邏輯送出來的READY信號,檢測到上升沿之后開始狀態跳轉,從IDLE狀態跳轉到EVEN_BLANK1狀態,設置一個模為22的計數器,包含一個模為1 728的計數器作為地址來讀取ROM中的數據。讀完ROM的數據,外計數器+1輸出一行數據,共輸出22行數據。然后跳轉到EVEN_VALID狀態,此時先讀取ROM中前288 B,并改寫EAV和SAV的最后1 B,分別改為9Dh和80h。接著開始讀取SRAM中的數據,按照行列地址進行讀取,行基地址為0,按列地址遞增讀取,讀至1 440列地址歸零,結束一行讀取,共重復288次輸出有效數據行。由于是隔行掃描,每次行地址加2,最后一次讀取的為第574行。接著狀態跳轉到EVEN_BLANK2,輸出兩行偶場消隱行,讀取ROM的數據即可。再跳轉到ODD_BLANK1,輸出23行奇場消隱行。讀取ROM的數據并改變EAV和SAV的最后1 B為F1h和ECh。然后跳至ODD_VALID輸出奇場有效數據,同EVEN _VALID,改寫EAV和SAV最后1 B為DAh和C7h,行基地址為1,每次加2,最后一次讀取的為第575行。奇場有效行輸出完成后,進入ODD_BLANK2,輸出兩行奇場消隱行。最后跳回EVEN _BLANK1輸出下一幀數據。

EVEN_BLANK1輸出22行,EVEN_ VALID輸出288行,EVEN_BLANK2輸出2行,ODD_BLANK1輸出23行,ODD_VALI D輸出288行,ODD_B LANK2輸出2行,一幀共625行標準的ITU656格式的視頻數據,并根據格式在特定位改寫同步信號。

2.5 ARM通信模塊

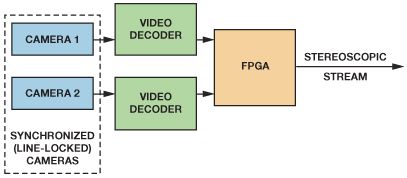

ARM通信模塊主要將合成所得的視頻數據送往ARM模塊,進行進一步的處理,包括壓縮、存儲等。接口主要有8 bit數據data[7:0],3 bit同步信號F、H、V,一路時鐘信號clk,以及握手信號。

本設計采用自頂向下的分析方法,根據系統的需求劃分功能模塊,給出一種視頻合成方法的FPGA設計,并詳細介紹各模塊的具體功能和實現。通過給定已知數據進行仿真驗證,證明了系統可以較好地實現合成操作。

電子發燒友App

電子發燒友App

評論