摘要:為解決不同性能指標數據采集系統開發時間較長的問題,提出了一種將FPGA軟核技術應用于高速數據采集系統設計的方法。系統以Xilinx公司的FPGA為例設計軟核,使用VHDL語言對軟核進行模塊化設計。介紹了數據采集系統的硬件電路、USB固件程序、USB驅動程序以及LabVIEW上位機的設計。該數據采集系統結構可移植性強,有利于縮短同類型系統設計研發周期。

數據采集在現代工業生產及科學研究中的重要地位日益突出,同時對實時采集、實時傳輸、實時處理的高速數據采集的要求也不斷提高。此外,對于不同的場合,數據采集系統的數據采樣參數要求也不同。工業生產與科研領域中對數據采集研發提出了以下的要求:(1)接口簡單靈活且有較高的數據傳輸率;(2)采集器體積小、抗干擾能力強、能夠對數據做出快速的存儲,并及時進行分析和處理;(3)設計周期短,能快速適應市場需求。

USB2.0以其即插即用、支持熱插拔的靈活性,以及高達480Mb/s的傳輸速率,成為了高速數據傳輸接口的首選。而FPGA以其工作頻率和集成度高、穩定性良好、抗干擾能力強等優點,逐步成為各領域數據采集數字電路的首選。FPGA集成軟核有設計周期短、設計投入少等優越性,且不涉及具體的物理實現,可以方便移植到各種FPGA硬件平臺,極大提高了它的靈活性和適應性。

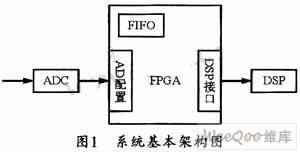

1 系統方案與結構

數據采集系統性能指標修改主要集中在A/D轉換模塊與FPGA控制模塊上,在USB2.0接口的硬件、固件、驅動程序的設計以及PC機應用軟件的設計基本沒有變化。而A/D轉換模塊的修改可以通過A/D轉換芯片的選擇及更改輸入信號調理電路設計來實現。但更換不同的A/D轉換芯片可能給A/D轉換的啟停控制、數字信號的緩存等方面帶來較多的改動。而FPGA軟核的模塊化設計可以極大地減少這方面的改動。

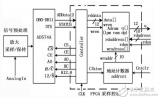

本文以TI公司的低功率高性能A/D轉換芯片ADS800為例介紹系統的設計。圖1為本數據采集系統的結構框圖。模擬信號經過THS4504全差分放大器進行信號差分放大后,輸入到ADS800進行A/D轉換。為減少不同系統中FPGA軟核改動的工作量,FPGA內部按功能設計了三個軟核作為系統的控制單元。CY7C68013作為USB控制芯片設置為從屬FIFO模式(Slave FIFO Mode),負責數字信號在采集系統與PC機間的傳輸;用戶通過LabVIEW設計的PC機應用軟件,在驅動程序的驅動下與數據采集系統進行命令以及數據的傳輸,以便對數據采集系統采集到的數據進行實時處理。

?

2 系統硬件設計

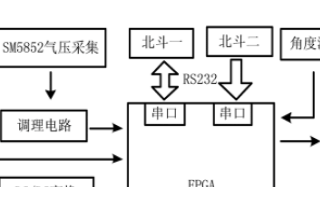

2.1 模數轉換電路

數據采集系統采樣參數調整的本質在于模數轉換電路的改變,設計者只需要更換不同的A/D轉換芯片、重新設計其硬件電路即可達到目標。本系統中模數轉換電路由信號調理電路與高速A/D轉換器組成。信號調理電路負責對待測模擬信號進行差分放大,高速A/D轉換器負責模擬信號到數字信號的轉換。

為了能精確檢測微弱信號,數據采集系統的ADC前加入了全差分放大器THS4504,采用ADS800作為A/D轉換芯片。ADS800含12bit流水線型A/D轉換內核,支持差分輸入,最高轉換速率高達40MHz[1],極好地滿足了本系統采樣頻率的要求。

2.2 FPGA芯片外圍電路

本系統FPGA采用Xilinx公司的XC3S200AN-4-FT256-C芯片。該芯片擁有20萬門邏輯單元,內含16個18KB的塊存儲器(Block RAM)與30KB分布存儲器(Distributed RAM),最高工作頻率達到326MHz[2],可滿足本系統的時序需求。

FPEA芯片外圍電路:

(1)FPGA與A/D接口模塊

ADS800的控制信號由FPGA生成,ADS800的轉換時鐘設定為30MHz,由FPGA的時鐘分頻獲得。FPGA與ADS800的連接示意圖如圖2所示。本設計中,FPGA通過ADC_OE來控制ADS800轉換數據輸出的啟停;ADS800的30MHz工作時鐘由FPGA的60MHz工作時鐘經過二分頻得到;ADS800的數據由并口輸出,FPGA內部FIFO控制單元將接收到的12bit數據轉換成16bit數據存入FPGA內的FIFO中。

當更換不同的A/D轉換芯片時,A/D轉換芯片與FPGA的連接有所不同。但對于并行輸出、流水線型的A/D轉換芯片,只需模仿上述連接方式,對輸出位數、控制時序以及FPGA時鐘分頻大小等做合適的修改即可。

(2)FPGA與USB接口模塊

本設計中使用Cypress公司生產的EZ-USB FX2LP系列的CY7C68013芯片作為USB2.0協議的微控制器芯片。由于該芯片支持480Mb/s高速傳輸,為本設計數據傳輸提供了速率保證。FPGA與CY7C68013的連接圖如圖3所示。

?

FLAGA、FLAGB腳可通過PINFLGSAB、PINFLAGSCD寄存器來選擇其工作在索引模式還是固定模式。本設計中被設置為固定模式。其中FLAGA表示EP2的空狀態(FIFO_EMPTY),FLAGB表示EP6的滿狀態(FIFO_FULL)。

2.3 USB接口外圍芯片電路

本設計使用容量為16KB的EEPROM芯片AT24C016A存儲,并設置CY7C68013的VID與PID。在CY7C68013上電并脫離復位狀態后,內部邏輯會檢查I2C端口上是否連接有串行EEPROM。如果有,則判斷連接上的EEPROM第一個字節是0xC0還是0xC2。本設計中設置EEPROM第一個字節為0xC0,設置VID=0x1234、PID=0x2211、DID=0x0001。在這種情況下,由CY7C68013內核提供USB描述符,使用EEPROM存儲的VID/PID/DID值替換CY7C68013內部的值,并設置RENUM=0。這樣,在設備重新列舉后,芯片內的程序代碼會以全新的自定義設備來加以呈現。

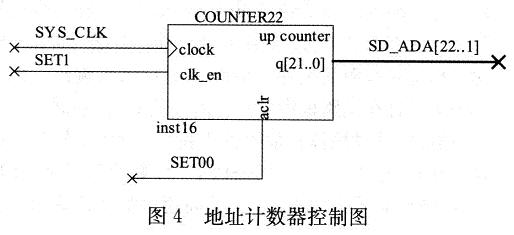

3 FPGA軟核設計

FPGA內部控制單元的功能分別由三個軟核負責完成,分別為:ADC接口控制單元、FIFO控制單元以及USB接口控制單元。三個軟核連接示意圖如圖4所示。

3.1 ADC接口控制單元

ADC接口控制單元控制數據采集的啟停和傳輸。數據采集開始時,ADC接口控制單元將時鐘信號分頻為30MHz供ADS800作轉換時鐘ADC_CLK使用。此時控制單元內寄存器CLK_CNT對ADC_CLK轉換時鐘進行周期計數,當經過7個時鐘周期后(ADS800轉換延時為6.5個時鐘周期,為了使轉換數據穩定,本設計再延時半個時鐘周期輸出)即CLK_CNT=8時,CLK_CNT清零,FIFO寫時鐘(FIFO_WR_CLK)輸出,同時端口FIFO_WR_EN置高電平,經ADC轉換完成的數據在補齊16bit后,隨時鐘FIFO_WR_CLK上升沿存入FIFO中。ADC接口控制單元狀態機工作過程如下:

(1)當FPGA上電或者復位后,狀態機進入空閑狀態(IDEL)。

(2)在空閑狀態下,當FIFO不滿(FIFO_FULL=0)且ADC_START=1時,狀態機進入轉換狀態(CONVERT),此時,ADC_CLK輸出ADC數據轉換時鐘。

(3)在轉換狀態下,當FIFO_WR_EN=1,即數據轉換延時結束時,狀態機進入寫狀態(WRITE),此時CLK_CNT清零,ADC_OE和FIFO_WR_EN都置為高電平,FIFO_WR_CLK輸出FIFO寫時鐘。

(4)在任何狀態下,如果FIFO已經寫滿(FIFO_FULL=1)或者ADC_START=0時,自動跳轉到空閑狀態。

ADC接口控制單元狀態機示意圖如圖5所示。

3.2 FIFO控制單元

本設計首先使用FPGA內部Block RAM生成FIFO。由于A/D接口控制單元輸出數據寬度為16bit,因此,FIFO寬度也設置為16bit,深度設置為4KB。FIFO可以使用Xilinx ISE套件中的Core Generator生成器,由Core Generator生成的FIFO軟核配合控制部分構成FIFO控制單元。FIFO控制單元內部結構示意圖如圖6所示。

由于本設計中數據采集系統處于異步從屬FIFO模式,且USB接口芯片讀數據的速度與ADC數據寫入FIFO的速度不同。為解決因讀寫速度不同而可能帶來的數據讀寫錯誤問題,FIFO軟核上的FULL與EMPTY兩信號線可以分別指示FIFO滿與空的狀態。當FIFO處于滿狀態時,FIFO_FULL信號置高電平,由ADC控制單元通知ADC停止采集數據;當FIFO處于空狀態時,FIFO_EMPTY信號置為高電平,由USB接口控制單元通知USB接口芯片停止讀FIFO。FIFO的讀時鐘信號(FIFO_RD_CLK)與讀使能信號(FIFO_RD_EN)由USB接口控制單元提供,寫時鐘(FIFO_WR_CLK)與寫使能信號(FIFO_WR_EN)由ADC接口控制單元提供。FIFO控制單元的工作有以下兩種特殊情況:

(1)在沒有來自PC機的控制命令情況下,如果FIFO_RD_EN=1,則FD[15:0]的數據傳輸方向為從FPGA到USB接口芯片(圖6表示為FD_OUT[15:0]),即數據從FIFO輸出至USB接口芯片;如果此時FIFO_RD_EN=0,則FD[15:0]呈高阻態。

(2)當有來自PC機的控制命令時,FD[15:0]的數據傳輸方向為從USB接口芯片到FPGA(圖6表示為FD_IN[15:0]),即PC機的控制命令寫入到USB接口芯片,再傳輸到FPGA內部命令分析器中。此時,命令分析器會根據命令控制ADC_START信號,進而控制ADC數據采集的啟停。

無論在上述哪種情況下,如果FIFO_CLEAR=0、 FIFO_WR_EN=1且FIFO_FULL=0時,FIFO_WR_CLK都有相應的時鐘信號輸入,此時ADC轉換完成的數據隨寫時鐘通過ADC_DATA[11:0]寫入FIFO中。

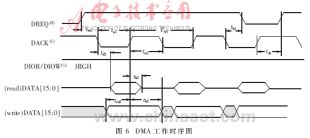

3.3 USB接口控制單元

USB接口控制單元主要完成兩種功能:(1)通過USB接口芯片實現把數據傳輸到PC機。此時FIFO中的數據先寫入EP6,當EP6寫滿時,USB接口芯片自動將數據打包傳輸到PC機。(2)協助FIFO控制單元接收來自PC機的命令數據。此時命令數據從PC機通過USB接口傳輸到EP2,然后讀取EP2的數據到FIFO控制單元的命令分析器中。USB接口控制單元狀態機工作如下:

(1)當FPGA上電或者復位后,狀態機進入空閑狀態(IDEL)。

(2)在空閑狀態下,當EP2不空(EP2_EMPTY=0)時,進入讀命令狀態(READ_COMMAND),此時令EP_ADDR[1:0]=00,FD[15:0]的傳輸方向由EP2指向FPGA,控制單元從EP2中讀出PC機傳來的控制命令。

(3)隨后進入存儲命令狀態(SOTRE_COMMAND),控制單元把傳來的控制命令存儲到FIFO控制單元內部的指令分析器中。同時控制單元置FIFO_CLEAR=1,即把FIFO控制單元內的FIFO數據清空,以準備存儲新的ADC轉換數據。任務完成后回到空閑狀態。

(4)優先處理PC機通過EP2傳來的命令,因此優先查看EP2的空狀態。在空閑狀態下,當EP2為空(EP2_EMPTY=1)且FIFO控制單元內FIFO不為空(FIFO_EMPTY=0)且EP6不滿(EP6_FULL=0)時,進入寫數據狀態(WRITE_DATA)。在寫數據狀態下,EP_ADDR[1:0]=10,控制單元選中CY7C68013的EP6,FD[15:0]方向由FPGA指向EP6,同時FIFO_RD_CLK產生一個周期時鐘,FIFO_RD_EN置為高電平,一個數據從FIFO控制單元內FIFO中讀出。

(5)隨后進入傳輸數據狀態(TRANS_DATA)。在該狀態下,令SLWR=0,數據從FIFO控制單元內FIFO寫入CY7C68013的EP6中。任務完成后進入空閑狀態。

USB接口控制單元狀態機示意圖如圖7所示。

?

4 USB接口芯片程序設計

4.1 USB固件程序

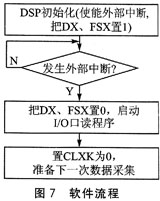

固件程序是一種嵌入在硬件設備中的軟件,通過執行固件程序,硬件設備可以完成各種特定的功能。在本設計中,CY7C68013芯片的固件程序是整個系統傳輸的控制核心,主要完成以下五種功能:(1)CY7C68013芯片的初始化;(2)輔助硬件完成設備的重新枚舉;(3)中斷處理;(4)數據接收與發送;(5)對外圍電路進行控制。

Cypress公司為提高用戶的開發效率,提供了EZ-USB FX2LP開發套件,其中包含了一個完整的固件程序架構[3]。該架構主要包含了EZ-USB FX2LP芯片的設備初始化、處理標準USB設備請求與電源管理等服務功能。用戶在開發時,只需使用Keil uVision3在固件架構下提供相應的USB描述符以及編寫外部設備功能程序代碼。固件架構流程圖如圖8所示。

主函數是固件架構流程的具體實現。主函數首先對內部狀態變量進行初始化,隨即調用TD_Init()進行用戶設備初始化,TD_Init()函數運行完成后,使能中斷,隨后進入主循環。

4.2 USB驅動程序設計

USB驅動程序位于固件程序與應用程序之間,是USB設備與PC機的通信接口。Cypress公司為用戶設計了一款通用驅動程序包(ezusb.sys),可以完成應用程序與USB接口的通信與控制任務。本設計即使用該通用驅動程序。

5 應用程序設計

應用程序通過USB驅動程序與USB接口進行通信。本設計使用LabVIEW設計應用程序。LabVIEW為用戶提供了簡單、直觀、易學的圖形編程法,相比于傳統的編程語言,LabVIEW能大量地節省開發時間。用戶通過LabVIEW應用程序可以進行對數據采集系統的控制,而且采集到的數據在控制界面中實時顯示。

本文介紹了一款較為通用、基于USB2.0接口的高速數據采集系統設計方法,通過FPGA軟核在數據采集系統中的應用,解決了硬件電路設計繁瑣復雜的問題,而且便于開發者對產品進行修改優化,可以大幅度地縮短產品的開發時間。本系統通過了硬軟件的聯合調試,系統工作正常,穩定性良好。

參考文獻

[1] Xilinx Corporation. Spartan-3AN FPGA family data sheet. 2009.???? [2] Cypress Semiconductor Corporation.EZ-USB FX2 CY7C68013 technical reference manual version2.2. 2003.???? [3] 錢峰.EZ-USB FX2單片機原理、編程及應用[M].北京:北京航空航天大學出版社,2006.

電子發燒友App

電子發燒友App

評論