。 通常,需要對(duì)這幾種路徑分別進(jìn)行約束,以便使設(shè)計(jì)工具能夠得到最優(yōu)化的結(jié)果。下面對(duì)這幾種路徑分別進(jìn)行討論。 (1)從輸入端口到寄存器: 這種路徑的約束是為了讓FPGA設(shè)計(jì)工具能夠盡可能的優(yōu)化從輸入端口到第一級(jí)寄存器

2023-10-12 12:00:02 866

866

時(shí)序不滿足約束,會(huì)導(dǎo)致以下問題: 編譯時(shí)間長的令人絕望 運(yùn)行結(jié)果靠運(yùn)氣時(shí)對(duì)時(shí)錯(cuò) 導(dǎo)致時(shí)序問題的成因及其發(fā)生的概率如下表: 由上表可見,造成時(shí)序問題的主要原因除了約束不完整,就是路徑問題,本文就時(shí)序

2020-11-29 10:34:00 7410

7410 時(shí)序約束的目的就是告訴工具當(dāng)前的時(shí)序狀態(tài),以讓工具盡量優(yōu)化時(shí)序并給出詳細(xì)的分析報(bào)告。一般在行為仿真后、綜合前即創(chuàng)建基本的時(shí)序約束。Vivado使用SDC基礎(chǔ)上的XDC腳本以文本形式約束。以下討論如何進(jìn)行最基本時(shí)序約束相關(guān)腳本。

2022-03-11 14:39:10 8731

8731 ??set_input_delay屬于時(shí)序約束中的IO約束,我之前的時(shí)序約束教程中,有一篇關(guān)于set_input_delay的文章,但里面寫的并不是很詳細(xì),今天我們就來詳細(xì)分析一下,這個(gè)約束應(yīng)該如何使用。

2022-09-06 09:22:02 1633

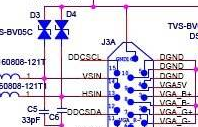

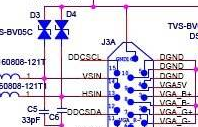

1633 在高速系統(tǒng)中FPGA時(shí)序約束不止包括內(nèi)部時(shí)鐘約束,還應(yīng)包括完整的IO時(shí)序約束和時(shí)序例外約束才能實(shí)現(xiàn)PCB板級(jí)的時(shí)序收斂。因此,FPGA時(shí)序約束中IO口時(shí)序約束也是一個(gè)重點(diǎn)。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 1382

1382 FPGA開發(fā)過程中,離不開時(shí)序約束,那么時(shí)序約束是什么?簡單點(diǎn)說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時(shí)間,這個(gè)時(shí)間必須在設(shè)定的時(shí)鐘周期內(nèi)完成,更詳細(xì)一點(diǎn),即需要滿足建立和保持時(shí)間。

2023-06-06 17:53:07 860

860

在FPGA設(shè)計(jì)中,時(shí)序約束的設(shè)置對(duì)于電路性能和可靠性都至關(guān)重要。在上一篇的文章中,已經(jīng)詳細(xì)介紹了FPGA時(shí)序約束的基礎(chǔ)知識(shí)。

2023-06-06 18:27:13 6213

6213

在FPGA設(shè)計(jì)中,時(shí)序約束對(duì)于電路性能和可靠性非常重要。在上一篇的文章中,已經(jīng)詳細(xì)介紹了FPGA時(shí)序約束的主時(shí)鐘約束。

2023-06-12 17:29:21 1230

1230 前面幾篇FPGA時(shí)序約束進(jìn)階篇,介紹了常用主時(shí)鐘約束、衍生時(shí)鐘約束、時(shí)鐘分組約束的設(shè)置,接下來介紹一下常用的另外兩個(gè)時(shí)序約束語法“偽路徑”和“多周期路徑”。

2023-06-12 17:33:53 868

868 時(shí)序路徑作為時(shí)序約束和時(shí)序分析的物理連接關(guān)系,可分為片間路徑和片內(nèi)路徑。

2023-08-14 17:50:02 452

452

前面講解了時(shí)序約束的理論知識(shí)FPGA時(shí)序約束理論篇,本章講解時(shí)序約束實(shí)際使用。

2023-08-14 18:22:14 842

842

FPGA時(shí)序分析與約束(1)本文中時(shí)序分析使用的平臺(tái):quartusⅡ13.0芯片廠家:Inter1、什么是時(shí)序分析?在FPGA中,數(shù)據(jù)和時(shí)鐘傳輸路徑是由相應(yīng)的EDA軟件通過針對(duì)特定器件的布局布線

2021-07-26 06:56:44

你好: 現(xiàn)在我使用xilinx FPGA進(jìn)行設(shè)計(jì)。遇到問題。我不知道FPGA設(shè)計(jì)是否符合時(shí)序要求。我在設(shè)計(jì)中添加了“時(shí)鐘”時(shí)序約束。我不知道如何添加其他約束。一句話,我不知道哪條路徑應(yīng)該被禁止。我

2019-03-18 13:37:27

FPGA開發(fā)過程中,離不開時(shí)序約束,那么時(shí)序約束是什么?簡單點(diǎn)說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時(shí)間,這個(gè)時(shí)間必須在設(shè)定的時(shí)鐘周期內(nèi)完成,更詳細(xì)一點(diǎn),即需要滿足建立和保持時(shí)間

2023-11-15 17:41:10

FPGA時(shí)序約束,總體來分可以分為3類,輸入時(shí)序約束,輸出時(shí)序約束,和寄存器到寄存器路徑的約束。其中輸入時(shí)序約束主要指的是從FPGA引腳輸入的時(shí)鐘和輸入的數(shù)據(jù)直接的約束。共分為兩大類:1、源同步系統(tǒng)

2015-09-05 21:13:07

由于缺乏布局優(yōu)先級(jí)信息而盲目優(yōu)化非關(guān)鍵路徑。由于模塊在每一次編譯中的布局位置變化被限定在了最優(yōu)的固定范圍內(nèi),時(shí)序收斂結(jié)果的可重現(xiàn)性也就更高。由于其粗粒度特性,LogicLock的約束信息并不很多,可以

2017-12-27 09:15:17

的時(shí)序約束。FPGA作為PCB上的一個(gè)器件,是整個(gè)PCB系統(tǒng)時(shí)序收斂的一部分。FPGA作為PCB設(shè)計(jì)的一部分,是需要PCB設(shè)計(jì)工程師像對(duì)待所有COTS器件一樣,閱讀并分析其I/O Timing

2016-06-02 15:54:04

要求(或者說是添加特定的時(shí)序約束),套用特定的時(shí)序模型,針對(duì)特定的電路進(jìn)行分析。分析的最終結(jié)果當(dāng)然是要求系統(tǒng)時(shí)序滿足設(shè)計(jì)者提出的要求。(特權(quán)同學(xué),版權(quán)所有)下面舉一個(gè)最簡單的例子來說明時(shí)序分析的基本概念

2015-07-09 21:54:41

FPGA的時(shí)序優(yōu)化高級(jí)研修班通知通過設(shè)立四大專題,幫助工程師更加深入理解FPGA時(shí)序,并掌握時(shí)序約束和優(yōu)化的方法。1.FPGA靜態(tài)時(shí)序分析2.FPGA異步電路處理方法3.FPGA時(shí)序約束方法4.FPGA時(shí)序優(yōu)化方法

2013-03-27 15:20:27

FPGA/CPLD的綜合、實(shí)現(xiàn)過程中指導(dǎo)邏輯的映射和布局布線。下面主要總結(jié)一下Xilinx FPGA時(shí)序約束設(shè)計(jì)和分析。

2023-09-21 07:45:57

FPGA 設(shè)計(jì)優(yōu)化主要分為編碼風(fēng)格、設(shè)計(jì)規(guī)劃和時(shí)序收斂三大部分,這 些因素直接決定了 FPGA 設(shè)計(jì)的成敗。 編碼風(fēng)格直接影響 FPGA 設(shè)計(jì)的實(shí)現(xiàn)并最終影響設(shè)計(jì)的性能。盡管綜合 工具集成

2022-09-29 06:12:02

FPGA靜態(tài)時(shí)序分析——IO口時(shí)序(Input Delay /output Delay)1.1概述 在高速系統(tǒng)中FPGA時(shí)序約束不止包括內(nèi)部時(shí)鐘約束,還應(yīng)包括完整的IO時(shí)序約束和時(shí)序例外約束才能

2012-04-25 15:42:03

;2.分析的基本情況是針對(duì)reg2reg這種情況,至于pin-2-reg,給出pin端的時(shí)間窗,來約束FPGA的su和hd時(shí)間,對(duì)于reg-2-pin,給出外部的時(shí)間窗,來約束FPGA內(nèi)部的tco等

2014-12-29 14:53:00

好的時(shí)序是設(shè)計(jì)出來的,不是約束出來的時(shí)序就是一種關(guān)系,這種關(guān)系的基本概念有哪些?這種關(guān)系需要約束嗎?各自的詳細(xì)情況有哪些?約束的方法有哪些?這些約束可分為幾大類?這種關(guān)系僅僅通過約束來維持嗎?1

2018-08-01 16:45:40

每日開講---學(xué)習(xí)STM32不得不看的剖析(詳細(xì)分析stm32f10x.h)摘要: 學(xué)習(xí)STM32不得不看的剖析(詳細(xì)分析stm32f10x.h)。/**這里是STM32比較重要的頭文件***************************************************************************

2021-08-05 07:44:05

本文跟大家一起詳細(xì)分析一下USB協(xié)議。

2021-05-24 06:16:36

上一篇文章中,我們詳細(xì)分析了VTIM和VMIN的功能,《嵌入式Linux 串口編程系列2--termios的VMIN和VTIME深入理解》 也明白了這兩個(gè)參數(shù)設(shè)計(jì)的初衷和使用方法,接下來我們 就詳細(xì)

2021-11-05 07:09:55

在嵌入式Linux專題(一)中已經(jīng)對(duì)嵌入式Linux系統(tǒng)的架構(gòu)及啟動(dòng)流程有了初步的介紹,本文將詳細(xì)分析嵌入式Linux系統(tǒng)啟動(dòng)流程。

2021-11-05 09:25:29

DVI接口詳細(xì)分析DVI 接口規(guī)格和定義 DVI 有DVI 1.0 和DVI 2.0 兩種標(biāo)準(zhǔn),其中 DVI 1.0 僅用了其中的一組信號(hào)傳輸信道(data0-data2 ),傳輸圖像的最高像素時(shí)鐘

2012-08-11 09:51:00

。通常,需要對(duì)這幾種路徑分別進(jìn)行約束,以便使設(shè)計(jì)工具能夠得到最 優(yōu)化的結(jié)果。下面對(duì)這幾種路徑分別進(jìn)行討論: ⑴ 從輸入端口到寄存器: 這種路徑的約束是為了讓 FPGA 設(shè)計(jì)工具能夠盡可能的優(yōu)化從

2012-03-05 15:02:22

[url=]uboot代碼詳細(xì)分析[/url]

2016-01-29 13:51:41

轉(zhuǎn)自:VIVADO時(shí)序分析練習(xí)時(shí)序分析在FPGA設(shè)計(jì)中是分析工程很重要的手段,時(shí)序分析的原理和相關(guān)的公式小編在這里不再介紹,這篇文章是小編在練習(xí)VIVADO軟件時(shí)序分析的筆記,小編這里

2018-08-22 11:45:54

報(bào)告人:林俊杰論壇用戶名:Hero2ljj一、評(píng)估開展說明開展意義FPGA開發(fā)流程包括設(shè)計(jì)輸入、功能仿真、綜合優(yōu)化、布局布線,其中綜合優(yōu)化和布局布線過程中需要考慮到時(shí)序約束實(shí)現(xiàn)問題。通常情況下如果

2017-07-05 11:00:48

本視頻是MiniStar FPGA開發(fā)板的配套視頻課程,主要通過工程實(shí)例介紹Gowin的物理約束和時(shí)序約束,課程內(nèi)容包括gowin的管腳約束及其他物理約束和時(shí)序優(yōu)化,以及常用的幾種時(shí)序約束。 本

2021-05-06 15:40:44

明德?lián)P時(shí)序約束視頻簡介FPGA時(shí)序約束是FPGA設(shè)計(jì)中的一個(gè)重點(diǎn),也是難點(diǎn)。很多人面對(duì)各種時(shí)序概念、時(shí)序計(jì)算公式、時(shí)序場景是一頭亂麻,望而生畏。現(xiàn)有的教材大部分是介紹概念、時(shí)序分析工具和計(jì)算公式

2017-06-14 15:42:26

、MulticyclePath、MaxDelay、MinDelay。但這還不是最完整的時(shí)序約束。如果僅有這些約束的話,說明設(shè)計(jì)者的思路還局限在FPGA芯片內(nèi)部。2. 核心頻率約束+時(shí)序例外約束+I/O約束 I/O

2017-10-20 13:26:35

什么是時(shí)序分析?時(shí)序約束的作用是什么?FPGA組成的三要素分別是哪些?

2021-09-18 06:05:51

三極管特性曲線詳細(xì)分析,特性曲線看不懂,

2015-06-29 16:34:40

SDRAM數(shù)據(jù)手冊(cè)有如張時(shí)序要求圖。如何使SDRAM滿足時(shí)序要求?方法1:添加時(shí)序約束。由于Tpcb和時(shí)鐘頻率是固定的,我們可以添加時(shí)序約束,讓FPGA增加寄存器延時(shí)、寄存器到管腳的延時(shí),從而使上述

2016-09-13 21:58:50

,不同的寄存器在時(shí)鐘脈沖的激勵(lì)下相互配合完成特定的功能,所以要保證不同的寄存器在同一時(shí)刻的時(shí)鐘脈沖激勵(lì)下協(xié)同工作,就需要進(jìn)行時(shí)序分析,通過分析得結(jié)果對(duì)FPGA進(jìn)行約束,以保證不同寄存器間的時(shí)序要求

2017-02-26 09:42:48

在給FPGA做邏輯綜合和布局布線時(shí),需要在工具中設(shè)定時(shí)序的約束。通常,在FPGA設(shè)計(jì)工具中都FPGA中包含有4種路徑:從輸入端口到寄存器,從寄存器到寄存器,從寄存器到輸出,從輸入到輸出的純組合邏輯。

2019-11-08 07:27:54

工程師應(yīng)該掌握的20個(gè)模擬電路(詳細(xì)分析及參考答案)

2013-08-17 09:58:13

工程師應(yīng)該掌握的20個(gè)模擬電路(詳細(xì)分析及參考答案).pdf

2013-04-07 13:28:38

求大神詳細(xì)分析電路圖個(gè)元器件作用

2013-08-04 15:46:35

內(nèi)含參考答案以及詳細(xì)分析

2023-10-07 07:15:56

本文檔的主要內(nèi)容詳細(xì)介紹的是硬件工程師必須掌握的20個(gè)重要模擬電路的概述和參考答案以及詳細(xì)分析

2023-09-27 08:22:32

電子工程師需要掌握的20個(gè)模擬電路的詳細(xì)分析

2023-09-28 06:22:26

本帖最后由 eehome 于 2013-1-5 09:52 編輯

電源電路圖最最最最最詳細(xì)分析(轉(zhuǎn)一網(wǎng)友)

2012-07-31 11:37:21

給大家詳細(xì)分析一下艾德克斯車載充電機(jī)的測試方案

2021-05-08 08:38:05

請(qǐng)問一下怎樣對(duì)stm32的啟動(dòng)代碼進(jìn)行詳細(xì)分析呢?

2021-11-26 07:10:48

時(shí)序約束與時(shí)序分析 ppt教程

本章概要:時(shí)序約束與時(shí)序分析基礎(chǔ)常用時(shí)序概念QuartusII中的時(shí)序分析報(bào)告

設(shè)置時(shí)序約束全局時(shí)序約束個(gè)別時(shí)

2010-05-17 16:08:02 0

0 本文詳細(xì)分析了ADSL系統(tǒng)中ATM層和物理層之間的UTOPIA LEVEL2接口時(shí)序,采用FPGA實(shí)現(xiàn)了UTOPIA接口設(shè)計(jì),應(yīng)用在ADSL系統(tǒng)中,數(shù)據(jù)收發(fā)正確,工作穩(wěn)定;該方案的實(shí)現(xiàn)對(duì)解決現(xiàn)有專門通信芯

2010-07-28 16:54:10 19

19 延時(shí)開關(guān)電路圖及詳細(xì)分析

圖1:

2007-11-08 10:20:09 13453

13453 筆記本使用十大陋習(xí)詳細(xì)分析

電腦越來越平民化,可是電腦卻總是出問題 由于摩爾法則的影響,整個(gè)IT產(chǎn)品業(yè)界的產(chǎn)品售價(jià)正在

2010-01-20 14:18:53 316

316 焊接技術(shù)詳細(xì)分析

焊接實(shí)質(zhì)上是將元器件高質(zhì)量連接起來最容易實(shí)現(xiàn)的方法,對(duì)于DIY高手來說,光能掌握電腦配件的性能和參數(shù)

2010-01-26 10:46:22 1630

1630 電子整流器工作原理詳細(xì)分析

2010-02-27 10:43:51 24851

24851 主板設(shè)計(jì)的5大缺陷詳細(xì)分析

第1頁:顯卡聲卡不兼容一覽

“太慘了!剛買的散熱器竟然用不上!”“好郁悶,PCI擴(kuò)展槽竟然裝不上聲卡。”

有的時(shí)候,我們經(jīng)

2010-03-15 10:52:21 1509

1509 uboot 1-1-6版本的 代碼詳細(xì)分析

2015-11-02 11:02:19 25

25 FPGA時(shí)序約束方法很好地資料,兩大主流的時(shí)序約束都講了!

2015-12-14 14:21:25 19

19 十二五規(guī)劃教材大學(xué)電路(邱關(guān)源、羅先覺版)二端口網(wǎng)絡(luò)的詳細(xì)分析和經(jīng)典例題以及解題方法

2015-12-23 18:15:36 0

0 賽靈思FPGA設(shè)計(jì)時(shí)序約束指南,下來看看

2016-05-11 11:30:19 48

48 近期的幾個(gè)單片機(jī)例程及詳細(xì)分析,感興趣的可以看看。

2016-06-21 17:02:48 3

3 半橋電源源高頻鏈逆變電路的詳細(xì)分析

2017-09-14 15:23:44 19

19 Buck變換器原理詳細(xì)分析

2017-09-15 17:26:25 30

30 一個(gè)好的FPGA設(shè)計(jì)一定是包含兩個(gè)層面:良好的代碼風(fēng)格和合理的約束。時(shí)序約束作為FPGA設(shè)計(jì)中不可或缺的一部分,已發(fā)揮著越來越重要的作用。毋庸置疑,時(shí)序約束的最終目的是實(shí)現(xiàn)時(shí)序收斂。時(shí)序收斂作為

2017-11-17 07:54:36 2326

2326

FPGA 設(shè)計(jì)的最優(yōu)結(jié)果。 何為時(shí)序約束? 為保證設(shè)計(jì)的成功,設(shè)計(jì)人員必須確保設(shè)計(jì)能在特定時(shí)限內(nèi)完成指定任務(wù)。

2017-11-24 19:37:55 4903

4903

耗費(fèi)數(shù)月精力做出的設(shè)計(jì)卻無法滿足時(shí)序要求,這確實(shí)非常令人傷心。然而,試圖正確地對(duì)設(shè)計(jì)進(jìn)行約束以保證滿足時(shí)序要求的過程幾乎同樣令人費(fèi)神。找到并確定時(shí)序約束本身通常也是非常令人頭痛的問題。 時(shí)序

2017-11-24 19:49:44 9123

9123

濾波電容器、共模電感、磁珠在EMC設(shè)計(jì)電路中是常見的身影,也是消滅電磁干擾的三大利器。對(duì)于這這三者在電路中的作用,相信還有很多工程師搞不清楚。本文從設(shè)計(jì)設(shè)計(jì)中,詳細(xì)分析了消滅EMC三大利器的原理。

2017-12-01 10:12:13 11403

11403

介紹FPGA約束原理,理解約束的目的為設(shè)計(jì)服務(wù),是為了保證設(shè)計(jì)滿足時(shí)序要求,指導(dǎo)FPGA工具進(jìn)行綜合和實(shí)現(xiàn),約束是Vivado等工具努力實(shí)現(xiàn)的目標(biāo)。所以首先要設(shè)計(jì)合理,才可能滿足約束,約束反過來檢查

2018-06-25 09:14:00 6374

6374 好的時(shí)序是設(shè)計(jì)出來的,不是約束出來的 時(shí)序就是一種關(guān)系,這種關(guān)系的基本概念有哪些? 這種關(guān)系需要約束嗎? 各自的詳細(xì)情況有哪些? 約束的方法有哪些? 這些約束可分為幾大類? 這種關(guān)系僅僅通過約束

2018-08-06 15:08:02 400

400 物聯(lián)網(wǎng)的產(chǎn)業(yè)生態(tài)是怎樣的詳細(xì)分析概述

2018-12-08 10:00:07 4642

4642 FPGA中的時(shí)序問題是一個(gè)比較重要的問題,時(shí)序違例,尤其喜歡在資源利用率較高、時(shí)鐘頻率較高或者是位寬較寬的情況下出現(xiàn)。建立時(shí)間和保持時(shí)間是FPGA時(shí)序約束中兩個(gè)最基本的概念,同樣在芯片電路時(shí)序分析中也存在。

2019-12-23 07:01:00 1894

1894

本文檔的主要內(nèi)容詳細(xì)介紹的是電子電路的復(fù)習(xí)題詳細(xì)分析

2020-04-15 08:00:00 15

15 時(shí)序分析結(jié)果,并根據(jù)設(shè)計(jì)者的修復(fù)使設(shè)計(jì)完全滿足時(shí)序約束的要求。本章包括以下幾個(gè)部分: 1.1 靜態(tài)時(shí)序分析簡介 1.2 FPGA 設(shè)計(jì)流程 1.3 TimeQuest 的使用 1.4 常用時(shí)序約束 1.5 時(shí)序分析的基本概念

2020-11-11 08:00:00 58

58 本文檔的主要內(nèi)容詳細(xì)介紹的是一些開關(guān)電源的拓?fù)浣Y(jié)構(gòu)詳細(xì)分析。

2021-01-06 00:16:00 20

20 時(shí)序分析時(shí)FPGA設(shè)計(jì)中永恒的話題,也是FPGA開發(fā)人員設(shè)計(jì)進(jìn)階的必由之路。慢慢來,先介紹時(shí)序分析中的一些基本概念。

2021-01-08 16:57:55 28

28 在高速系統(tǒng)中FPGA時(shí)序約束不止包括內(nèi)部時(shí)鐘約束,還應(yīng)包括完整的IO時(shí)序約束利序例外約束才能實(shí)現(xiàn)PCB板級(jí)的時(shí)序收斂。因此,FPGA時(shí)序約束中IO口時(shí)序約束也是重點(diǎn)。只有約東正確才能在高速情況下保證FPGA和外部器件通信正確

2021-01-13 17:13:00 11

11 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA的時(shí)序分析的優(yōu)化策略詳細(xì)說明。

2021-01-14 16:03:59 17

17 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA的時(shí)序分析的優(yōu)化策略詳細(xì)說明。

2021-01-14 16:03:59 19

19 本文檔的主要內(nèi)容詳細(xì)介紹的是如何實(shí)現(xiàn)LTE無線網(wǎng)絡(luò)優(yōu)化案例的詳細(xì)分析。

2021-01-14 16:55:41 21

21 本文檔的主要內(nèi)容詳細(xì)介紹的是功率放大電路的仿真資料詳細(xì)分析。

2021-02-01 11:28:50 28

28 正激有源鉗位的詳細(xì)分析介紹。

2021-06-16 16:57:07 56

56 約束條件可以使綜合布線工具調(diào)整映射和布局布線過程,使設(shè)計(jì)達(dá)到時(shí)序要求。例如用OFFSET_IN_BEFORE約束可以告訴綜合布線工具輸入信號(hào)在時(shí)鐘之前什么時(shí)候準(zhǔn)備好,綜合布線工具就可以根據(jù)這個(gè)約束調(diào)整與IPAD相連的Logic Circuitry的綜合實(shí)現(xiàn)過程,使結(jié)果滿足FFS的建立時(shí)間要求。 附加時(shí)序

2021-09-30 15:17:46 4401

4401 約束條件可以使綜合布線工具調(diào)整映射和布局布線過程,使設(shè)計(jì)達(dá)到時(shí)序要求。例如用OFFSET_IN_BEFORE約束可以告訴綜合布線工具輸入信號(hào)在時(shí)鐘之前什么時(shí)候準(zhǔn)備好,綜合布線工具就可以根據(jù)這個(gè)約束調(diào)整與IPAD相連的Logic Circuitry的綜合實(shí)現(xiàn)過程,使結(jié)果滿足FFS的建立時(shí)間要求。 附加時(shí)序

2021-10-11 10:23:09 4861

4861

本文章探討一下FPGA的時(shí)序約束步驟,本文章內(nèi)容,來源于配置的明德?lián)P時(shí)序約束專題課視頻。

2022-03-16 09:17:19 3255

3255

上一篇《FPGA時(shí)序約束分享01_約束四大步驟》一文中,介紹了時(shí)序約束的四大步驟。

2022-03-18 10:29:28 1323

1323

本文章探討一下FPGA的時(shí)序input delay約束,本文章內(nèi)容,來源于配置的明德?lián)P時(shí)序約束專題課視頻。

2022-05-11 10:07:56 3462

3462

明德?lián)P有完整的時(shí)序約束課程與理論,接下來我們會(huì)一章一章以圖文結(jié)合的形式與大家分享時(shí)序約束的知識(shí)。要掌握FPGA時(shí)序約束,了解D觸發(fā)器以及FPGA運(yùn)行原理是必備的前提。今天第一章,我們就從D觸發(fā)器開始講起。

2022-07-11 11:33:10 2922

2922

本文章探討一下FPGA的時(shí)序input delay約束,本文章內(nèi)容,來源于明德?lián)P時(shí)序約束專題課視頻。

2022-07-25 15:37:07 2379

2379

FPGA/CPLD的綜合、實(shí)現(xiàn)過程中指導(dǎo)邏輯的映射和布局布線。下面主要總結(jié)一下Xilinx FPGA時(shí)序約束設(shè)計(jì)和分析。

2023-04-27 10:08:22 768

768 前面幾篇文章已經(jīng)詳細(xì)介紹了FPGA時(shí)序約束基礎(chǔ)知識(shí)以及常用的時(shí)序約束命令,相信大家已經(jīng)基本掌握了時(shí)序約束的方法。

2023-06-23 17:44:00 1260

1260

FPGA開發(fā)過程中,離不開時(shí)序約束,那么時(shí)序約束是什么?簡單點(diǎn)說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時(shí)間,這個(gè)時(shí)間必須在設(shè)定的時(shí)鐘周期內(nèi)完成,更詳細(xì)一點(diǎn),即需要滿足建立和保持時(shí)間。

2023-06-26 14:42:10 344

344

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論