經(jīng)常涉及對(duì)寬帶模擬信號(hào)進(jìn)行數(shù)據(jù)采集和存儲(chǔ),以便計(jì)算機(jī)進(jìn)一步進(jìn)行數(shù)據(jù)處理。為了對(duì)高速模擬信號(hào)進(jìn)行不失真采集,根據(jù)奈奎斯特定理, 采樣頻率必須為信號(hào)頻率的2 倍以上,但在電阻抗多頻及參數(shù)成像技術(shù)中正交

2023-09-15 09:45:01 1054

1054

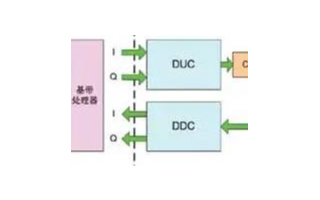

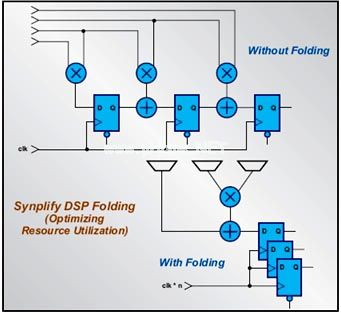

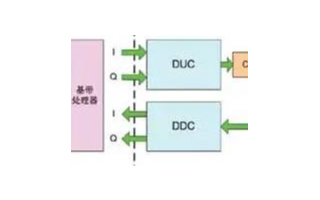

中頻技術(shù)通常包括上下變頻(DUC/DDC)、波峰因子衰減(CFR)和數(shù)字預(yù)失真(DPD)。 DUC/DDC DUC實(shí)現(xiàn)了從“復(fù)”基帶(Baseband)信號(hào)到“實(shí)”帶通(Pas***and)信號(hào)的轉(zhuǎn)換。輸入的復(fù)基帶信號(hào)采樣率相對(duì)較低

2023-10-21 18:59:00 2568

2568

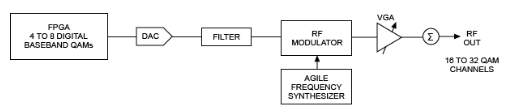

本文介紹了基于MAX5879等RF DAC的RF直接變頻發(fā)送器設(shè)計(jì),文章列舉了零中頻、正交IF調(diào)制、高中頻調(diào)制以及RF直接變頻架構(gòu),詳細(xì)介紹了RF直接變頻帶給智能手機(jī)、平板電腦等無線設(shè)備的優(yōu)勢。

2013-04-03 16:40:39 2445

2445

FPGA實(shí)現(xiàn)直接數(shù)字頻率合成(DDS)的原理、電路結(jié)構(gòu)和優(yōu)化方法介紹了利用現(xiàn)場可編程邏輯門陣列FPGA實(shí)現(xiàn)直接數(shù)字頻率合成(DDS)的原理、電路結(jié)構(gòu)和優(yōu)化方法。重點(diǎn)介紹了DDS技術(shù)在FPGA中的實(shí)現(xiàn)

2012-08-11 18:10:11

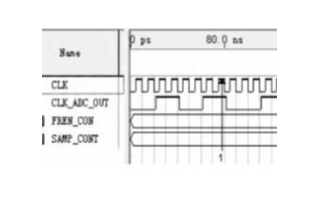

1、FPGA內(nèi)部AD多通道采樣實(shí)驗(yàn)設(shè)計(jì)與實(shí)現(xiàn)編寫程序,使用Anlogic 自帶的ADC進(jìn)行四通道數(shù)據(jù)輪詢采集,同時(shí)介紹TD軟件IP核的用法。本實(shí)驗(yàn)設(shè)計(jì)使用FPGA自帶的12位串行AD芯片工作,將直流

2022-07-15 18:18:37

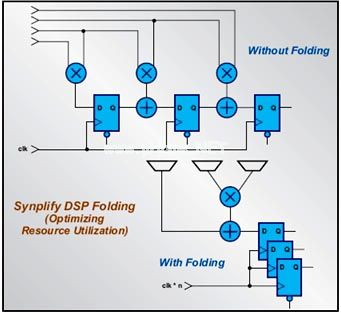

以及最新的DSP系統(tǒng)工具的概況;接著主要介紹了計(jì)算機(jī)算法的概念、理論、有限字長效用、FIR和IIR濾波器的實(shí)現(xiàn)、多速率和自適應(yīng)信號(hào)處理的FPGA實(shí)現(xiàn);最后,介紹了System Genrerator

2009-07-21 09:22:42

的主要功能為實(shí)現(xiàn)信號(hào)的隔離,以及對(duì)輸入信號(hào)進(jìn)行功率的調(diào)整,達(dá)到信號(hào)處理最佳的狀態(tài)。在接收通道中,將外部信號(hào)與內(nèi)部信號(hào)隔離,并將接收中頻信號(hào)接口的輸入阻抗調(diào)整為50Ω、信號(hào)由0.7Vpp~1Vpp 調(diào)整為

2018-08-13 07:18:30

插值濾波器設(shè)計(jì)-明德?lián)P至簡設(shè)計(jì)與應(yīng)用FPGA

2019-08-16 10:34:20

文章主要講CIC理論基礎(chǔ),下個(gè)文章講FPGA實(shí)現(xiàn)。級(jí)聯(lián)積分梳狀濾波器又稱CIC。這是多速率信號(hào)處理中一種結(jié)構(gòu)簡單的濾波器,只需要加法器和寄存器即可實(shí)現(xiàn),可以靈活的設(shè)置抽取因子和插值因子,并且CIC是一種

2021-08-17 08:27:40

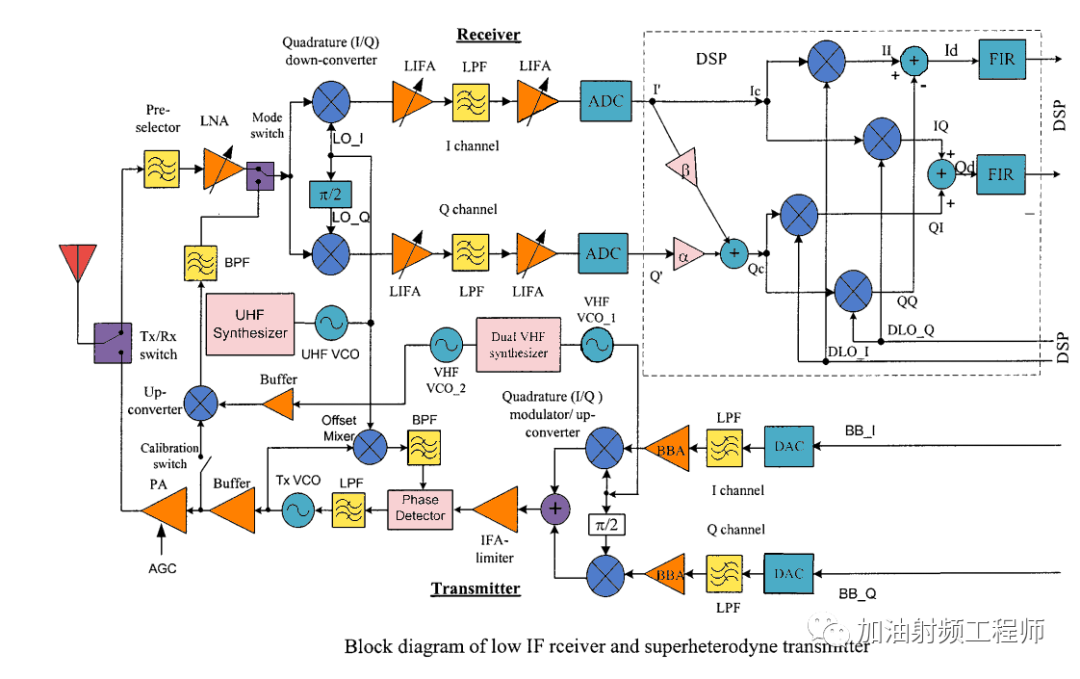

(IF)信號(hào)。正交解調(diào)器再將中頻信號(hào)向下轉(zhuǎn)換成復(fù)基帶(BB)信號(hào),在復(fù)基帶處,信號(hào)被雙通道模數(shù)轉(zhuǎn)換器(ADC)采樣并傳遞到數(shù)字處理器。 奈奎斯特采樣定理規(guī)定,采樣頻率必須至少是信號(hào)帶寬的兩倍;但在

2018-09-06 14:58:45

。這允許更輕松的模擬濾波,以便消除能向下混疊到被捕獲的帶寬范圍內(nèi)并降低接收器靈敏度的干擾信號(hào)。圖1展示了兩個(gè)實(shí)例:一種以接近奈奎斯特速率的速率采樣的信號(hào)以及一種被過采樣的信號(hào)。在被過采樣的實(shí)例中,模擬抗

2018-09-06 14:58:46

以及最新的DSP系統(tǒng)工具的概況;接著主要介紹了計(jì)算機(jī)算法的概念、理論、有限字長效用、FIR和IIR濾波器的實(shí)現(xiàn)、多速率和自適應(yīng)信號(hào)處理的FPGA實(shí)現(xiàn);最后,介紹了System Genrerator

2009-07-21 09:20:11

以及最新的DSP系統(tǒng)工具的概況;接著主要介紹了計(jì)算機(jī)算法的概念、理論、有限字長效用、FIR和IIR濾波器的實(shí)現(xiàn)、多速率和自適應(yīng)信號(hào)處理的FPGA實(shí)現(xiàn);最后,介紹了System Genrerator

2009-07-24 13:07:08

近期在利用fpga spartan6系列進(jìn)行OFDM系統(tǒng)開發(fā)工作,基帶實(shí)現(xiàn)平臺(tái)為xilinx spartan6系列,我們系統(tǒng)結(jié)構(gòu)是這樣的,發(fā)射基帶是:編碼+qpsk映射+ifft+插值濾波+dac

2013-08-14 22:02:34

求教,labview用一維插值控件在想要插值的地方插好值后,如何與原來未插值的數(shù)據(jù)合并起來,比如原來的數(shù)組值為1,7,13;插值以后想變?yōu)?,3,5,7,9,11,13,該如何做??現(xiàn)在在想插值的地方已插好值,但初始值沒有。如圖標(biāo)題9999為待插值文件,標(biāo)題ok為插值好的文件。

2016-08-26 17:55:33

本帖最后由 我來看看你在干什么 于 2018-5-15 09:10 編輯

用verilog實(shí)現(xiàn)EMD算法,需要用到三次樣條插值法,請(qǐng)問有做過類似算法實(shí)現(xiàn)的嗎,可以講一下verilog實(shí)現(xiàn)三次樣條插值的思路,或者相互交流探討一下嗎?

2018-05-13 21:34:56

本節(jié)知識(shí)我們講解如何用FPGA建立正交解碼器正交解碼器FPGA是最適合建立正交解碼器。正交信號(hào)是什么? 正交信號(hào)是兩個(gè)信號(hào)產(chǎn)生相位差90度。機(jī)械系統(tǒng)中,它們被用來確定軸(或旋轉(zhuǎn))運(yùn)動(dòng)。這里是一軸

2012-03-15 09:29:46

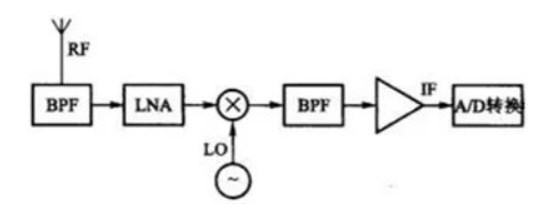

一種中頻直接采樣方案

2012-11-25 15:47:05

針對(duì)視頻的輸出顯示要求,重點(diǎn)介紹了基于雙線性插值算法的實(shí)現(xiàn)。ModelSim的仿真結(jié)果表明,該算法符合多屏幕顯示系統(tǒng)的要求。關(guān)鍵詞 視頻監(jiān)控;視頻圖像處理;雙線性插值;FPGA;多屏幕

2019-06-28 07:06:54

正交誤差在2°左右,即幅相誤差引入的鏡像功率在-34 dB左右。這樣的技術(shù)性能限制了信號(hào)處理器性能的提高。

2019-11-07 06:38:29

什么是數(shù)字中頻?FPGA怎么實(shí)現(xiàn)數(shù)字中頻?

2021-05-08 08:05:40

,D是插值倍數(shù)。如果我們直接用F1*D倍的采樣率采信號(hào),得到的頻譜會(huì)發(fā)現(xiàn),就不會(huì)有中間兩個(gè)波形,因此,這兩個(gè)波形是多余的,書上叫做是鏡像頻譜。既然是多余的,我們就可以將它用一個(gè)低通濾波器濾掉,這樣

2018-11-15 00:27:19

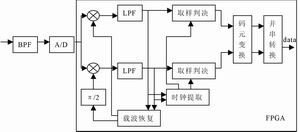

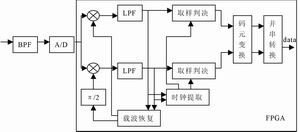

本文研究了中頻軟件無線電的實(shí)現(xiàn)方案,并設(shè)計(jì)了基于FPGA的通用硬件平臺(tái)。在此平臺(tái)上,通過PC機(jī)下載軟件,實(shí)時(shí)實(shí)現(xiàn)了軟件無線電中頻至基帶的波形處理和多種不同的調(diào)制解調(diào)方式。

2021-04-29 06:27:47

本文結(jié)合FPGA的并行處理優(yōu)勢,提出了一種利用信號(hào)FFT插值系數(shù)的幅度和相位信息來構(gòu)造頻率修正項(xiàng)的新算法。

2021-04-29 06:02:26

源碼-基于FPGA設(shè)計(jì)的插值濾波器設(shè)計(jì).rar (12.14 KB )

2019-05-08 06:35:28

內(nèi)容簡介:掌握FPGA的編程仿真,實(shí)現(xiàn)數(shù)控圓弧插補(bǔ)的程序設(shè)計(jì)。插補(bǔ)程序設(shè)計(jì)除考慮幾何關(guān)系,還需要考慮速度的變化。

2013-04-23 09:32:46

1,背景

利用FPGA做數(shù)據(jù)處理、系統(tǒng)控制時(shí),經(jīng)常需要做線性插值。如圖(1)所示,給點(diǎn)A和B的x,y坐標(biāo),需要求A,B中間某一點(diǎn)C的坐標(biāo)。限定x取整數(shù)。

圖(1) 插值示意圖

根據(jù)A,B兩點(diǎn)即可

2023-11-20 23:10:38

上次分享了基于FPGA的線性插值的背景和方法原理,今天分享

方法原理的驗(yàn)證。

通常FPGA的開發(fā)分為電路功能設(shè)計(jì)、設(shè)計(jì)輸入、功能仿真、綜合優(yōu)化、綜合后仿真、實(shí)現(xiàn)、布線后仿真、板級(jí)仿真以及芯片編程

2023-11-23 23:09:43

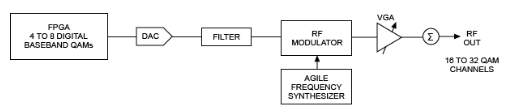

引言無線電發(fā)射器在經(jīng)歷了若干年的發(fā)展后,逐步從簡單中頻發(fā)射架構(gòu)過渡到正交中頻發(fā)送器、零中頻發(fā)送器。而這些架構(gòu)仍然存在局限性,最新推出的RF直接變頻發(fā)送器能夠克服傳統(tǒng)發(fā)送器的局限性。本文比較了無

2019-07-04 08:26:10

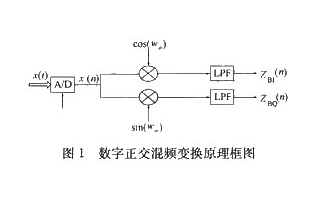

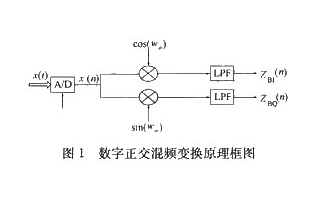

采用ADC(LTC2208)、FPGA和SDRAM(HY57V561620)設(shè)計(jì)高速的數(shù)據(jù)采集及正交下變頻系統(tǒng),其中數(shù)據(jù)采樣速率90MSPS;實(shí)現(xiàn)70M中頻的數(shù)字正交下變頻…………請(qǐng)求大牛的幫助啊,我是小菜鳥,這方面還需要你們的大力提攜啊,萬分感謝

2014-04-01 10:44:33

影響采樣精度以及計(jì)算出來的頻率精度,對(duì)于依靠直接采樣手段獲取頻率信息的接收機(jī)來講,這顯然是不適合的。針對(duì)這種技術(shù)與需求的矛盾,將欠采樣技術(shù)廣泛應(yīng)用于這種情形中以解決問題。1 欠采樣接收機(jī)原理欠采樣進(jìn)行

2018-07-31 10:24:36

數(shù)字上變頻/下變頻(DUC/DDC)是數(shù)字中頻設(shè)計(jì)的重要組成部分,其功能是將基帶信號(hào)經(jīng)過內(nèi)插濾波后變到中頻的頻率,或者將中頻的信號(hào)經(jīng)過抽取濾波后降到基帶的頻率上。本文的主要目的就是介紹多天線多載波數(shù)字上下變頻的FPGA實(shí)現(xiàn)方法,以及Altera提供的一種數(shù)字信號(hào)處理的工具,DSP BUILDER。

2019-09-25 08:22:51

rt,收集了20個(gè)數(shù)據(jù)點(diǎn),然后畫在xy圖上,現(xiàn)在想要找出給定的y值,它所對(duì)應(yīng)的x值。然后用了這個(gè)插值工具,發(fā)現(xiàn)了一個(gè)問題。當(dāng)數(shù)據(jù)是一種上升的趨勢時(shí),它能找到第一個(gè)y值(0.03)所對(duì)應(yīng)的x值。如下

2015-11-04 17:29:36

本文基于隨著通信市場模塊化、小型化、低互調(diào)、高效率的發(fā)展趨勢,重點(diǎn)討論了通信設(shè)備內(nèi)模塊與設(shè)備外模塊的連接器設(shè)計(jì)與實(shí)現(xiàn),主要討論如何實(shí)現(xiàn)快插連接器的低互調(diào)以及降低電磁泄漏,介紹了母端連接器采用劈6 槽

2021-05-20 06:04:31

中頻調(diào)制解調(diào)系統(tǒng)具有哪些特點(diǎn)?如何利用FPGA去實(shí)現(xiàn)中頻調(diào)制解調(diào)系統(tǒng)?

2021-04-28 07:21:00

MATLAB程序。我們知道Matlab的一個(gè)強(qiáng)大之處在于給我們提供了很多API可以調(diào)用,為我們節(jié)省了不少時(shí)間,而且大多數(shù)的函數(shù)我們都是可以看到源碼的。比如我們今天所說的插值濾波器,可以直接

2020-12-24 16:03:16

如何設(shè)計(jì)并實(shí)現(xiàn)一種高性能中頻采樣系統(tǒng)?中頻采樣系統(tǒng)系統(tǒng)總體設(shè)計(jì)由哪些組成?它們分別有什么作用?

2021-04-07 07:09:32

式提供給用戶,包括A/D采樣,數(shù)字下變頻,中頻濾波器,包絡(luò)檢波器,視頻濾波器,以及幅度定標(biāo)等模塊。如何合理的布局,組織數(shù)據(jù)流鏈路,以及資源優(yōu)化都是數(shù)字中頻技術(shù)研究課題之一。 數(shù)字中頻實(shí)現(xiàn)中重要的一個(gè)模塊

2015-10-29 17:08:06

、數(shù)字濾波器設(shè)計(jì)(IIR、FIR及特殊形式的濾波器)等;下篇內(nèi)容包括信號(hào)的正交變換(正交變換的定義與性質(zhì)、K-L變換、DCT及其在圖像壓縮中的應(yīng)用)、信號(hào)處理中若干典型算法(如抽取與插值、子帶分解、調(diào)制

2023-09-19 08:01:36

數(shù)字陣列雷達(dá)可以實(shí)現(xiàn)陣元級(jí)的數(shù)字收發(fā),為了減少射頻前端的復(fù)雜性同時(shí)降低對(duì)高采樣率的需求,本文簡單介紹正交解調(diào)接收機(jī),或者稱為零中頻接收機(jī),從而每個(gè)陣元只需要一個(gè)本振就可以了。零中頻接收機(jī)的一個(gè)重要

2020-08-29 08:23:49

求教大俠指導(dǎo)樣條插值。如果已知一組數(shù)據(jù)【(x,y)】,對(duì)其按等間隔(非時(shí)間)采樣后【(c1,y1)】。現(xiàn)在想通過對(duì)原數(shù)據(jù)進(jìn)行樣條插值,并求出在y1時(shí)刻的x1值序列。該如何實(shí)現(xiàn)???跪求啊!!!

2013-10-31 21:36:45

以及系統(tǒng)實(shí)現(xiàn)的復(fù)雜度。本文介紹的等效時(shí)間采樣技術(shù)由于使用了FPGA 采樣技術(shù), 使得在被采樣信號(hào)的一個(gè)周期中相較于一個(gè)周期僅能采集一個(gè)點(diǎn)的順序等效時(shí)間采樣有很大的提高,并且可以控制被采集信號(hào)一個(gè)周期

2020-10-21 16:43:20

好像跟插值DAC沒有關(guān)系吧?我用matlab量化一個(gè)正弦波至于FPGA中,用FPGA驅(qū)動(dòng)AD9957,結(jié)果出了個(gè)奇怪的波形,如圖。怎么辦?寄存器CFR1,CFR2,CFR3配置為默認(rèn)值,只把工作模式改為

2018-12-04 09:36:16

框圖上面看,是要直接對(duì)這樣的數(shù)據(jù)進(jìn)行插值濾波么?附件紅色標(biāo)記處,DATA ASSEMBLER對(duì) 數(shù)據(jù)進(jìn)行的是什么處理?對(duì)于正交半帶濾波,貴司有相關(guān)的介紹資料么?附件DAC.PNG180.7 KB

2019-01-10 11:50:46

請(qǐng)問一下基于FPGA技術(shù)如何實(shí)現(xiàn)彩色圖像的Bayer插值變換?

2021-04-29 06:48:02

窄帶正交數(shù)字中頻TX單次轉(zhuǎn)換觀測RX

2018-10-10 15:38:28

搬移到基帶不會(huì)被Fs/2內(nèi)的信號(hào)干擾,因此,Pipeline型的ADC也常常被稱為欠采樣ADC。(原文 德州儀器高性能單片機(jī)和模擬器件在高校中的應(yīng)用和選型指南 p13),請(qǐng)問這里所說的把中頻處的信號(hào)搬移到基帶進(jìn)行處理,是怎么實(shí)現(xiàn)的?不理解?請(qǐng)教

2019-02-26 08:59:33

西安交通大學(xué)電信學(xué)院 周俊峰 陳濤摘要:介紹了Altera公司的即FPGA器件ACEXEPlK50的主要特點(diǎn),給出了由ACEXEPlK50實(shí)現(xiàn)直接數(shù)字頻率合成的工作原理、設(shè)計(jì)思路、電路結(jié)構(gòu)和改進(jìn)優(yōu)化

2019-06-18 06:05:34

校正(請(qǐng)參見圖 1)。本文將逐一介紹這些特性的功能和作用。 圖 1 DAC34H84 功能結(jié)構(gòu)圖 第一個(gè)數(shù)字模塊是插值模塊,它負(fù)責(zé)增加 DAC 內(nèi)部數(shù)字信號(hào)的采樣速率。一般而言,利用兩倍采樣速率增加步驟,來實(shí)現(xiàn)插值。利用在輸入采樣點(diǎn)之間插入零來完成這項(xiàng)工作,其在 fIF 和 FIN – f…

2022-11-23 07:20:34

提出了一個(gè)欠采樣中頻收發(fā)器的體系結(jié)構(gòu),它在中頻數(shù)字化以前先通過欠采樣將中頻頻率變到一個(gè)較低的頻率。該結(jié)構(gòu)在ADC 之前不需要鏡像抑制濾波器且只有一條模擬路徑,通過

2009-08-10 08:57:32 24

24 根據(jù)軟件無線電的思想,用可編程器件FPGA 實(shí)現(xiàn)了QPSK 解調(diào),采用帶通采樣技術(shù)對(duì)中頻為70MHz 的調(diào)制信號(hào)采樣,通過對(duì)采樣后的頻譜進(jìn)行分析,用相干解調(diào)方案實(shí)現(xiàn)了全數(shù)字解調(diào)

2009-08-27 11:00:14 68

68 根據(jù)中頻采樣多模式數(shù)字接收機(jī)的理論,利用專用數(shù)字下變頻器、數(shù)字信號(hào)處理器為主的芯片,構(gòu)建了一種在中頻直接采樣的多模式數(shù)字接收機(jī)系統(tǒng)。并對(duì)各個(gè)模塊的應(yīng)用設(shè)計(jì),

2009-08-28 12:03:49 36

36 本文闡述了雷達(dá)中頻信號(hào)相干檢波的原理,根據(jù)該原理使用FPGA 對(duì)特定的雷達(dá)中頻信號(hào)進(jìn)行采樣來實(shí)現(xiàn)正交數(shù)字相干檢波,設(shè)計(jì)所使用軟件是MentorGraphics 的FPGA Advantage,完成了

2010-06-15 08:26:41 53

53 本文研究了用DDS加乘法器實(shí)現(xiàn)正交數(shù)字混頻器的設(shè)計(jì)及其完整的驗(yàn)證方法,用DDS產(chǎn)生的正/余弦正交本振序列與模擬信號(hào)通過A/D采樣數(shù)字化后的數(shù)字序列相乘,再通過數(shù)字低通濾波實(shí)現(xiàn)

2010-07-17 18:02:32 46

46 提出了一種改進(jìn)型中頻數(shù)字化正交解調(diào)結(jié)構(gòu),通過在現(xiàn)場可編程門陣列內(nèi)部對(duì)采樣數(shù)據(jù)流拆分后,分路進(jìn)行數(shù)字解調(diào)的方法,大幅降低了現(xiàn)場可編程門陣列的內(nèi)核工作頻率。解決了

2010-11-22 15:09:51 0

0

為提高中頻采樣系統(tǒng)性能,降低板級(jí)噪聲,加大采樣頻率的靈活性,設(shè)計(jì)并實(shí)現(xiàn)一種高性能中頻采樣系統(tǒng)。該系統(tǒng)利用AD9518-4實(shí)現(xiàn)可配置的采樣時(shí)鐘,根據(jù)不同的采樣要

2010-12-07 13:40:23 22

22 摘 要:本文提出了一種基于FPGA的寬帶中頻數(shù)字接收機(jī)的實(shí)現(xiàn)方法。

2006-03-11 13:19:24 1247

1247

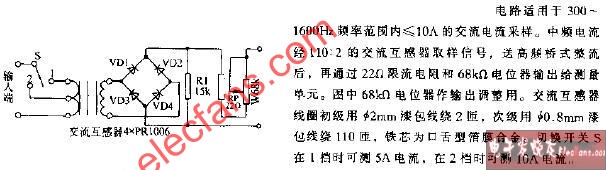

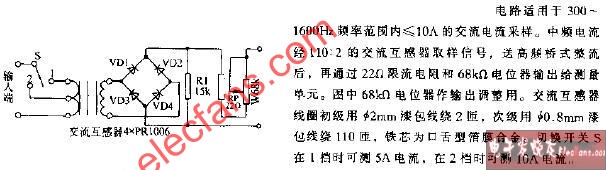

中頻大電流信號(hào)采樣電路

2009-02-10 09:10:38 1293

1293

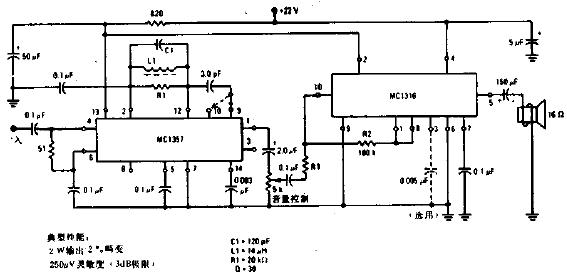

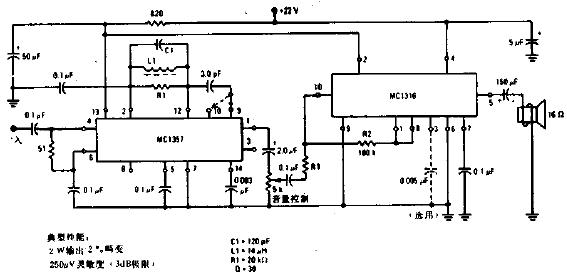

帶有正交檢波器的電視伴音中頻或調(diào)頻中頻放大器電路圖

2009-04-15 08:47:21 1000

1000

用FPGA實(shí)現(xiàn)音頻采樣率的轉(zhuǎn)換

如今,即使低成本FPGA也能提供遠(yuǎn)遠(yuǎn)大于DSP的計(jì)算能力。目前的FPGA包含專用乘法器甚至DSP乘法/累加(MAC)模塊,能以550MHz以上的時(shí)鐘速度處理

2010-03-01 10:50:05 3788

3788

在對(duì)中頻GPS信號(hào)理論建模與分析的基礎(chǔ)上,采用Matlab/Simulink構(gòu)建了一種精確的數(shù)字中頻GPS信號(hào)軟件模擬器,考慮了噪聲、欠采樣以及接收機(jī)時(shí)鐘誤差等的影響。軟件模擬器的實(shí)現(xiàn)采用Matl

2011-03-30 16:56:29 35

35 CDMA200系統(tǒng)中,信道是經(jīng)過QPSK四相擴(kuò)頻正交調(diào)制傳輸?shù)模瑪?shù)字中頻與模擬中頻相比能產(chǎn)生嚴(yán)格的幅相平衡正交信號(hào),處理時(shí)能保證有嚴(yán)格的線性相位。為此介紹了CDMA200系統(tǒng)數(shù)字中頻調(diào)制

2011-04-08 15:20:51 43

43 傳統(tǒng)的中頻數(shù)字化正交解調(diào)系統(tǒng)中芯片選擇的限制及成本的大幅上升。為此提出了一種新的中頻數(shù)字化 正交解調(diào) 系統(tǒng)結(jié)構(gòu),在保留高速A/D的高數(shù)據(jù)率輸出的同時(shí),大幅降低現(xiàn)場可編程

2011-10-08 11:09:14 4434

4434

為了對(duì)中頻PCM信號(hào)進(jìn)行直接解調(diào),提出一種全新的數(shù)字化PCM中頻解調(diào)器的設(shè)計(jì)方法。在實(shí)現(xiàn)過程中,采用大規(guī)模的FPGA芯片對(duì)位幀同步器進(jìn)行了融合,便于設(shè)備的集成化和小型化。這種新

2012-03-05 17:51:52 58

58 基于FPGA實(shí)現(xiàn)變采樣率FIR濾波器的研究

2017-01-08 15:59:09 19

19 基于FPGA的高速多通道AD采樣系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)_徐加彥

2017-01-18 20:23:58 12

12 正交相位調(diào)制,理論介紹。

2017-09-20 08:51:17 10

10 )全部奈奎斯特帶寬背后的動(dòng)因是,降低功耗、在日益密集的封裝中減輕熱量問題、降低成本、延長備用時(shí)間或電池壽命等需求在本文中,我們將探討這種類型的設(shè)計(jì)要面臨的一些挑戰(zhàn)和所擔(dān)心的問題,同時(shí)在信號(hào)帶寬接近 100MHz 時(shí),對(duì)直接轉(zhuǎn)換與中頻采樣 (IF--sampling) 進(jìn)行比較。

2017-12-04 06:33:01 1943

1943

本文檔的目的是介紹與高速、數(shù)模轉(zhuǎn)換器(DAC)相關(guān)的廣泛的理論和主題。該文件提供了關(guān)于采樣理論、數(shù)據(jù)表規(guī)范、常見系統(tǒng)級(jí)關(guān)注以及插值FAC、數(shù)字混合和正交調(diào)制器校正的內(nèi)插DAC的共同功能的細(xì)節(jié)。

2018-05-25 16:14:09 9

9 高速中頻采樣信號(hào)處理平臺(tái)在實(shí)際應(yīng)用中有很大的前景,提出采用FPGA+DSP的處理結(jié)構(gòu),結(jié)合高性能A/D和D/A處理芯片,設(shè)計(jì)了一個(gè)通用處理平臺(tái),并對(duì)其主要性能進(jìn)行了測試。

2018-10-18 16:36:48 4637

4637

,如何在充分利用現(xiàn)有FPGA器件資源情況下能更高效的實(shí)現(xiàn)所需模塊功能是值得深入研究的。本文首先介紹了實(shí)際應(yīng)用中常見的中頻接收機(jī)各模塊,然后通過編寫各自的硬件描述語言分別映射到三種不同的FPGA芯片,最終通過布線工具軟件的布線報(bào)告得出相關(guān)的設(shè)計(jì)結(jié)論。

2019-11-28 18:00:41 6

6 在FPGA中,如果要將一個(gè)采樣率為480MHz,中頻頻率為302.5MHz的信號(hào)變頻到零中頻的基帶信號(hào),要怎么做呢?

2020-01-07 14:45:43 592

592 電子戰(zhàn)設(shè)備的要求。為此,人們提出了對(duì)中頻信號(hào)直接采樣,經(jīng)過混頻來實(shí)現(xiàn)正交數(shù)字下變頻的方案,這種下變頻的方法可以實(shí)現(xiàn)很高精度的正交混頻,能滿足高鏡頻抑制的要求。采用可編程器件FPGA對(duì)該算法流程進(jìn)行實(shí)現(xiàn),能滿足在高采樣率下的信號(hào)時(shí)實(shí)處理要求,在電子戰(zhàn)領(lǐng)域中有著重要的意義。

2020-03-04 09:07:47 1663

1663

基于軟件無線電(SDR)的思想,介紹了一種新型FM調(diào)制方法——正交調(diào)制,并利用Xilinx的高級(jí)系統(tǒng)級(jí)FPGA仿真工具System Generator for DSP對(duì)這種正交調(diào)制方法進(jìn)行建模,仿真

2020-06-29 18:04:43 18

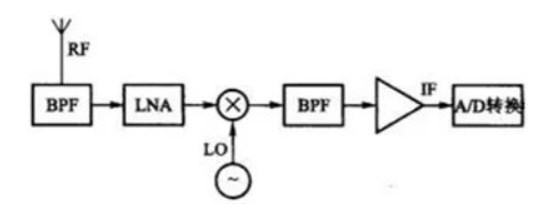

18 一、什么是中頻采樣,什么是IQ采樣 射頻接收系統(tǒng)通常使用數(shù)字信號(hào)處理算法進(jìn)行信號(hào)解調(diào)和分析,因此需要使用ADC對(duì)信號(hào)進(jìn)行采樣。根據(jù)采樣頻率的不同,可以分為射頻直接采樣、中頻采樣、IQ采樣。射頻采樣

2020-12-02 14:03:25 9031

9031 本文檔的主要內(nèi)容詳細(xì)介紹的是基于FPGA的AD采樣的實(shí)現(xiàn)免費(fèi)下載。

2021-01-21 15:33:54 31

31 針對(duì)高速率QPSK數(shù)據(jù)傳輸鏈系統(tǒng),比較分析了數(shù)字中頻接收與零中頻接收的優(yōu)、缺點(diǎn),并提出了一種基于多相濾波的寬帶中頻正交采樣數(shù)字零中頻接收方案。基于FPGA對(duì)此數(shù)字零中頻正交變換方案進(jìn)行了實(shí)現(xiàn)和驗(yàn)證,同時(shí),對(duì)一種全數(shù)字零中頻QPSK信號(hào)的高速解調(diào)算法及其FPGA硬件實(shí)現(xiàn)進(jìn)行了介紹。

2021-03-19 17:43:12 11

11 軟件無線電中信號(hào)中頻與采樣頻率選擇說明。

2021-03-25 09:50:52 13

13 LT5502:400 MHz正交中頻解調(diào)器,帶RSSI數(shù)據(jù)表

2021-05-23 13:31:52 6

6 射頻接收系統(tǒng)通常使用數(shù)字信號(hào)處理算法進(jìn)行信號(hào)解調(diào)和分析,因此需要使用ADC對(duì)信號(hào)進(jìn)行采樣。根據(jù)采樣頻率的不同,可以分為射頻直接采樣、中頻采樣、IQ采樣。射頻采樣和中頻采樣只需要一路ADC,采樣結(jié)果

2022-07-28 09:05:47 2627

2627 :針對(duì)高速率 QPSK 數(shù)據(jù)傳輸鏈系統(tǒng),比較分析了數(shù)字中頻接收與零中頻接收的優(yōu)、缺點(diǎn),并提出了一種基

于多相濾波的寬帶中頻正交采樣數(shù)字零中頻接收方案。基于 FPGA 對(duì)此數(shù)字零中頻正交變換方案

2022-12-12 15:44:36 3

3 具有12至14位高分辨率的現(xiàn)代高速數(shù)模轉(zhuǎn)換器(DAC)為采用直接調(diào)制方案的新型發(fā)射器設(shè)計(jì)奠定了基礎(chǔ)。在此類設(shè)計(jì)中,調(diào)制后的傳輸信號(hào)直接在基頻上生成。到目前為止,這種方法僅用于生成有線電視系統(tǒng)中正交

2023-02-28 14:13:23 1800

1800

點(diǎn)擊上方 藍(lán)字 關(guān)注我們 在電阻抗多頻及參數(shù)成像技術(shù)中正交序列數(shù)字解調(diào)法的抗噪性能對(duì)信號(hào)每周期的采樣點(diǎn)數(shù)決定,采樣點(diǎn)數(shù)越多,抗噪性能越高。當(dāng)采樣信號(hào)頻率很高時(shí),為了在被采樣信號(hào)的一周期內(nèi)多采樣

2023-07-29 09:00:01 537

537

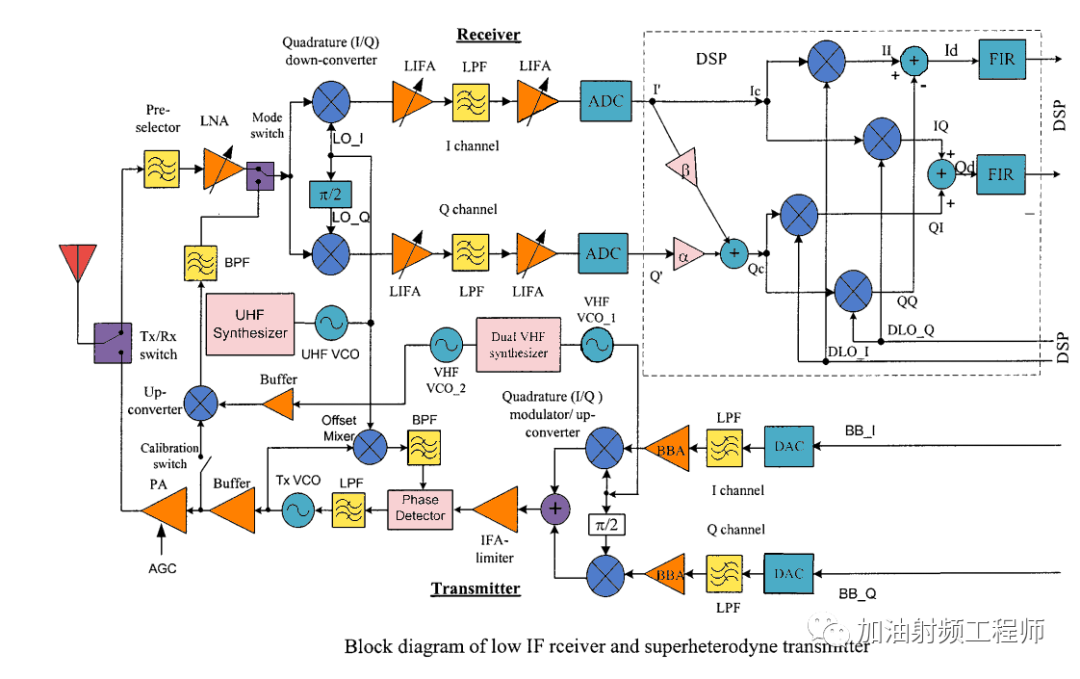

就如大家知道的這樣,接收機(jī)的架構(gòu),分為超外差,零中頻,低中頻和直接采樣。

2023-08-24 13:59:41 625

625

電子發(fā)燒友網(wǎng)站提供《高性能中頻采樣系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn).pdf》資料免費(fèi)下載

2023-10-18 09:57:34 0

0 中頻采樣是什么意思?中頻采樣與基帶采樣的區(qū)別? 中頻采樣與基帶采樣都是數(shù)字信號(hào)處理中常用的采樣技術(shù),它們的區(qū)別在于采樣信號(hào)的頻率不同。基帶采樣是指在信息原始頻域內(nèi)進(jìn)行采樣,而中頻采樣是指在信號(hào)已經(jīng)

2023-10-22 11:24:39 1146

1146 。而中頻采樣和IQ采樣是兩個(gè)在接收過程中常用的采樣方式。本文將詳細(xì)介紹什么是中頻采樣和IQ采樣,以及它們之間的比較和轉(zhuǎn)換。 一、什么是中頻采樣? 中頻采樣又稱IF采樣,是在無線電接收機(jī)中廣泛用于對(duì)接收信號(hào)進(jìn)行數(shù)字化處理的一種采樣

2023-10-22 11:24:42 2240

2240

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論