本文在說明全數字鎖相環的基礎上,提出了一種利用FPGA設計一階全數字鎖相環的方法,并給出了關鍵部件的RTL可綜合代碼,并結合本設計的一些仿真波形詳細描述了數字鎖相環的工作過程,最后對一些有關

2018-10-25 09:17:13 8237

8237 調制信號的符號速率達到500Mbps,根據奈奎斯特采樣定理,DA的采樣頻率采用2Gbps。

2023-09-22 15:28:11 1052

1052

Altera公司的QuartusⅡ環境下,用VHDL語言實現了8PSK全數字解調系統設計。最后在PCB板上利用Stratix Ⅱ芯片實現,并結合8PSK調制器進行功能驗證,得到滿意的結果。【關鍵詞】:PSK

2010-04-23 11:16:42

[/td][td] AD9789 IRQ管腳 上電拉不高,非正常工作狀態

手冊描述是:Active Low, Open-Drain Interrupt Request Output. Pull up

2023-11-27 06:27:08

采用AD9789,遇到以下問題,求大神解答!上電手動復位后,對芯片進行寫操作無響應,無論寫入什么數據,讀取狀態寄存器結果都是0xFF,示波器觀察SPI管腳時序無誤,上電后,不進行任何配置,從SDO

2018-11-14 11:02:18

Hi ADI,關于AD9789 Datashhet EN中關于基帶數字上變頻的輸出頻率為DC to Fdac/16(The digital upconverter enables each

2018-10-25 09:25:53

關于AD9789 Datashhet EN中關于基帶數字上變頻的輸出頻率為DC to Fdac/16(The digital upconverter enables each baseband

2023-12-21 07:56:11

Hi ADI我們的設計用到了FPGA和AD9789進行CMOS電平的數字通信。fpga的時鐘跟AD9789的時鐘是異步的,不知道這樣的設計會不會導致fpga和ad9789的通信不穩定,如何避免

2018-10-22 09:47:03

你好!在使用AD9789芯片的過程中,發現中文和英文數據手冊的P44頁有不對應的地方,16倍數字可調帶通濾波器公式中,中文數據手冊中最高中心頻率為Fdac/2,而英文數據手冊中最高中心頻率為Fdac,請問以哪個參考為準,謝謝!

2018-11-16 10:10:37

的頻譜,復制16份。這時并不存在Nyqusit區這一概念。 這個問題是我在看一個關于AD9789用于DVB-S的應用時想到的,文檔如附件。附件DVB_S射頻調制的FPGA 實現.pdf268.7 KB

2018-12-12 11:34:59

輸出數據不對,會丟包,當我將波特率設置到7.8M時是可以正常運行的,是否是AD9789的QAM編碼器對于輸出帶寬有限制呢?謝謝各位!

2023-12-21 06:05:45

請問各位,AD9789的QAM編碼器能不能工作在符號率為8MHz以上?謝謝!

2023-12-21 08:25:16

我們在項目中使用AD9789芯片過程中發現IRQ上電后輸出為低電平,寫入值到中斷使能寄存器0x03后再讀中斷狀態寄存器0x04,則0x04均返回為0,但讀寫其他寄存器正常。在和ADI購買的AD9789評估版上測試,上電后IRQ則為高電平,讀寫0x03和0x04則正常,想請專家幫解答一下,謝謝!

2018-10-09 16:21:26

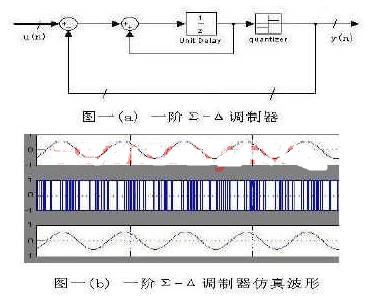

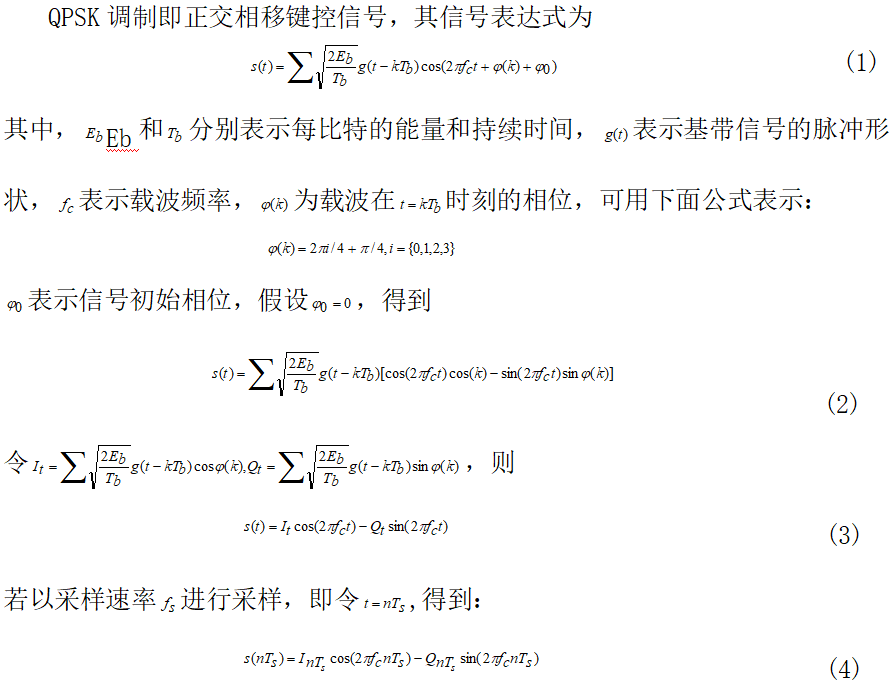

QPSK即正交相移調制。在看QPSK之前,先看一下通信系統的調制解調的過程為了方便分析,先假設這里是理想信道,沒有噪聲,接收端已經載波同步,位同步。調制后的信號數學模型為: 上述的x(t)被調制到了

2016-11-30 18:26:53

我們的設計用到了FPGA和AD9789進行CMOS電平的數字通信。fpga的時鐘跟AD9789的時鐘是異步的,不知道這樣的設計會不會導致fpga和ad9789的通信不穩定,如何避免。fpga和ad9789是如何同步的?通信速率fs=18.284MHz,fdac=2.395204GHz。謝謝!

2023-12-21 08:29:25

的發展方向。本課題著重研究高速調制解調器的全數字實現方法和基于FPGA的QAM系統設計、仿真和實現,首先簡要分析了QAM系統的基本原理和系統模型以及各個模塊的原理,提出了一種全數字調制解調器方案, 然后在

2021-07-27 06:38:51

的原理及實現,以OFDM寬帶數字調制解調系統為例進行說明,子載波采用QPSK調制,用預畸變的μ律變換進行了峰均比的降低。我已錄制成視頻,視頻及視頻中提到的代碼和資料下載地址如下(回復可見

2013-08-15 14:43:38

SoC面臨的挑戰是什么采用FPGA方案進行數字顯示系統設計有什么特性?

2021-04-29 06:24:26

就已經出現,隨著FPGA芯片價格的不斷降低,其在工業領域的應用正在飛速發展,采用FPGA來實現SVPWM調制算法也將層出不窮2. 系統任務分析及實現SVPWM調制算法相對比較復雜,在完成系統控制任務

2022-01-20 09:34:26

摘要:調幅是中短波廣播中一種主要的調制方式。本文針對現有的模擬短波AM解調器的不足,提出了一種基于FPGA的全數字解調器。其最大的優點是將系統中的模擬電路壓縮到最小。短波信號在前端經過模數轉換器采樣

2019-07-02 07:35:09

本文基于VHDL方式實現了QPSK數字調制解調電路的設計,通過QuartusII軟件建模對程序進行仿真,并通過引腳鎖定,下載到FPGA芯片EP1K30TC144—3中,軟件仿真和硬件驗證結果表明了該

2020-12-18 06:03:26

QPSK調制的基本原理QPSK調制電路的FPGA實現

2021-04-08 06:01:29

鎖相環是什么工作原理?如何采用FPGA與頻率綜合器ADF4111相結合的方法實現數字鎖相式頻率源的設計?

2021-04-14 07:00:20

全數字鎖相環由那幾部分組成?數字鎖相環的原理是什么?如何采用VHDL實現全數字鎖相環電路的設計?

2021-05-07 06:14:44

本文引入了dsPIC30F4012芯片,并介紹采用它與IPM模塊結合實現的全數字化SPWM變頻調速系統的構成及基本算法。系統主電路采用交直一交電壓型變頻方式,逆變電路采用三菱電機推出的第4代智能功率

2021-04-21 06:40:01

本文首先介紹了MQAM調制解調的基本原理,然后以64QAM為例,介紹了一種全數字實現的調制系統結構方案,并給出了解調器的具體FPGA實現方法及關鍵技術。

2021-04-30 06:46:14

本文將介紹線路調制的FPGA實現,包括:線路調制單元數字化實現的總體設計,CIC和FIR濾波器的FPGA實現以及載波發生器單元的設計。

2021-04-29 06:41:28

QPSK調制是什么?衡量QPSK調制質量的指標有哪些?QPSK調制是如何測量與凈化的?

2021-04-13 06:23:18

專家您好,請問, AD9789 可以透過設定哪個register and value,使其輸出sine wave? Thanks a lot.

2018-12-12 09:16:56

請問, AD9789 可以透過設定哪個register and value,使其輸出sine wave?

非常感謝。

2023-11-24 08:29:08

,AD9789在QDUC模式下,基帶數字上變頻輸出IQ信號(復信號)至16倍插值器和帶通濾波器,則相應的帶通濾波器輸出至RFDAC是實信號,我想了解的是芯片在此架構圖中如何實現復信號到實信號的轉換,(我

2023-12-21 07:32:06

,AD9789在QDUC模式下,基帶數字上變頻輸出IQ信號(復信號)至16倍插值器和帶通濾波器,則相應的帶通濾波器輸出至RFDAC是實信號,我想了解的是芯片在此架構圖中如何實現復信號到實信號的轉換,(我原來的理解

2018-12-12 11:34:07

大家好:

我在使用AD9789的時候遇到一個問題。

我是用STM32f系列的單片機對AD9789進行控制。

在程序初始化的時候,采用datasheet上的初始化順序可以對AD9789進行正確

2023-12-19 07:27:33

大家好:我在使用AD9789的時候遇到一個問題。我是用STM32f系列的單片機對AD9789進行控制。在程序初始化的時候,采用datasheet上的初始化順序可以對AD9789進行正確的配置。現在

2018-09-25 17:39:08

AD9788實現QPSK調制時所用載波是由FPGA提供的還是由AD9788本身提供的?

2018-11-15 09:19:30

1 AD9789的參考時鐘要求是差分鋒值電壓為1.8V,如下截圖2ADF4350的輸出功率范圍通過寄存器可以配置為-4dbm至5dbm, 3AD9789的參考設計中為AD9789增加了一個時鐘驅動

2018-10-22 09:47:27

Hi ALL,目前我在正在調試AD9789,使用的是AD9789內部的QDUC功能,如下圖:原理圖是參考官網設計的(芯片為AD9789 ADF4350 ADCLK914以及一個MCU)。現在

2018-12-11 09:22:51

Hi,請問有AD9789 flatness 相關的技術文件嗎?? We need the documents about AD9789 register setting and recomended

2019-03-05 13:01:32

誰有基于FPGA的數字調制器的程序啊,急用啊ASK,PSK,.FSK,QPSK等

2014-04-14 22:31:30

本文較系統地介紹了一類遠距離射頻卡讀寫器數字處理模塊的設計,特別在于采用單片CPLD實現了射頻卡讀寫器數字模塊功能,采用了原理圖和VHDL相結合自頂向下的設計方法,樣機PCB版面積小,開發周期短

2021-05-07 06:00:47

智能全數字鎖相環的設計

摘要: 在FPGA片內實現全數字

2008-08-14 22:12:51 56

56 數字調制解調技術在數字通信中占有非常重要的地位,數字通信技術與FPGA的結合是現代通信系統發展的一個必然趨勢。文中介紹了QPSK調制解調的原理,并基于FPGA實現了QPSK調制

2009-06-09 09:06:44 124

124 基于FPGA的全數字鎖相環設計:

2009-06-26 17:30:59 141

141 數字調制解調技術在數字通信中占有非常重要的地位,數字通信技術與FPGA的結合是現代通信系統發展的一個必然趨勢。文中介紹了QPSK調制解調的原理,并基于FPGA實現了QPSK調制解調

2009-07-22 15:42:25 0

0 GMSK(高斯最小移頻鍵控)信號優良的頻譜特性在跳頻通信中有廣闊的應用前景。本文分析了GMSK 調制器的設計理論,給出了一種全數字實現結構并在FPGA 上加以實現。仿真結果表明,

2009-08-13 14:48:05 56

56 根據軟件無線電的思想,用可編程器件FPGA 實現了QPSK 解調,采用帶通采樣技術對中頻為70MHz 的調制信號采樣,通過對采樣后的頻譜進行分析,用相干解調方案實現了全數字解調

2009-08-27 11:00:14 68

68 The AD9789 is a flexible QAM encoder/interpolator/upconverter combined with a high performance

2009-09-21 08:22:25 17

17 本文提出了一種QPSK 高性能數字調制器的FPGA 實現方案,由Altera 的IP 核NCO2.3.0 提供QPSK高穩定度的數字正弦信號,給出了QPSK 的實驗仿真結果。結果表明,基于NCO 的QPSK 數字調制器極大

2009-09-26 08:56:55 43

43 提出了一種基于FPGA 實現QPSK 調制器的方法。以FPGA 實現DDS,通過對DDS 信號輸出相位的控制實現調相。仿真結果表明方案是可行的。

2009-12-18 11:57:08 66

66 介紹一種全數字BPSK 解調器的設計及FPGA 實現。該解調器采用前向開環的結構實現載波同步,與傳統的閉環反饋結構相比,該解調器具有同步速度快,載波頻差估計范圍大等優點,

2009-12-19 15:57:36 52

52 論述了某航天器DS-SS接收機外部AGC的設計原理和具體實現,重點討論了如何根據射頻前端的輸出設計全數字AGC以擴展接收機的動態范圍,并給出了基于FPGA的外部AGC電路算法。計算機仿

2010-07-17 15:02:13 9

9 介紹一種全數字BPSK解調器的設計及FPGA實現。該解調器采用前向開環的結構實現載波同步,與傳統的閉環反饋結構相比,該解調器具有同步速度快,載波頻差估計范圍大等優點,尤其適合

2010-07-21 17:34:19 47

47 介紹了某直接序列擴頻、QPSK調制系統接收通道中四相Costas載波跟蹤環的原理及其基于DSP+FPGA的實現。著重論述了跟蹤環的鑒相特性和環路濾波器的設計和參數計算。

2010-08-04 11:43:35 0

0

QPSK調制器

本文深入淺出地向讀者介紹了QPSK調制解調器的工

2006-05-07 13:42:48 1614

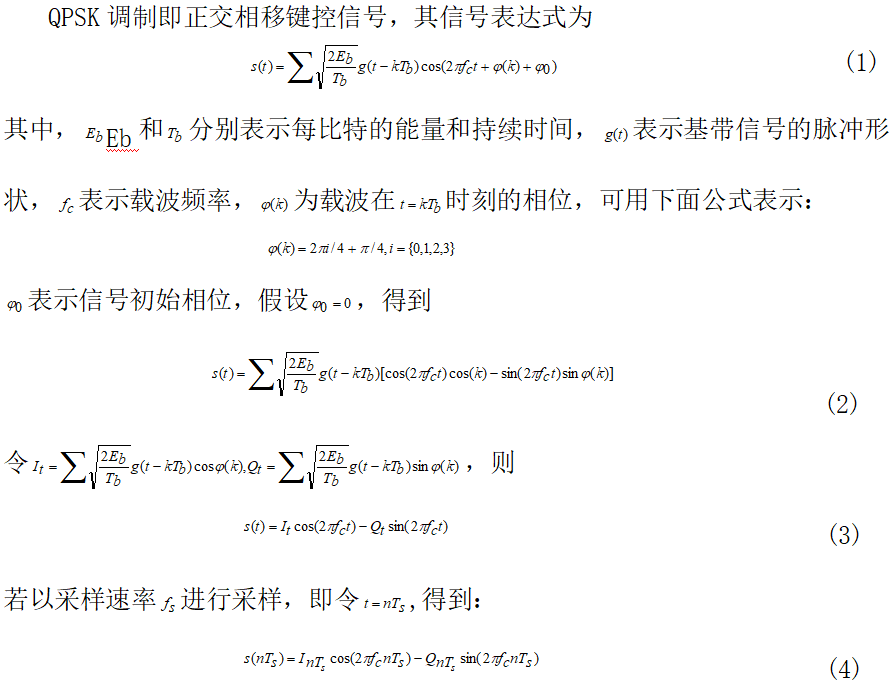

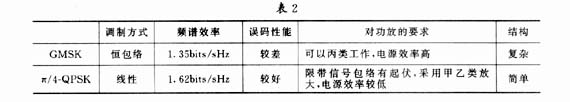

1614 【摘 要】 簡略介紹了QPSK,π/4-QPSK調制方法及基于此的π/4-DQPSK調制方法,就π/4-QPSK的調制電路原理與實現作了概述,并針對π/4-QPSK調制方法的優點及其性能與GMSK技術

2009-05-15 22:32:30 16257

16257

根據數字信號FSK調制和解調的工作原理,采用層次化、模塊化方法設計了一種基于FPGA 芯片的FSK調制解調器;用數字鍵控法實現了調制,用過零檢測法實現了全數字解調。同時結合系統

2011-08-26 15:25:48 114

114 針對全數字正交幅度(QAM)調制技術在數字微波通信系統中的應用,以64QAM為例提出了一種全數字實現的調制系統結構方案,基于Quartus II及Matlab軟件開發平臺,用原理圖和Verilog HDL語言相結

2011-09-20 15:16:23 92

92 該設計是基于System Generator設計平臺,在Matlab/Simulink環境下搭建系統模型,再進行功能仿真和驗證,完成QPSK調制器的設計。仿真結果表明,所設計的調制器能產生正確QPSK波形,達到了預期效果

2011-10-17 16:10:51 65

65 介紹了MSK信號的優點,并分析了其實現原理,提出一種MSK高性能數字調制器的FPGA實現方案;采用自頂向下的設計思想,將系統分成串/并變換器、差分編碼器、數控振蕩器、移相器、乘

2012-04-12 14:40:40 65

65 文中詳細介紹了QPSK技術的工作原理和QPSK調制、解調的系統設計方案,并通過VHDL語言編寫調制解調程序和QuartusII軟件建模對程序進行仿真,通過引腳鎖定,下載程序到FPGA芯片EP1K30TC144

2013-06-08 17:47:19 91

91 QPSK是數字通信系統中一種常用的多進制調制方式。其調制的基本原理:對輸入的二進制序列按每兩位碼元分為一組,用載波的四種相位表征它們。

2014-09-04 10:21:55 1901

1901

QPSK的調制解調的整個過程的講解和源代碼,之后會長傳在FPGA上的實現和調試

2016-12-12 21:36:19 71

71 基于FPGA的全數字FQPSK調制器實現_楊峰

2017-03-19 11:38:26 2

2 隨著FPGA技術的發展,數字通信技術與FPGA的結合體現了現代數字通信系統發展的一個趨勢。為了使高速通信系統更加緊湊、成本更低、減小功耗,特別是提高設備的可靠性,可采用Q P S K數字調制技術

2018-02-20 07:50:00 19252

19252

采用FPGA設計芯片技術對多進制數字通信技術的QPSK調制器實現進行了設計研究,將調制器中原有多種專用芯片的功能集成在一片大規模可編程邏輯器件FPGA芯片上,實現了高度集成化,小型化。實際研究仿真表明,該方案具有突出的靈活性和高效性,為設計者提供了多種可自由選擇的設計方法和工具.

2020-07-22 17:51:13 15

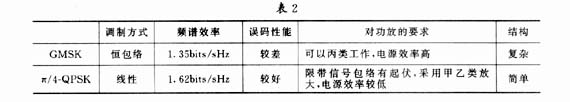

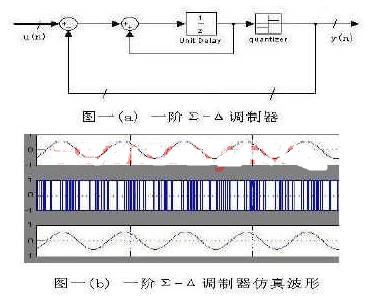

15 Σ-Δ調制在數字信號處理以及通信系統方面的應用正越來越引起大家的重視,因為Σ-Δ調制實現時主要采用數字技術而且對模擬端的精度要求不高,Σ-Δ調制通常都是對模擬信號進行調制產生一位數字信號。但很多情況下,輸入信號本身就是數字信號,這時就非常有必要研究對數字信號的Σ-Δ調制實現方式。

2020-07-31 17:52:09 4939

4939

近年來,數字AM調制技術應用越來越廣泛,具體應用中多采用專用的調制芯片完成。文中介紹一種在FPGA中實現數字AM調制的方法,采用該方法設計的系統具有使用靈活、擴展性強、便于集成等優點。文中先討

2020-07-31 17:50:22 19

19 本文提出了一種適用范圍廣泛的全數字鎖相環(ADPLL)實現方法.在鎖相環輸入頻率未知的情況下,實現鎖相鎖頻功能。本文從全數字鎖相環的基本實現方式入手.進行改進,并使用VH DL語言建模,使用FPGA進行驗證。

2021-01-26 15:03:00 65

65 本文提出了一種適用范圍廣泛的全數字鎖相環(ADPLL)實現方法.在鎖相環輸入頻率未知的情況下,實現鎖相鎖頻功能。本文從全數字鎖相環的基本實現方式入手.進行改進,并使用VH DL語言建模,使用FPGA進行驗證。

2021-01-26 15:03:00 18

18 AD9789:14位、2400 MSPS RF DAC,具備4通道信號處理能力 數據手冊

2021-03-19 06:43:52 4

4 針對高速率QPSK數據傳輸鏈系統,比較分析了數字中頻接收與零中頻接收的優、缺點,并提出了一種基于多相濾波的寬帶中頻正交采樣數字零中頻接收方案。基于FPGA對此數字零中頻正交變換方案進行了實現和驗證,同時,對一種全數字零中頻QPSK信號的高速解調算法及其FPGA硬件實現進行了介紹。

2021-03-19 17:43:12 11

11 AD9789 IBIS型號

2021-04-12 17:04:19 2

2 AD9789評估板、DAC-FMC轉接器和Xilinx ML605參考設計

2021-05-20 13:26:26 8

8 基于軟件無線電QPSK調制解調實現的研究畢業設計免費下載。

2021-05-28 14:24:12 35

35 基于FPGA的高性能全數字鎖相環

2021-06-08 11:09:01 45

45 AD9789 IBIS型號

2021-06-17 09:40:23 4

4 進行了實現和驗證,

同時,對一種全數字零中頻 QPSK 信號的高速解調算法及其 FPGA 硬件實現進行了介紹。

2022-12-12 15:44:36 3

3 本文深入淺出地向讀者介紹了QPSK調制解調器的工作原理。從模擬通信到數字通信的轉變加速了QPSK技術的應用。本文用歐拉公式輔助分析正弦和余弦的乘積,并通過SPICE仿真給出了一個1MHz正弦波

2023-06-09 14:21:57 707

707

簡介:論述了一種運行在FPGA芯片上應用于B超的全數字波束形成技術。采用孔徑變跡、幅度加權變跡和動態變跡相結合的綜合變跡技術和動態聚焦技術,兩種技術均形成直觀的數學模型,在FPGA上的實現方法類似

2023-11-09 08:31:41 0

0

電子發燒友App

電子發燒友App

評論