Digilent為Arty FPGA開發(fā)板系列增加了新的成員——兩種不同規(guī)格的新的Arty S7,這款FPGA開發(fā)板是基于中等大小(size)的Xilinx Spartan-7 FPGA系列芯片而開發(fā)的

2017-09-27 06:33:00 8255

8255

FPGA開發(fā),如何從Flash啟動嵌入式系統(tǒng)?我們手把手教你。

2017-12-24 10:22:28 11338

11338 比特流是一個常用詞匯,用于描述包含F(xiàn)PGA完整內(nèi)部配置狀態(tài)的文件,包括布線、邏輯資源和IO設(shè)置。大多數(shù)現(xiàn)代FPGA都是基于SRAM的,包括Xilinx Spartan 和Virtex 系列

2022-11-30 10:59:17 733

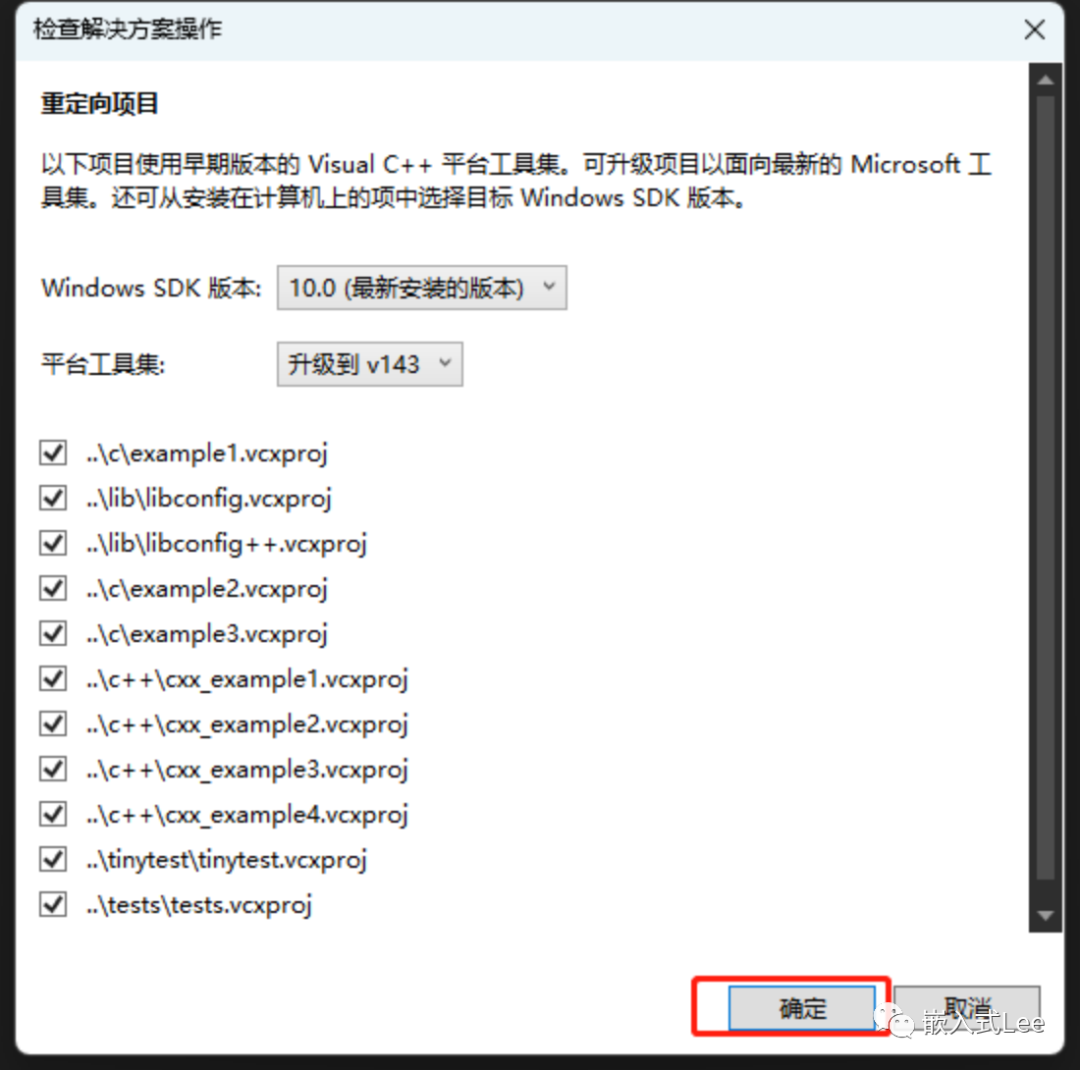

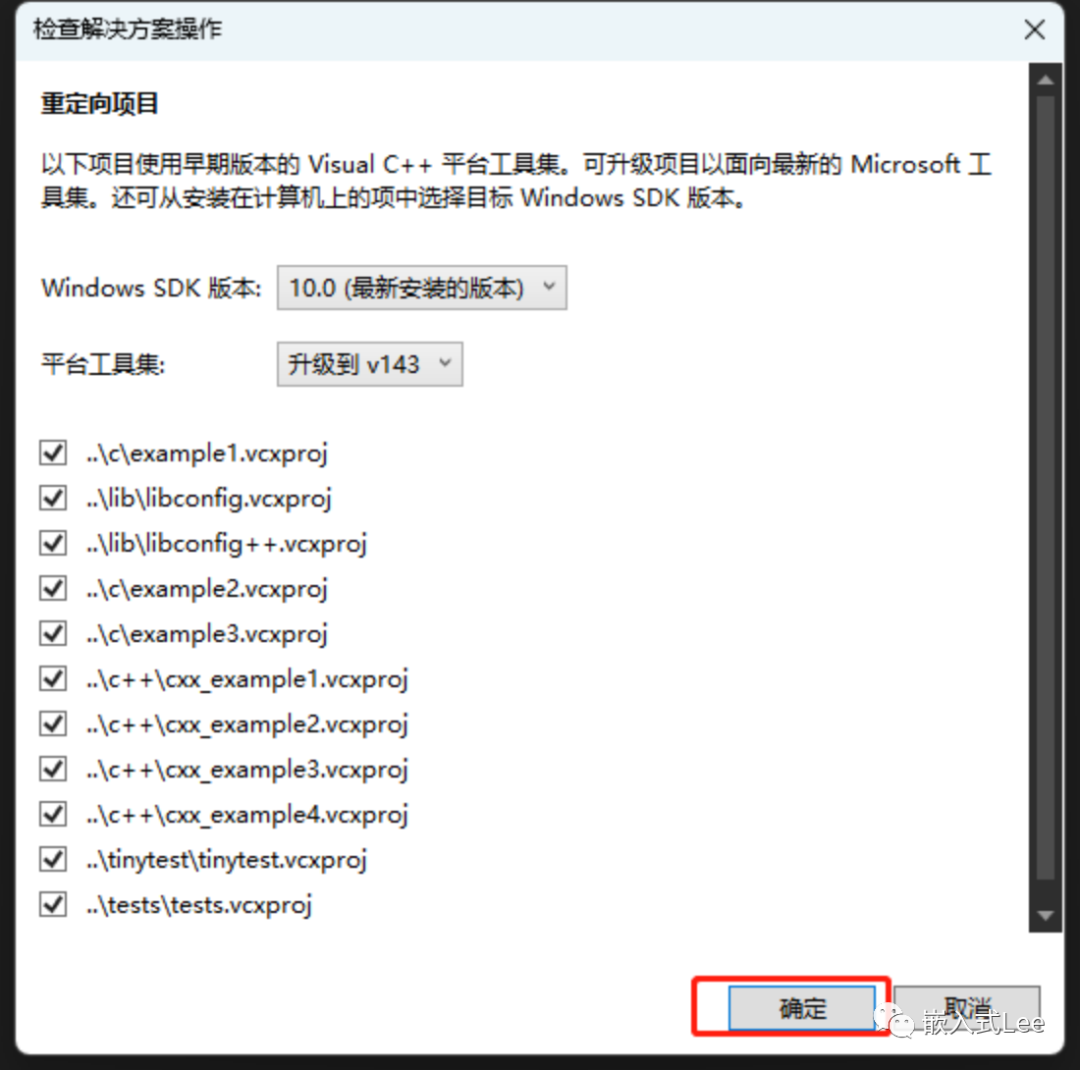

733 本文介紹基于libconfig進(jìn)行配置文件解析

2023-06-08 10:18:06 738

738

一、學(xué)習(xí)計(jì)劃計(jì)劃item時間備注資料搜集2020-03-08無二、資料搜集資料備注普中科技-雙核-A7開發(fā)板_嗶哩嗶哩 (゜-゜)つロ 干杯~-bilibiliB站 A7型板子視頻 非常詳細(xì)普中科

2021-07-21 07:10:11

使用與以前相同的程序在Arty板上調(diào)試稍微不同的程序,但沒有成功......將比特流編程到FPGA時收到的消息:警告:[Labtools 27-3123]在用戶掃描鏈1或3處未檢測到調(diào)試集線器核心。解決方案

2020-08-26 15:20:18

移植蜂鳥內(nèi)核的arty A7 35T 開發(fā)板在執(zhí)行GPIO中斷函數(shù)的時候總是會連續(xù)進(jìn)入兩次中斷。

2023-08-16 07:30:20

用的arty A7 35T開發(fā)板,移植的蜂鳥內(nèi)核,調(diào)試器用的ARM-USB-TINY-H,使用IDE下載程序時,出現(xiàn)下面的情況:

但是最后是這樣的:

想問一下這樣有沒有下載成功

2023-08-16 08:04:27

`請問比特流是什么?`

2019-08-23 16:24:40

寫了一個數(shù)據(jù)庫連接配置文件,但是其中某些內(nèi)容需要進(jìn)行加密存儲,比如用戶密碼等,不知道該怎么實(shí)現(xiàn),求大神指點(diǎn)!!

2013-10-10 20:36:18

開發(fā)板支持調(diào)試功能。

給AliOS Things一顆STAR(前往GitHub關(guān)注我們)

目錄簡介AliOS Studio調(diào)試機(jī)制準(zhǔn)備工作編寫配置文件debug配置文件說明配置文件參數(shù)說明啟動調(diào)試

2019-10-17 10:11:11

大家好,如果我將CyPress提供的默認(rèn)配置文件(當(dāng)我安裝了驅(qū)動程序)從目錄C:CyPress \ USB \ CY4605-HX2LP \ 1 \軟件\CONTIOFFILE \2A

2019-05-24 10:06:18

;supportDimensions\": [

\"2*2\"

]

}

]

}

*附件:HarmonyOSOpenHarmony元服務(wù)開發(fā)-配置卡片的配置文件.docx

2023-08-01 11:45:01

簡介應(yīng)用的每個HAP的根目錄下都存在一個“config.json”配置文件,主要涵蓋以下三個方面:應(yīng)用的全局配置信息,包含應(yīng)用的包名、生產(chǎn)廠商、版本號等基本信息。應(yīng)用在具體設(shè)備上的配置信息。HAP包

2020-09-18 14:04:47

1.使用nfs進(jìn)行網(wǎng)絡(luò)掛載①開發(fā)板必須要和虛擬機(jī)、電腦在同一個網(wǎng)段內(nèi)(相互可以ping通)②將要下載到開發(fā)板的程序放到指定目錄,這個目錄需要在ubuntu環(huán)境的配置文件/etc/exports中指

2019-09-29 08:49:59

N32G430C8L7_STB開發(fā)板用于32位MCU N32G430C8L7的開發(fā)

2023-03-31 12:05:12

了問題,我不得不重新刷板。我的問題有兩個,我將不勝感激任何建議(1) 如何在板載 LCD 屏幕上打開 Linux shell 而不是使用 STLink 將其映射到我的計(jì)算機(jī)(2) 如何自動啟動A7 應(yīng)用程序和M4 固件并禁用演示。

2022-12-28 06:40:58

(xczu7eg-ffvf1517-1-e),代碼實(shí)現(xiàn)并正確生成比特流。然而,當(dāng)我使用Xilinx平臺電纜II通過JTAG配置帶有比特流的設(shè)備時,我得到錯誤Labtools 27-3303。 (分配給設(shè)備的比特流不正確

2020-06-09 14:24:42

大家好,我正在與SoC邁出第一步,我目前正在使用Zybo Zynq開發(fā)板。我有一個簡單的問題:是否可以創(chuàng)建多個設(shè)備配置,為每個配置生成比特流并將比特流存儲在內(nèi)存或其他內(nèi)容中,以便創(chuàng)建一個說“配置庫

2020-05-20 10:44:19

都還離不開ISE,除非,ISE不支持該芯片(比如A7最小的那幾塊)。 (3)用vivado集成環(huán)境內(nèi)的硬件會話(hardware session)下載比特流時斷開板子再連接, hw_server就會連接不上, 卡頓在那,必須退出vivado, 在任務(wù)管理器結(jié)束hw_server才行。

2015-07-08 17:35:03

”可執(zhí)行文件通過SSH拷貝到飛凌RZ/G2L開發(fā)板,然后修改文件權(quán)限。執(zhí)行測試程序test_01,可以看到屏幕出現(xiàn)圖標(biāo)按鈕。//------END

2022-09-06 20:17:50

嗨,我正在嘗試部分自我重新配置。想法是通過介質(zhì)將部分比特流發(fā)送到FPGA。FPGA接收它(在多個塊中)并將比特流寫入ICAP。當(dāng)連接發(fā)生時,我的FPGA的行為會發(fā)生什么發(fā)送部分比特流中途消失了?我

2019-02-14 09:40:06

你好 ,我們使用ise 14.2生成.mcs文件,但該文件無法編程為a7。有什么問題 ? Vivado必須用于a7嗎?

2020-03-06 10:09:30

我有一個設(shè)計(jì)有多個相同的SDA-6設(shè)備的電路板,它連接在一個串行菊花鏈中(共8個)。第一個配置為主串行模式,另一個配置為從串行模式。主設(shè)備連接到單個64Mb SPI設(shè)備進(jìn)行配置。我的應(yīng)用程序使用完

2019-06-21 12:05:52

BootloadDead應(yīng)用程序中,我可以用一個配置文件只使用BLE組件,然后在引導(dǎo)加載時將它轉(zhuǎn)換到Bootloader版本中。 以上來自于百度翻譯 以下為原文I have a fixed stack

2018-11-05 16:35:47

大家好,我在artix7上使用ICAP進(jìn)行部分比特流編程時遇到問題。我有一個靜態(tài)和部分比特流,當(dāng)用jtag編程時工作正常,所以比特流似乎沒問題。我可以通過icap觸發(fā)Multiboot,所以我假設(shè)

2020-08-06 09:15:36

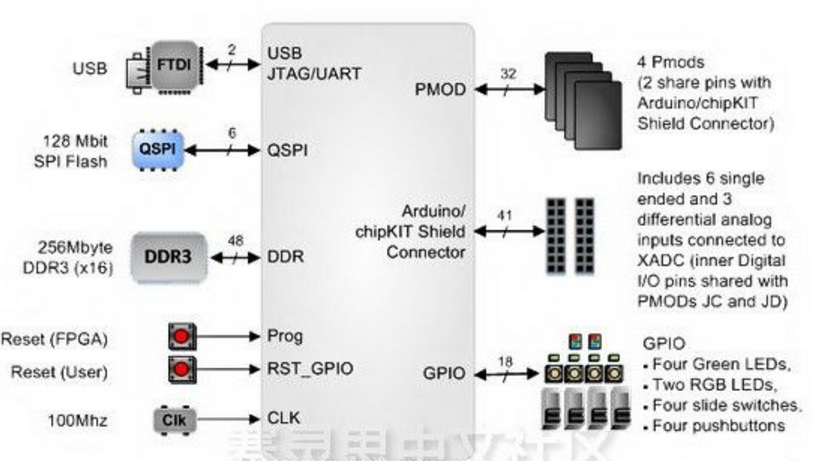

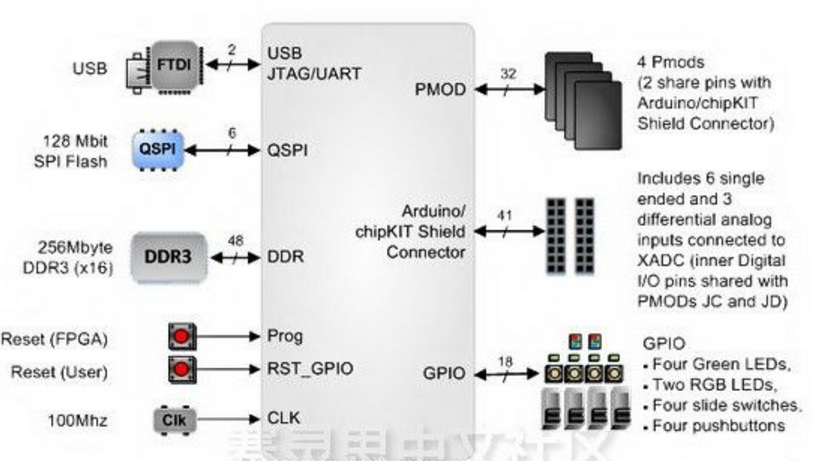

arty a7是基于Artix-7 FPGA設(shè)計(jì)的開發(fā)平臺,具有豐富的Pmod接口,擴(kuò)展性較強(qiáng),搭建microblaze軟核易于開發(fā)Arty A7開發(fā)板基本外設(shè):LED燈、UART串口、KEY按鍵

2022-01-18 08:09:43

我正在開發(fā)一個具有大型遠(yuǎn)程可升級比特流和慢速閃存寫入速度的項(xiàng)目。這些比特流使用普通文件壓縮(pkzip,gzip等)傳送。我想將更新的比特流以壓縮格式存儲在閃存上,并使用多引導(dǎo)方法引導(dǎo)它們

2020-05-29 17:12:21

大家好,我想使用USR_ACCESS_VIRTEX4原語來訪問存儲在配置閃存中的其他比特流。情況如下:我有一個主FPGA(Virtex-4FX)和一個從FPGA(Spartan-3A)。從屬FPGA

2020-05-29 10:14:55

for Partial Region 1& 2和Mul用于部分區(qū)域1&所以我將總共有7個比特流(1個全比特流,6個部分比特流)。目前我如何生成比特流是我為9個配置中的每一個做

2020-05-05 09:42:44

的筆記本電腦我想將一些比特流文件發(fā)送到NEXYS 4 Board中的Artix-7 Xilinx FPGA,然后使用這個比特流數(shù)據(jù)存儲閃光燈。我已經(jīng)為這塊板提供了Pmod Wifi模塊。可以與我的筆記本電腦

2020-04-30 07:46:17

我想利用A7開發(fā)板上的PMOD接口JB JC來實(shí)現(xiàn)攝像頭的圖像采集,想問一下大家具體的實(shí)現(xiàn)方法,比如攝像頭接口的編寫,怎么掛到AXI總線協(xié)議上以及如何使用

2023-08-16 07:13:29

我正在研究Zedboard,我需要將FPGA配置文件(.mcs文件)存儲到Flash上??。Zedboard在JTAG模式下工作正常。但是,如果我選擇加載文件的flash方法,F(xiàn)PGA_done

2020-05-20 10:31:51

這個問題對于了解開發(fā)流程的人來說,就太幼稚了,但是對于第一次編寫應(yīng)用程序,并且想要在開發(fā)板上運(yùn)行的人來講,可能就有點(diǎn)小懵逼了。 當(dāng)應(yīng)用程序編好以后,首先需要想辦法把應(yīng)用程序搬遷到開發(fā)板上,目前比較

2021-12-14 07:26:25

嗨,我只需要一個簡單的通訊模塊。我只是想讓我的模塊用AM中斷來喚醒,然后把它的設(shè)備ID發(fā)送給另一個模塊。我搜索了定義的配置文件,但是它們都是在某些應(yīng)用程序中指定的。你建議我怎么做?它必須只發(fā)送它的設(shè)備ID,有沒有定義的配置文件簡單地做了那項(xiàng)工作?

2019-09-25 08:56:40

學(xué)習(xí)普中A7開發(fā)板心得(一)關(guān)于LED實(shí)驗(yàn)的總結(jié)在開發(fā)板中關(guān)于LED的實(shí)驗(yàn)中,最值得注意的是在開發(fā)過程中,出現(xiàn)了按鍵的使用,在使用獨(dú)立按鍵時,我們需要注意的是,按鍵的抖動消除。延時函數(shù)的學(xué)習(xí)編寫

2022-01-06 07:40:39

將新的比特流圖像寫入SPI附加存儲器的過程是什么。理想情況下,圖像不應(yīng)位于@ 0x0000000并且正在替換圖像。我在U470中看到提到配置存儲器讀取過程是否存在配置存儲器寫入過程?該文件涉及FAR

2020-06-01 13:57:36

你好,這是一個思維設(shè)計(jì),而不是我正在積極努力的東西,但是:我想分析一下比特流。比特流包含在時鐘脈沖或兩個時鐘脈沖之間對齊的脈沖。沒有明確的時鐘信號,但我知道粗略的時鐘速度,并且在比特流中嵌入同步序列

2018-12-17 16:35:26

所有:由于缺少DMS respin的源文件,我很高興不得不重用遺留部分。我所擁有的只是一個最初存儲在XC1701部件上的比特流。我們相信我們已經(jīng)使用板外編程器成功地將此流編程到Micron

2020-05-29 11:06:25

ifourunderstanding不正確,并希望得到任何幫助和建議:1.我們將使用ISE Webpack生成比特流。2.然后我們將生成一個新文件,由SPI閃存使用,包含上一步中獲得的比特流。3.現(xiàn)在我們將使

2019-07-04 08:13:32

你好我有一個在MIcroBlaze上運(yùn)行l(wèi)inux的設(shè)計(jì)要求。我能夠在我的Virtex-7 FPGA上下載比特流(在Vivado 2014.4中生成)。我使用Impact來編程我的FPGA。我因此

2020-04-02 10:05:40

嗨,我有一個應(yīng)用程序,我希望在下載到FPGA之前使用類似于data2mem的工具來在FPGA比特流中破解塊內(nèi)存內(nèi)容。FPGA可以是Virtex 6或Artix 7或Kintex 7。比特流未加密且未

2019-03-19 12:44:14

嗨,我有幾塊帶有Spartan 3器件的電路板,并希望將相同的比特流加載到所有電路板中。我應(yīng)該選擇哪個端口在電路板和設(shè)備上使用?是否可以在JTAG配置模式下進(jìn)行配置?謝謝。阿卜杜拉以上來自于谷歌翻譯

2019-01-10 11:15:42

'hdcp@2015.09'未經(jīng)許可.IPCP功能在IP GUI上也不可用(灰顯)。忽略此嚴(yán)重警告后,我們能夠生成,合成,放置和路由知識產(chǎn)權(quán)。但無法生成比特流。錯誤是:[Common 17-69]命令失敗:此

2019-01-03 11:06:05

你好,我使用Vivado 2017.4;當(dāng)我運(yùn)行Synthesis和Implementation時,一切似乎都可以。但是,當(dāng)我想生成比特流文件時,沒有任何錯誤消息發(fā)生。.runs / impl_l

2018-11-09 11:37:53

嗨,我正在使用斯巴達(dá)3an,并想知道是否可以將配置文件存儲在ISF中并在外部spi flash中啟動用戶應(yīng)用程序代碼?在啟動時,我希望FPGA在ISF中運(yùn)行一個小型引導(dǎo)加載程序,并在外部spi

2019-05-29 13:50:06

嗨專家, 我正在使用spartan-6 FPGA進(jìn)行多重啟動實(shí)驗(yàn)。我發(fā)現(xiàn)位文件位于ug380上,如下圖所示。黃金比特流位于閃存的下部塊上,多重引導(dǎo)比特流位于閃存的較高塊上。 因此,如果我想使用保護(hù)區(qū)

2020-06-09 17:43:26

來自EMI12.4和13.3的比特流文件中的重要區(qū)別是什么?我從開始文件tosequence 0xF,交換和loadind到FPGA切換字節(jié)。來自12.4boot的比特流確定,但不是來自13.3。誰能幫我?

2020-06-12 14:04:57

大家好,當(dāng)我嘗試在本教程中生成比特流時:http://blog.idv-tech.com/2014/05/18

2018-10-24 15:31:25

你好,我們正在開發(fā)一個新的BLE產(chǎn)品使用自定義配置文件。該設(shè)備將具有自定義應(yīng)用程序,因此不需要使用標(biāo)準(zhǔn)配置文件,也避免了對認(rèn)證的需要。該設(shè)備完成,并使用自定義配置文件完美地工作,但我們現(xiàn)在要添加電池

2019-10-17 10:26:18

你好我用vertex6購買評估板我下載ISE 12.1,安裝完整版,進(jìn)行30天評估,獲得許可。但是,當(dāng)我在XPS中生成比特流時,我得到:信息:安全性:65- 您的“ISE”許可僅供試用:安全:69-

2018-11-27 14:36:14

我去年買ZLG的2100開發(fā)板(LPC2119),在映射文件鏈接ADS設(shè)置中采取的是scattered配置文件的方式,在《ARM體系結(jié)構(gòu)與編程》中介紹到對于簡單的文件可以采取使用命令行的方式,我在

2011-09-20 10:25:41

你好!xc7a35t和xc7a50t設(shè)備的實(shí)際比特流大小是多少?在UG470 v1.7(在vivado 2014.1文檔導(dǎo)航器中標(biāo)記為“最新”)中,只有標(biāo)記為“初步估計(jì)”的數(shù)字。這些設(shè)備現(xiàn)在似乎幾乎完全支持,可能已經(jīng)有最終數(shù)字了嗎?

2020-07-24 06:17:10

匹配的。當(dāng)我想要創(chuàng)建配置文件時write_cfgmem -format MCS -size 512 -interface bpix16 -loadbit“up 0x0 / C:/Users

2020-06-05 09:12:25

有沒有辦法改變比特流文件位于Vivado(2016.1)內(nèi)的位置?我知道我可以在Tcl控制臺上輸入tcl命令“write_bitstream”(https://forums.xilinx.com

2020-05-12 09:23:20

的模塊。之后,我可以執(zhí)行實(shí)現(xiàn)和位生成,該工具將創(chuàng)建完整和部分比特流。通過這種方式,我將得到4個比特流,兩個部分(每個可重新配置模塊一個比特流 - 讓我們稱之為BIT_A)和兩個完整(一個比特流,左移

2020-06-04 08:52:24

接口配置和先進(jìn)豐富的多媒體資源,方便客戶應(yīng)用程序開發(fā)。 開發(fā)板支持2路千兆以太網(wǎng)、2路CAN-FD、4路UART、4G、5G、雙頻WiFi、PCIe3.0、USB3

2021-08-20 14:00:36

HD-IMX6ULL-MB高性價比開發(fā)板產(chǎn)品介紹 HD-IMX6ULL-MB高性價比開發(fā)板基于HD-IMX6ULL核心板設(shè)計(jì)開發(fā),核心板默認(rèn)集成工業(yè)級處理器、512MB內(nèi)存、8GB存儲

2021-11-04 10:45:30

樹莓派RPi分辨率配置文件,從800*600到1920*1440,任你選擇

2015-11-30 11:13:07 9

9 , Digilentinc 針對這個問題有提供關(guān)于 Zybo Board 的配置文件,就讓我們來搞定他吧。 關(guān)于 Zybo Board 的配置文件可以在 Digilentinc 的 GitHub 上找到

2017-02-08 01:15:37 363

363 Zynq開發(fā)板FPGA比特流文件可以通過三種途徑下載: 1. 利用SDK生成的FSBL.elf文件自動加載FPGA比特流配置文件,將比特流文件,F(xiàn)SBL.elf文件和u-boot.elf文件利用

2017-02-08 15:20:09 895

895 開發(fā)板時,只會將FPGA配置文件(.bit)直接通過JTAG口下載到芯片里。后來編寫的程序大了,如果將程序直接放到內(nèi)部的

2018-02-27 15:33:29 5

5 配置文件配置文件是利用SCL語言描述變電站設(shè)備對象模型后生成的文件,用于在不同廠商的配置工具之間交換配置信息。

2018-06-02 11:16:13 16410

16410

了解如何使用Vivado Device Programmer創(chuàng)建和配置配置存儲設(shè)備。

首先,我們將學(xué)習(xí)如何設(shè)置正確的比特流屬性并生成配置存儲器文件。

2018-11-22 07:11:00 7095

7095 。客戶也可參考此方法,在自己的整機(jī)生產(chǎn)中實(shí)現(xiàn)應(yīng)用程序及配置文件的自動拷貝。本文以下介紹在CE平臺實(shí)現(xiàn)應(yīng)用程序及配置文件自動拷貝的具體步驟。 英創(chuàng)主板處于調(diào)試模式啟動時,會查詢系統(tǒng)的usbdisk根目錄下是否有名為autotest.tx

2020-02-07 11:03:14 874

874

本文檔的主要內(nèi)容詳細(xì)介紹的是Keil的黑色界面配置文件和配置方法。

2019-12-03 15:05:00 26

26 FreeRTOS_006_FreeRTOSConfig.h配置文件(三)

2020-03-14 11:10:09 3093

3093

FreeRTOS_004_FreeRTOSConfig.h配置文件(一)

2020-03-14 11:18:08 2394

2394

本文檔的主要內(nèi)容詳細(xì)介紹的是Python進(jìn)行配置文件的教程免費(fèi)下載。

2020-09-30 16:41:10 6

6 AD8283評估板設(shè)計(jì)和配置文件

2021-05-31 16:04:46 9

9 labview讀寫配置文件實(shí)例分享

2021-11-01 16:05:12 40

40 上期講述了AMetal平臺驅(qū)動框架中的硬件層,介紹了硬件層的驅(qū)動是如何實(shí)現(xiàn)及其硬件層接口的定義,逐漸深入了解AMetal平臺。接下來向大家介紹配置文件和例程文件的使用,以此可靈活使用相應(yīng)外設(shè)的資源。

2022-04-07 11:49:04 1635

1635

Map配置 YML配置文件: sys-num: mymap: "{'a':'aaa','b':'bbb'}" 方法內(nèi): public class learnMap { @Value

2023-01-13 15:28:53 404

404 Map配置 YML配置文件: sys-num: mymap: "{'a':'aaa','b':'bbb'}" 方法內(nèi): public class learnMap { @Value

2023-01-13 15:36:37 467

467 教程 2:自定義配置文件示例

2023-03-13 19:33:00 0

0 教程 3:構(gòu)建自定義配置文件

2023-03-15 19:39:12 0

0 現(xiàn)在配置對象已經(jīng)是單例了,但還有一個問題,它的每個配置項(xiàng)的值都是默認(rèn)值,我們當(dāng)然是希望它在創(chuàng)建對象的時候是使用配置文件中的值啦。下面看需求三怎么實(shí)現(xiàn)。

2023-05-04 10:00:45 453

453 教程 2:自定義配置文件示例

2023-07-04 20:50:27 0

0 教程 3:構(gòu)建自定義配置文件

2023-07-06 18:49:28 0

0 KT142C語音芯片配置文件總是不起作用?配置文件的問題集中歸納

2023-10-20 15:04:15 243

243

Linux是一種開源的操作系統(tǒng),因此,它給用戶提供了很高的自由度,可以根據(jù)個人需要進(jìn)行各種定制和配置。其中,修改網(wǎng)絡(luò)接口配置文件是常見的操作,可以通過修改網(wǎng)卡ip配置文件來設(shè)置網(wǎng)絡(luò)接口的IP地址

2023-11-17 10:51:27 1008

1008 Spring Boot是一種快速開發(fā)框架,其通過提供配置文件來實(shí)現(xiàn)對應(yīng)用程序的配置。全局配置文件在Spring Boot中起著非常重要的作用,可以用于配置各種不同的屬性,包括數(shù)據(jù)庫連接、日志級別

2023-12-03 15:28:21 390

390 人員的工作量。 Spring Boot的核心配置文件主要有以下幾個: application.properties:Spring Boot應(yīng)用程序的主要配置文件。它使用Java的鍵值對格式來定義各種配置屬性

2023-12-03 15:30:47 446

446 PHP的配置文件是一種用于配置PHP解釋器的文本文件。它包含了一系列的指令和選項(xiàng),用于影響PHP的行為和性能。通過修改配置文件,可以改變PHP解釋器的默認(rèn)行為,從而滿足不同的需求。 在PHP

2023-12-04 15:55:53 662

662 Oracle配置文件tnsnames.ora是一個文本文件,用于定義數(shù)據(jù)庫連接的別名和連接信息。通過配置該文件,可以在應(yīng)用程序中使用別名來連接數(shù)據(jù)庫,而不必直接給出數(shù)據(jù)庫的具體連接信息。以下是關(guān)于

2023-12-06 10:15:55 1050

1050 接下來我們下載兩塊開發(fā)板的測試程序,先在5CEFA7F23的下載器內(nèi)添加比特流文件,輸入翻轉(zhuǎn)率50%比特流文件并且加載。

2023-12-15 11:41:00 239

239

可執(zhí)行文件之前,您需要確保正確配置文件,以便應(yīng)用程序能夠在不同計(jì)算機(jī)上正確運(yùn)行。 下面是一個詳盡、詳實(shí)、細(xì)致的步驟指南,告訴您如何配置LabVIEW生成的可執(zhí)行文件: 確保您的應(yīng)用程序在LabVIEW中正確運(yùn)行:在生成可執(zhí)行文件之前,您需要先在LabVIEW開發(fā)環(huán)境中驗(yàn)證

2023-12-27 16:28:35 433

433

電子發(fā)燒友App

電子發(fā)燒友App

評論