FPGA的開發(fā)流程是遵循著ASIC的開發(fā)流程發(fā)展的,發(fā)展到目前為止,F(xiàn)PGA的開發(fā)流程總體按照圖1進行,有些步驟可能由于其在當前項目中的條件的寬度的允許,可以免去。

2023-01-06 11:19:28 1403

1403 我已獲得SDSoC的試用許可證并將其加載到許可證管理器中;它說“裝載成功”。然后我啟動SDSoC并彈出一條錯誤消息,請參閱附件。然后我再次加載它(許可證管理器說一切都很好),然后再次啟動SDSoC

2019-01-02 14:39:44

使用C/C+在硬件實現(xiàn)加速OpenCV功能,并在SDSoC開發(fā)環(huán)境中實現(xiàn)硬件優(yōu)化庫

2019-01-04 13:30:14

PCF8591是什么?PCF8591主要的功能特性有哪些呢?A/D轉換的應用開發(fā)流程是怎樣的呢?

2022-01-20 06:55:26

Linux的常用命令該怎樣去使用呢?ARM Cortex-A9的具體開發(fā)流程有哪些?ARM Cortex-A9的開發(fā)流程與51的有什么不同?

2021-11-12 07:53:35

FPGA設計工具視點是什么DSP設計流程有哪幾個步驟?

2021-04-30 06:56:24

哪位大神可以發(fā)一個FPGA開發(fā)流程的文檔,用實例演示的,包括行為,功能和時序分析的,萬分感謝!

2014-05-14 10:34:40

如圖1.6所示。這個流程圖是一個相對比較高等級的FPGA開發(fā)流程,從項目的提上議程開始,設計者需要進行FPGA功能的需求分析,然后進行模塊的劃分,比較復雜和龐大的設計,則會通過模塊劃分把工作交給一個

2019-01-28 04:24:37

在第一章中,已經(jīng)給出了FPGA/CPLD的基本開發(fā)流程圖。這里不妨回顧一下,如圖5.15所示。這個流程圖是一個相對比較高等級的FPGA/CPLD器件開發(fā)流程,從項目的提上議程開始,設計者需要進行

2015-03-03 14:31:44

FPGA入門:基本開發(fā)流程概述 在第一章中,已經(jīng)給出了FPGA/CPLD的基本開發(fā)流程圖。這里不妨回顧一下,如圖5.15所示。這個流程圖是一個相對比較高等級的FPGA/CPLD器件開發(fā)流程,從項目

2019-01-28 02:29:05

、板級仿真以及芯片編程與調試等主要步驟。圖1-10 FPGA開發(fā)的一般流程1.電路功能設計在系統(tǒng)設計之前,首先要進行的是方案論證、系統(tǒng)設計和FPGA芯片選擇等準備工作。系統(tǒng)工程師根據(jù)任務要求,如系...

2021-07-23 09:12:07

如圖1.6所示。這個流程圖是一個相對比較高等級的FPGA開發(fā)流程,從項目的提上議程開始,設計者需要進行FPGA功能的需求分析,然后進行模塊的劃分,比較復雜和龐大的設計,則會通過模塊劃分把工作交給一個團隊

2015-03-31 09:27:38

PSoC開發(fā)流程和一般MCU開發(fā)流程有什么區(qū)別?

2021-03-03 07:14:24

教程,自己看xilinx的文檔的話,不知道要看到啥時候。還是有些麻煩的,需要vivado配置一下硬件平臺,petalinux搞一下軟件平臺,合在一起放到sdsoc中生成用戶平臺。熟悉的路子再走一

2019-01-22 14:17:47

請問從零開始學習單片機開發(fā)需要一個怎樣的學習流程……網(wǎng)上搜索出來一大籮筐,不知道哪個才是靠譜的…… 感覺找不到路……感謝各位前輩指教

2016-05-20 15:19:16

?當我必須選擇開發(fā)環(huán)境時,我選擇了SDSoC平臺。任何人都有同樣的問題,可以幫我弄清楚該怎么辦?以上來自于谷歌翻譯以下為原文Hi,I downloaded SDSoC

2018-12-27 10:52:18

調試器嵌入式開發(fā)的流程步驟1:開發(fā)引導加載程序步驟2:內核實現(xiàn)步驟3:創(chuàng)建模塊(設備驅動程序)步驟4:創(chuàng)建應用程序步驟5(最后一步):系統(tǒng)調整結束語導語近年來,“嵌入式設備”對Linux的采用越來越多。Linux標準擁有的許多功能都符合嵌入式產(chǎn)品的目的,這是最大的原因。安裝在嵌入式設備上的Linux通常被

2021-11-05 06:35:11

項目,需要使用其中一個Zynq SOC器件開發(fā)產(chǎn)品。我有兩個Promo Key,它給了我1年的SDSoC開發(fā)套件許可證。我還有一些側面項目使用一些較舊的較小的Artix Xilinx器件。我的理解

2018-12-26 11:35:08

文件夾)我甚至拉了一個全能,我在網(wǎng)上找不到任何答案。希望有人能解決這個問題:D以上來自于谷歌翻譯以下為原文Dear sirs, My SDSoC 2016.1 on Ubuntu 14.04 prints

2019-04-26 08:07:43

的挑戰(zhàn)。如何開發(fā)出成功的硬件產(chǎn)品,一個產(chǎn)品由概念的產(chǎn)生到產(chǎn)品的落地量產(chǎn)又需要經(jīng)歷哪些流程呢?每個公司的流程可能不完全一樣,但都大同小異,通常可分為四個主要階段:調研期、原型期、小批量/產(chǎn)品化期及批量生產(chǎn)

2022-07-15 14:26:16

如何利用基于WiFi模塊的nodemcu開發(fā)板去點亮一個led燈呢?有哪些步驟?

2022-02-15 07:29:15

如何利用庫函數(shù)的方法進行開發(fā)使用STM32外設的基本流程呢?如何驅動平臺上的用戶指示燈呢?

2022-02-25 07:38:22

如何去開發(fā)一個人機交互的顯示屏呢?串口屏的開發(fā)步驟有哪些?

2021-10-25 07:22:58

你好,我已經(jīng)創(chuàng)建了一些示例SDSOC項目并注意到了這一點。我已經(jīng)檢查過,在執(zhí)行一個持續(xù)很長時間的功能的PL期間,處理器沒有停止,Zynq FPGA中的Core A9仍然保持在100%。如果

2020-05-08 10:00:52

如何對USART進行配置呢?有哪些步驟?USART的發(fā)送流程是怎樣的?

2021-11-17 07:35:37

如何給開發(fā)板替換一個精簡的文件系統(tǒng)呢?有哪些操作步驟?

2022-01-06 06:46:13

本文將系統(tǒng)地講解嵌入式Linux開發(fā)流程中的各個步驟,詳細解析各個流程中的疑點、難點。本書分3個部分,共12章。各部分內容如下:目錄展示內容展示基礎知識篇:第一章 嵌入式系統(tǒng)基礎第二章 Linux

2021-11-04 07:37:49

單片機和Linux的區(qū)別在哪?嵌入式Linux開發(fā)的流程是怎樣的呢?

2021-10-21 09:30:38

嵌入式系統(tǒng)開發(fā)流程方法/步驟1:建立開發(fā)環(huán)境,操作系統(tǒng)一般使用Redhat Linux,選擇定制安裝或全部安裝,通過網(wǎng)絡下載相應的GCC交叉編譯器進行安裝(比如,arm-1inux-gcc

2020-04-21 10:35:31

怎樣使用Matlab聯(lián)合STM32CubeMX以及Keil開發(fā)一個STM32的簡單程序呢?有哪些基本流程呢?

2021-11-18 06:42:36

怎樣去開發(fā)一種RK3399開發(fā)板呢?有哪些開發(fā)步驟?

2022-03-07 12:02:56

這是一個講解手機產(chǎn)品開發(fā)與設計的PPT,作者結合自己的開發(fā)經(jīng)驗詳細介紹了手機開發(fā)的步驟、流程以及軟硬件設計、ID設計知識,該PPT還對手機未來發(fā)展做了分析,對于手機設計工程師來說非常實用。

2012-08-12 01:51:57

一般軟件開發(fā)公司在開發(fā)軟件的時候需要通過以下流程步驟:一、需求分析產(chǎn)品經(jīng)理要進行需求采集、需求分析和需求確認這幾方面的工作,然后輸出需求分析文檔和產(chǎn)品原型圖,文檔和產(chǎn)品原型圖要及時與客戶進行溝通

2020-08-10 09:59:29

本文將系統(tǒng)地講解嵌入式Linux開發(fā)流程中的各個步驟,詳細解析各個流程中的疑點、難點。本書分3個部分,共12章。各部分內容如下:目錄展示由于文章篇幅原因,這里以目錄+知識點截圖的方式展示部分給大家

2021-11-05 08:18:47

本文將系統(tǒng)地講解嵌入式Linux開發(fā)流程中的各個步驟,詳細解析各個流程中的疑點、難點。本書分3個部分,共12章。各部分內容如下:目錄展示由于文章篇幅原因,這里以目錄+知識點截圖的方式展示部分給大家

2021-11-05 08:46:14

我非常想了解如果想設計一個類似risc-v的處理器,整個開發(fā)流程是怎樣的?

2023-12-09 18:39:01

設計一個收音機電路需要遵循以下步驟: 確定電路的功能和需求:在開始設計之前,需要明確電路的功能和需求,例如收音機的頻率范圍、音量大小、電臺數(shù)量等。 2.選擇合適的元器件:根據(jù)電路的需求,選擇

2023-04-19 14:15:51

PCB基本設計有哪些步驟流程?PCB布線工藝要求有哪些?PCB布線時要遵循哪些原則?

2021-04-23 06:26:27

請教一下RK3568開發(fā)板的啟動流程是怎樣的呢?

2022-03-02 06:50:18

請問一下MAX32660的開發(fā)流程是怎樣的呢?

2022-01-18 06:16:42

DSP設計流程通常包括哪些步驟?

2021-04-09 06:47:59

我可以在哪里獲得修訂堆棧。它是SDSOC 2016.4的一部分開始使用修訂版所需的所有工具(如SDSOC,VIVADO)是什么?謝謝

2020-05-21 10:09:52

印制板(PCB)的排版格式及流程步驟:印制板(PCB)的排版格式及流程步驟內容有元件的安裝方式,元件的排列方式,接點的形式,排版格式等內容。

2009-09-30 12:30:29 0

0 PCB光繪(CAM)的操作流程步驟

(一),檢查用戶的文件

用戶拿來的文件,首先要進行例行的檢查:

1,

2009-11-19 09:47:09 843

843 這是一個講解手機產(chǎn)品開發(fā)與設計的PPT,作者結合自己的開發(fā)經(jīng)驗詳細介紹了手機開發(fā)的步驟、流程以及軟硬件設計、ID設計知識,該PPT還對手機未來發(fā)展做了分析,對于手機設計工程

2011-09-05 14:44:33 0

0 針對STM32芯片介紹的USB開發(fā)步驟流程框圖,感興趣的朋友可以看看,圖框信息還包含有函數(shù)的調用和數(shù)據(jù)處理

2015-11-12 15:09:19 25

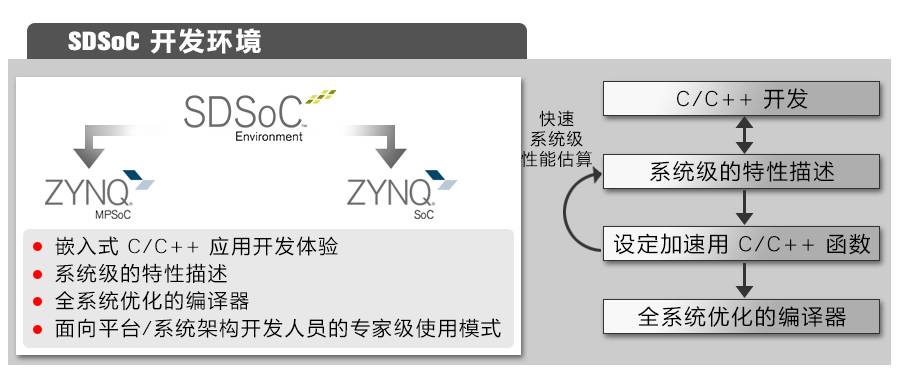

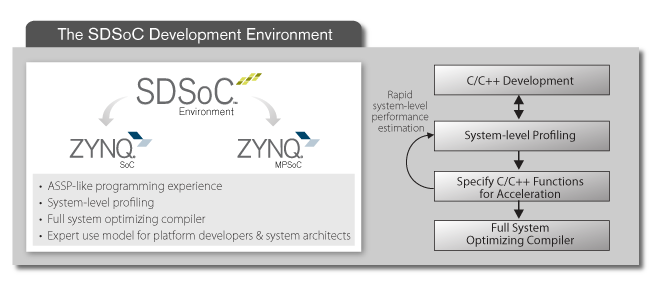

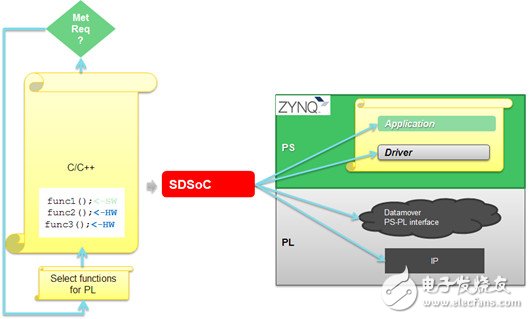

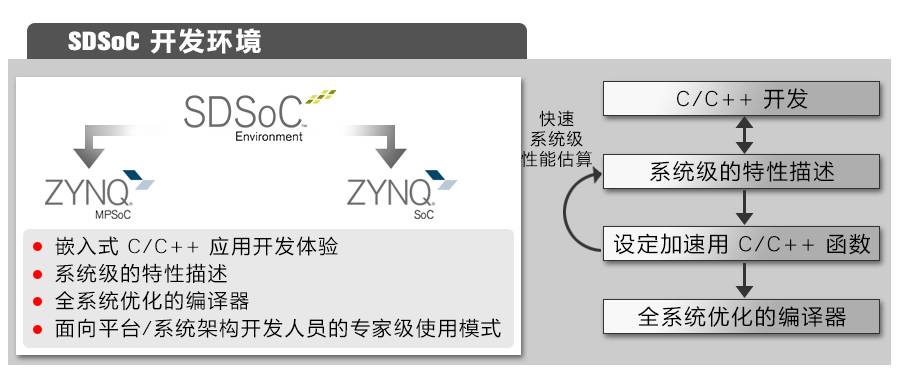

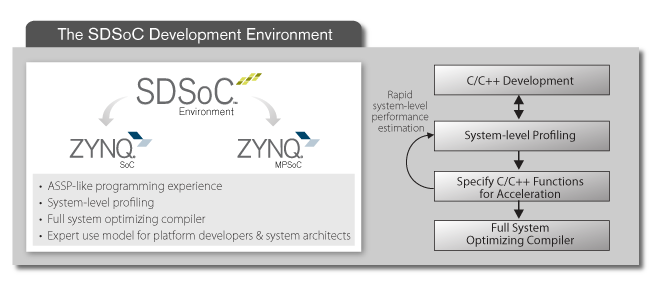

25 SDSoC是Xilinx旗下,用于設計開發(fā)Zynq SoC和MPSoC異構嵌入式系統(tǒng)的基于Eclipse的集成開發(fā)環(huán)境,可以完成從C/C++到指定目標平臺上功能完整的硬件/軟件系統(tǒng)的編譯、實現(xiàn)、調試執(zhí)行等全過程。

2016-04-13 10:05:15 954

954

SDSoC? 開發(fā)環(huán)境可為異構 Zynq? All Programmable SoC 及 MPSoC 部署提供類似嵌入式 C/C++/OpenCL 應用的開發(fā)體驗,其中包括簡單易用的 Eclipse IDE 和綜合設計環(huán)境。

2017-01-13 12:39:11 2131

2131 Xilinx SDSoC集成開發(fā)環(huán)境是Xilinx推出的面向其Zynq系列產(chǎn)品的嵌入式開發(fā)工具,目的是使不懂硬件的系統(tǒng)架構師和軟件架構師也能夠直接使用Zynq器件,在Zynq上用C/C++編程,只能

2017-02-08 11:10:11 207

207 SDSoC?? 開發(fā)環(huán)境面向公眾開放,包括擴展庫、開發(fā)板、和設計服務生態(tài)系統(tǒng)支持,并實現(xiàn) ?C/C++? 應用開發(fā)。此外,該版本還包含針對集成設計環(huán)境 ?(IDE)? 的增強特性,可實現(xiàn)輕松的編程及平臺開發(fā)。 觀看演示視頻 ??? 閱讀背景資料 ?(PDF) ?? 了解更多 ??

2017-02-09 03:33:01 217

217 新的SDSoC設計環(huán)境的構想。 軟件SDSoC提供了一個可編程環(huán)境,平臺不僅可以對傳統(tǒng)的SoC和ASSP進行開發(fā),也可以對Zynq UltraScale+等進行開發(fā),并且編程難度相當。當然,SDSoC

2017-02-09 06:13:11 170

170 公司進一步豐富其SDx產(chǎn)品系列,并持續(xù)將用戶群拓展至更廣闊的系統(tǒng)及軟件工程師社區(qū) 賽靈思推出面向全可編程SoC和MPSoC的SDSoC? 開發(fā)環(huán)境。作為賽靈思SDx?系列開發(fā)環(huán)境的第三大成員,SDSoC開發(fā)環(huán)境讓更廣闊的系統(tǒng)和軟件開發(fā)者群體也能獲益于“全可編程”SoC和MPSoC器件的強大優(yōu)勢。

2019-10-06 11:53:00 404

404 賽靈思在2015年七月宣布開放正式版SDSoC開發(fā)環(huán)境,現(xiàn)在我們的官網(wǎng)可以下載這一軟件,正式支持的開發(fā)板也在逐步增加中,除了在目前版本上打開SDSoC可以看到的包括賽靈思ZC702、706等開發(fā)平臺

2017-11-17 03:26:25 5826

5826

業(yè)界標桿性的入門級Zynq-7000平臺還免費附贈SDSoC Vochuer! 這一贈可謂激起千層浪,對于垂涎SDSoC已久的Digilent社區(qū)用戶而言,識貨者此等福利當然不會錯過。然,作為版主,在下也因此收到了不少關于SDSoC開發(fā)的問題。

2018-01-05 08:16:01 965

965 由于SDSoC設計實施上的靈活性,它被作為視頻處理的理想平臺,通過它可以創(chuàng)建一個優(yōu)化的視頻處理系統(tǒng),在處理性能、成本、功耗和開發(fā)時間等要素之間實現(xiàn)平衡。

2018-06-21 14:40:00 659

659 SDSoC:面向SoC和MPSoC 的軟件定義開發(fā)環(huán)境 TI參考設計可加速開發(fā)Xilinx MPSoC、SoC和FPGA應用電源解決方案 Zynq-7000能干什么 阿里云 全新一代 FPGA

2018-05-21 14:16:00 1999

1999 在理解了SDSoC“平臺”的概念之后(詳見《SDSoC上手必讀:什么是SDSoC平臺?》),現(xiàn)在我們就可以開始使用SDSoC進行開發(fā)工作了。 在下載并安裝了SDSoC之后,細心的人會在文件目錄中發(fā)

2018-06-04 01:31:00 7720

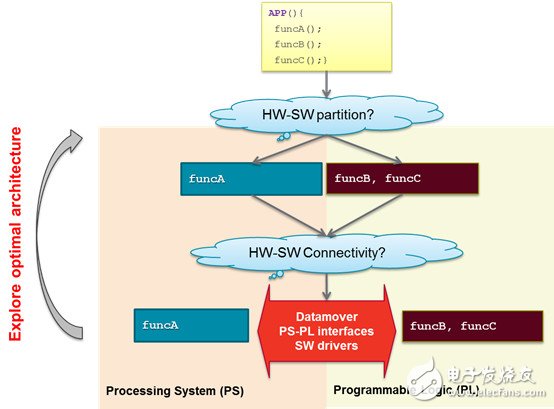

7720 讓我們先來看看一個典型的Zynq SoC開發(fā)流程(如圖1):開發(fā)者首先需要對軟硬件進行分區(qū),即確定系統(tǒng)哪些部分放入PL(可編程邏輯)中進行硬件加速,哪些部分在PS(處理器系統(tǒng))中用軟件實現(xiàn);接下來

2018-07-02 08:17:00 1862

1862 搭建平臺是使用SDSoc工具開發(fā)的第一步,對于如何搭建平臺,XILINX官方提供了較為詳細的說明,由于SDSoc2017.4包含了ZedBoard開發(fā)板平臺,而且提供的這個平臺也剛好配置了MIO(如下圖所示),因此這個例子就可以省去搭建平臺的操作。

2018-08-04 10:24:00 2079

2079

賽靈思公司(Xilinx)今天宣布推出正式版(Public Access Release)SDSoC開發(fā)環(huán)境,將Zynq SoC和MPSoC用戶擴展至廣泛的系統(tǒng)和軟件工程師社群。SDSoC開發(fā)環(huán)境

2018-08-21 09:32:00 2545

2545 FPGA的開發(fā)流程是遵循著ASIC的開發(fā)流程發(fā)展的,發(fā)展到目前為止,F(xiàn)PGA的開發(fā)流程總體按照圖1進行,有些步驟可能由于其在當前項目中的條件的寬度的允許,可以免去,比如靜態(tài)仿真過程,這樣來達到項目

2018-11-18 09:55:45 1273

1273

SDSoC?開發(fā)環(huán)境簡介的第2部分。

本視頻回顧了在Zynq?SoC器件中實施系統(tǒng)所面臨的挑戰(zhàn),以及SDSoC如何幫助解決這些挑戰(zhàn)。

然后在示例設計上展示SDSoC的演示......

2018-11-20 06:12:00 1989

1989 使用Zynq UltraScale + MPSoC的ZCU102開發(fā)套件,該視頻展示了使用SDSoC開發(fā)環(huán)境的開發(fā)流程。

2018-11-27 06:29:00 4495

4495 通過SDSoC開發(fā)環(huán)境僅使用C / C ++和硬件優(yōu)化庫,在硬件中加速OpenCV功能

2018-11-27 06:25:00 2755

2755 SDSoC開發(fā)環(huán)境提供了極為簡化的類似ASSP的C / C ++編程體驗,包括易于使用的Eclipse IDE和用于異構Zynq?AllProgrammable SoC和MPSoC部署的綜合設計環(huán)境。

2018-11-27 06:08:00 2964

2964 SDSoC是開發(fā)Zynq-7000 SoC應用程序的理想工具,當您可以在自己的定制板平臺上實現(xiàn)設計時,SDSoC變得更加強大。

有了這個視頻,看看創(chuàng)建自己的自定義硬件是多么容易..

2018-11-26 06:25:00 2305

2305 該演示強調了使用SDSoC?開發(fā)環(huán)境進行工業(yè)控制的優(yōu)勢。

它在磁場中顯示懸浮的鐵球,并進行連續(xù)的位置監(jiān)控。

2018-11-23 06:45:00 2397

2397 SDSoC?開發(fā)環(huán)境簡介的第2部分:該視頻回顧了實施挑戰(zhàn)以及SDSoC如何幫助解決這些挑戰(zhàn),采用完全實現(xiàn)的設計并對其進行修改以進一步優(yōu)化加速功能......

2018-11-22 06:56:00 2291

2291 SDSoC 開發(fā)環(huán)境可為異構 Zynq SoC 及 MPSoC 部署提供類似嵌入式 C/C++/OpenCL 應用的開發(fā)體驗,其中包括簡單易用的 Eclipse IDE 和綜合設計環(huán)境

2019-07-27 11:33:46 1728

1728 與傳統(tǒng)彼此孤立的嵌入式軟硬件開發(fā)流程不同,SDSoC 不會造成開發(fā)延遲,也不會出現(xiàn)系統(tǒng)架構和性能不確定性的問題,其經(jīng)過精心架構設計,可提供快速系統(tǒng)特性分析和架構探索,并采用熟悉的 Eclipse IDE 框架。

2019-07-30 14:45:07 1456

1456 在本次研討會中,賽靈思的專家們將通過一個完整的流程案例,手把手教你如何針對一個硬件優(yōu)化的系統(tǒng)將 C 代碼進行優(yōu)化。同時還將為您介紹 SDSoC 的一些新功能,以及如何無縫地將您的硬件或軟件設計作為可重用資源導入到 SDSoC 中。

2019-08-01 14:21:49 1631

1631

lon公司創(chuàng)始人兼CEO Davor Kovacec指出:“利用賽靈思的新型SDSoC開發(fā)環(huán)境,并結合使用面向嵌入式圖形視頻的MicroZed開發(fā)板視覺平臺和Xylon logicBRICKSIP

2019-07-31 15:02:32 2682

2682 SDSoC? 開發(fā)環(huán)境可為異構Zynq? 全可編程SoC及MPSoC部署提供類嵌入式 C/C++ 應用的開發(fā)體驗,其中包括簡單易用的 Eclipse IDE 和綜合設計環(huán)境。SDSoC提供業(yè)界

2019-11-12 14:12:08 1170

1170

FPGA的設計流程就是利用EDA開發(fā)軟件和編程工具對FPGA芯片進行開發(fā)的過程。FPGA的開發(fā)流程一般包括功能定義/器件選型、設計輸入、功能仿真、邏輯綜合、布局布線與實現(xiàn)、編程調試等主要步驟。

2019-11-06 15:17:28 2224

2224 FPGA的設計流程就是利用EDA開發(fā)軟件和編程工具對FPGA芯片進行開發(fā)的過程。FPGA的開發(fā)流程包括功能定義/器件選型、設計輸入、功能仿真、邏輯綜合、布局布線與實現(xiàn)、編程調試等主要步驟。

2019-11-20 15:06:28 1545

1545 Xilinx SDSoC 開發(fā)環(huán)境可通過兩種方式加速Zynq SoC 和MPSoC 開發(fā)進程。第一種是,軟件開發(fā)人員借助賽靈思平臺、第三方平臺

2020-07-02 10:18:00 2321

2321 時間上的優(yōu)勢。但是,大部分的流程步驟還是需要我們循規(guī)蹈矩的去做,因為這些步驟的輸入是上一個步驟的結果,輸出是下一個步驟的輸入的關系,這樣的步驟就必不可少了。 FPGA開發(fā)的具體難度,與軟件開發(fā)有輸入、編譯、鏈接、執(zhí)行步驟對應的就

2020-10-25 10:05:37 3592

3592

采購業(yè)務處理流程步驟教程下載

2021-09-09 10:21:01 4

4 芯片制造工藝流程步驟:芯片一般是指集成電路的載體,芯片制造工藝流程步驟相對來說較為復雜,芯片設計門檻高。芯片相比于傳統(tǒng)封裝占用較大的體積,下面小編為大家介紹一下芯片的制造流程。

2021-12-15 10:37:40 41572

41572 芯片開發(fā)流程包括哪幾項?芯片開發(fā)流程包括規(guī)格制定、詳細設計、 HDL編碼、仿真驗證、邏輯綜合、STA、 形式驗證、布局規(guī)劃、布線、CTS、寄生參數(shù)提取、版圖物理驗證等步驟。

2021-12-15 11:13:30 16772

16772 芯片的制造需要百個步驟,工程量巨大,一顆小小的芯片從設計到量產(chǎn)可能需要四個月的時間。那么下面我們一起來看看芯片制造工藝流程步驟。 芯片制造工藝流程步驟 沉積:將材料薄膜沉積到晶圓上。材料可以是導體

2021-12-22 15:13:22 32745

32745 單片機的開發(fā)流程是一個有序的過程,通常包括以下幾個關鍵步驟。請注意,下面的描述是一個一般化的單片機開發(fā)流程,并且在實際應用中可能會有一些差異。

2023-05-19 13:46:55 1126

1126 pcb設計一般流程步驟

2023-12-13 17:30:30 1333

1333

電子發(fā)燒友App

電子發(fā)燒友App

評論