S2C日前宣布他們已經開發了一種原型驗證產品,即TAI Verification Module(專利申請中)。它允許使用者通過一條x4 PCIe Gen2通道到連接FPGA原型中的用戶設計和用戶的電腦,使得用戶能夠使用大量

2011-06-16 08:55:48 1785

1785 什么是FPGA原型?? FPGA原型設計是一種成熟的技術,用于通過將RTL移植到現場可編程門陣列(FPGA)來驗證專門應用的集成電路(ASIC),專用標準產品(ASSP)和片上系統(SoC)的功能

2022-07-19 16:27:29 1735

1735 原型驗證過程中的ASIC到FPGA的代碼是怎樣進行轉換的?

2021-05-08 09:16:18

的費用持續上升。一次失敗的ASIC流片將會推遲數個月的上市時間。誰愿意承擔簽字的責任呢? 一些BUG通過仿真和Emulation是抓不到的。傳統的驗證方法認為設計的功能符合功能定義就是對的。 但功能定義到底對不對呢?唯一的辦法就是建立一個真實的硬件:原型。

2019-07-11 08:19:24

。 ASIC在離開生產線后再也無法改變。這就是為什么設計師在大規模量產之前需要完全確保設計正確無誤。工程師可以利用FPGA的可重配置這一優勢,進行ASIC的原型驗證,以便在將設計發送到代工廠之前,可以在

2020-12-01 17:41:49

1ASIC 驗證技術.................................................11.1 ASIC 設計流程

2015-09-18 15:26:25

ASIC設計-FPGA原型驗證

2020-03-19 16:15:49

FPGA 驗證可以說就完成了 ASIC 整套流程的 50~80%。從設計成本來考慮,小批量上 FPGA 占優,大批量時,ASIC 占優。FPGA 本身就是一個芯片,只是你可以通過編程的方式修改內部邏輯連接

2020-09-25 11:34:41

。FPGA本身就是一個芯片,只是你可以通過編程的方式修改內部邏輯連接和配置實現自己想要的功能。實現ASIC,就如從一張白紙開始,你得有代碼,之后綜合,之后布局,布線,得到GDSII后去流片。比速度相同的工藝

2017-09-02 22:24:53

FPGA原型驗證已是當前原型驗證的主流且成熟的芯片驗證方法——它通過將RTL移植到現場可編程門陣列(FPGA)來驗證ASIC的功能,并在芯片的基本功能驗證通過后就可以開始驅動的開發,一直到芯片

2020-08-21 05:00:12

ASIC是一種為專門目的而設計的集成電路,是指應特定用戶要求和特定電子系統的需要而設計、制造的集成電路。ASIC的特點是面向特定用戶的需求,亮點在于運行速度在同等條件下比FPGA快。FPGA作為

2017-06-12 15:56:59

既然是芯片驗證,那就需要明確驗證芯片的哪些特性(功能、性能等)。驗證空間是無窮大的,驗證工程師需要在有限的時間內,完成盡可能多的重要verification features的驗證

2022-12-30 16:21:57

。這是由于在 FPGA 質量和開發時間上提高了 UVVM 良率。這個開源庫和方法具有最廣泛的 VHDL 驗證支持,讓您以非常有效的方式驗證真正復雜的 DUT,提供類似于 UVM 的模塊化、可重用性

2022-02-13 17:03:49

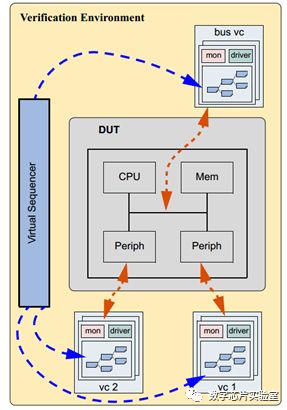

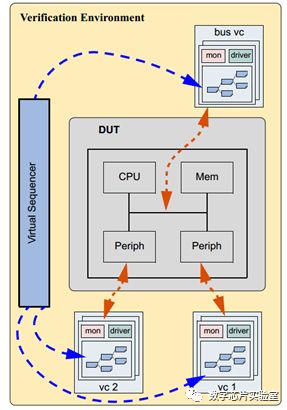

model)。一個簡單的驗證平臺框圖:在UVM中,引入了agent和sequence的概念,因此UVM中驗證平臺的典型框圖長這樣:通知:本章更新后在更新一篇《IC驗證之UVM常用宏匯總(四)》將不

2020-12-02 15:21:34

加入factory機制 上一節《IC驗證"一個簡單的UVM驗證平臺"是如何搭建的(五)》給出了一個只有driver、使用UVM搭建的驗證平臺。嚴格來說這根本就不算是UVM驗證

2020-12-08 12:07:21

的組件,是整個驗證平臺數據流的源泉。本節以一個簡單的DUT為例,說明一個只有driver的UVM驗 證平臺是如何搭建的。最簡單的驗證平臺,假設有如下的DUT定義:這個DUT的功能非常簡單,通過rxd接收

2020-12-04 15:48:19

Verification Methodology),其正式版是在2011年2月由Accellera推出的,得到了Sysnopsys、Mentor和Cadence 的支持。UVM幾乎完全繼承了OVM,同時又采納了

2020-12-01 15:09:14

在上一節中,**《IC驗證"UVM驗證平臺加入factory機制"(六)》**雖然輸出了“main_phase is called”,但是“data is drived”并沒有

2020-12-09 18:28:15

第二章 驗證flow驗證的Roadmap驗證的目標UVM驗證方法學ASIC驗證分解驗證策略和任務的分解AMBA可重用、靈活性、兼容性、廣泛支持一.驗證的Roadmap1.ASIC芯片項目流程市場需求

2021-11-01 06:28:47

Knowledge of SoC (ASIC/FPGA) design and verification tools. System One to Two

2009-04-10 15:17:03

in ASIC verification.- Needs to have better understanding of Verification methodology and concepts-

2012-08-20 18:35:50

本帖最后由 NvidiaHR 于 2012-7-6 14:28 編輯

ASIC/SOC Verification Engineer:RESPONSIBILITIES:- RTL design

2012-07-06 14:27:07

方法中的漏洞。用于可笑的測試并支持設計人員運行他們自己的驗證。加快標準驗證流程并支持芯片啟動測試開發。等等等等。 這份長達 500 多頁的介紹性材料將向讀者介紹處理硬件驗證需求的主要 Python

2022-11-03 13:07:24

先進的設計與仿真驗證方法成為SoC設計成功的關鍵。一個簡單可行的SoC驗證平臺,可以加快SoC系統的開發與驗證過程。FPGA器件的主要開發供應商都針對自己的產品推出了SoC系統的開發驗證平臺,如

2019-10-11 07:07:07

on design language Verilog/VHDL Good knowledge on SystemVerilog, and verification methodology OVM/UVM Good

2012-04-05 23:26:48

。HAPS-51采用FPGA陣列Xilinx Virtex-5 LX330和板上存儲器,加快了ASIC驗證的速度。先前的HAPS系統在存儲器存取方面采用子板,而最新的HAPS-51則采用位于板上并靠近

2018-11-20 15:49:49

設計。 現代ASIC常包含整個32-bit處理器,類似ROM、RAM、EEPROM、Flash的存儲單元和其他模塊. 這樣的ASIC常被稱為SoC(片上系統)。 FPGA是ASIC的近親,一般通過

2012-02-27 17:46:03

AMD超威半導體上海研發中心招聘 ASIC Design Verification Engineer;請有意向者將簡歷發送到 Maggie1.Zhang@amd.com 以及

2017-03-13 16:47:03

design3.Familiar with System-Verilog and UVM verification methodology4.Familiar with script languages

2018-09-19 14:15:19

的開發和驗證符合這一過程是DO-254.1的目標安森美半導體& DO-254支持安森美半導體的數字ASIC設計流程及其采用的方法完全支持需要獲得DO-254認證的商用飛機制造商的嚴格要求。符合

2018-10-17 15:03:44

大家好,我是一哥,上章內容我們介紹什么是uvm?uvm的特點以及uvm為用戶提供了哪些資源?本章內容我們來看一看一個典型的uvm驗證平臺應該是什么樣子的,來看一個典型的uvm測試平臺的結構。我們一個

2022-02-14 06:46:33

就以支持AWS的FPGA平臺為主要方案。 至此,FPGA AI這樣一來設計迭代速度(尤其是配合了Chisel,HLS等敏捷開發流程之后)可以遠遠快于傳統ASIC流程,同時硬件的能效比則遠高于傳統

2023-03-28 11:14:04

提供的門電路規模足夠大,通過編程,就能夠實現任意ASIC的邏輯功能。

FPGA開發套件,中間那個是FPGA芯片

我們再看看FPGA的發展歷程。

FPGA是在PAL(可編程

2024-01-23 19:08:55

/verifications. 2. Responsible for IPs/SOC design FPGA emulation/verification. 3. Responsible for chip

2015-06-12 12:07:37

Systemverilog [1]和 UVM [2]為驗證團隊提供結構和規則。它使得在許多測試中能獲得一致的結果,并可以在團隊之間共享驗證。許多驗證團隊都在使用由C代碼編寫的驗證套件。本文將討論將基于C的測試和驗證套件集成到常規UVM測試平臺的各種方法。

2020-12-11 07:59:44

Systemverilog [1]和 UVM [2]為驗證團隊提供結構和規則。它使得在許多測試中能獲得一致的結果,并可以在團隊之間共享驗證。許多驗證團隊都在使用由C代碼編寫的驗證套件。本文將討論將基于C的測試和驗證套件集成到常規UVM測試平臺的各種方法。

2020-12-15 07:38:34

的驗證結構,以及以功能覆蓋率為指標的驗證流程。在本文中,圍繞Synopsys的VMM(Verification Methodology Manual)構建了一個MCU驗證環境。

2019-07-01 08:15:47

如何通過視頻幀加快視頻設備開發和調試速度?

2021-06-03 06:51:58

ASIC驗證能夠采用的主要技術是什么?如何利用現成FPGA開發板進行ASIC原型開發?

2021-05-08 07:51:04

請教各位大佬,UVM是基于sv的驗證方法學,如果采用systemc語言編程,如何實現?

2019-11-07 15:30:16

可編程門陣列FPGA具有可編程特性,用戶根據特定的應用定制電路結構,因此其處理速度大大超過通用處理器。與ASIC相比,FPGA的缺點是在提供靈活的可編程同時,則以芯片的面積、功耗和速度做為代價。

2019-09-03 07:44:22

Ctrl-V!)

幾點說明:

為了使用UVM庫里的函數和宏定義,需要先import uvm_pkg和include uvm_macros。

在testbench的頂層(module tb)里通過

2023-11-03 10:18:58

:外商獨資·外企辦事處 下屬人數:0 企業規模:100-499人 崗位職責Responsibilities:1.FPGA design and verification. Porting ASIC code

2012-03-15 13:55:19

,對黑盒驗證,我們只能通過了解其設計文檔來了解它的功能。驗證就存在著數據比較。通常的做法是使用高級語言為被測設計建立一個參考模型,這個參考模型將模擬被測設計的行為,并給出相應的結果,將這個理想的結果

2021-01-21 15:59:03

會在一定范圍內產生,減少無用的激勵,提高效率。支持覆蓋率驅動模式,根據當前覆蓋率的情況,驗證工程師可以決定下一步的驗證內容,當覆蓋率達到了一定的要求時,就可以宣告驗證工作的完成。uvm驗證平臺,它具有很高的可重用性

2021-01-21 16:00:16

大家好,我是一哥,上章內容我們介紹什么是uvm?uvm的特點以及uvm為用戶提供了哪些資源? 本章內容我們來看一看一個典型的uvm驗證平臺應該是什么樣子的,來看一個典型的uvm測試平臺的結構

2021-01-22 15:32:04

大家好,我是一哥,上章一個典型的uvm驗證平臺應該是什么樣子的?從本章開始就正式進入uvm知識的學習。先一步一步搭建一個簡單的可運行的測試平臺。 本章首先來介紹一下構成uvm測試平臺的主要組件

2021-01-22 15:33:26

the UniversalVerification Methodology(UVM)》,后來的第二版我很喜歡,里面配有大量實際驗證中的例子,很有價值。這本身出版后反映不錯,所以有了后來的另一

2015-03-11 16:24:35

浮點是最優選的數據類型,可確保算法建模和仿真的高精度計算。傳統上,當您想要將這種浮點算法部署到FPGA或ASIC硬件時,您唯一的選擇是將算法中的每種數據類型轉換為定點,以節省硬件資源并加快計算速度

2018-09-11 21:59:16

失敗的原因不是時序或者功率的問題,而是邏輯或功能錯誤。為此,功能驗證已經成為ASIC開發周期中一個最關鍵的環節,通常最耗費時間。越來越多的ASIC設計人員發現通過采用FPGA進行功能原型設計能夠最好

2019-07-15 07:00:39

。基于FPGA的原型驗證方法憑借其速度快、易修改、真實性的特點,已經成為ASIC芯片設計中重要的驗證方法。本文主要描述高頻RFID芯片的FPGA原型驗證平臺的設計,并給出驗證結果。1、RFID芯片的FPGA

2019-05-29 08:03:31

that dominates time scales. This book defines a methodology that helps minimize the time necessary to meet the verification requirements. It also takes

2009-07-22 14:39:21 37

37 that dominates time scales. This book defines a methodology that helps minimize the time necessary to meet the verification requirements. It also takes

2009-07-22 14:41:06 13

13 在現在復雜的ASIC 設計中,校驗(Verification)是最大的瓶頸。隨著先進的半導體工藝技術不斷前進,隨之帶來的是ASIC 設計規模和設計復雜度的飛速增長,這使得傳統的軟件仿真工具

2009-11-24 12:20:02 24

24 a means of Mentor’s advanced verification methodology (AVM) basedunified verification platform solution.The continuing growth o

2010-07-04 11:39:45 17

17 Open Verification Methodology(OVM)是Mentor Graphics 和Cadence 共同推出的,業界第一個基于SystemVerilog、通用開放的驗證方法學;其基于事務交易級的方法學,基于Factory Pattern 的對象生

2010-07-04 11:43:22 7

7 FPGA原型驗證和其他驗證方法是不同的,任何一種其他驗證方法都是ASIC驗證中的一個環節,而FPGA驗證卻是一個過程。由于FPGA與ASIC在結構、性能上各不相同,ASIC是基于標準單元庫,FPGA用的

2010-09-10 17:22:26 989

989 對ASIC設計進行FPGA原型驗證時,由于物理結構不同,ASIC的代碼必須進行一定的轉換后才能作為FPGA的輸入。 現代集成電路設計中,芯片的規模和復雜度正呈指數增加。尤其在ASIC設計流程中

2011-03-25 15:16:20 108

108 MathWorks 近日宣布推出 HDL Coder,該產品 支持MATLAB 自動生成 HDL 代碼,允許工程師利用廣泛應用的 MATLAB 語言實現 FPGA 和 ASIC 設計。

2012-03-07 09:27:18 2033

2033

本文描述ASIC驗證方法和過程,有助于ASIC設計者對驗證的認識。模擬是驗證ASIC并產生測試矢量的唯一途徑,設計者可以對ASIC芯片或者在ASIC應用系統中進行功能和時序模擬。

2012-05-24 09:32:47 23

23 本文描述ASIC驗證方法和過程,有助于ASIC設計者對驗證的認識。模擬是驗證ASIC并產生測試矢量的唯一途徑,設計者可以對ASIC芯片或者在ASIC應用系統中進行功能和時序模擬。

2012-05-24 09:32:47 27

27 徹底地驗證其片上系統(SoC)是否符合HDMI 2.0規范,從而加速批量生產的準備時間。這款用于HDMI 2.0的Cadence VIP支持各種主流邏輯模擬器、驗證語言及包括UVM(Universal Verification Methodology)在內的方法學。

2013-09-27 16:19:08 857

857 基于UVM的CPU卡芯片驗證平臺_錢一文

2017-01-07 19:00:39 4

4 基于UVM的驗證平臺設計研究_王國軍

2017-01-07 19:00:39 4

4 基于UVM的CAN模塊自驗證方法_熊濤

2017-01-08 14:47:53 3

3 一種基于UVM的混合信號驗證環境_耿睿

2017-01-07 21:39:44 1

1 ?7200? 萬個 ?ASIC? 門的容量。 FPGA? 原型設計系統通過添加多達 ?3? 個附加電路板,可使用 ?Aldec? 背板 ?(HES7-BPx4)? 擴展至 ?28800? 萬個 ?ASIC? 門。 了解更多 ??

2017-02-09 06:27:08 327

327 FPGA原型驗證和其他驗證方法是不同的,任何一種其他驗證方法都是ASIC驗證中的一個環節,而FPGA驗證卻是一個過程。

2017-02-11 12:46:11 2975

2975 的連接、驅動器、監視器、仿真序列以及功能覆蓋率的建立。 本文呈現出了一種使用UVM驗證方法學構建基于高可配置性的高級微處理器總線架構(AMBA)的IP驗證環境,其中會使用到Synopsys公司的AMBA VIP和Ruby腳本。該驗證環境可以支持通過使用AMBA設計參數進行自

2017-09-15 14:37:34 6

6 。 本文所聚焦的技術手段是讓一個已有的UVM驗證平臺通過改變需求去執行硬件加速。如果這些點在UVM環境開發過程中被考慮到,那么之后將環境遷移到硬件加速器作為一個性能選項將是一件較容易的事情。本文所提議的建議將會使你的UVM驗證

2017-09-15 17:08:11 14

14 近年來,ASIC設計規模的增大帶來了前所未有的芯片原型驗證問題,單顆大容量的FPGA通常已不足以容下千萬門級、甚至上億門級的邏輯設計。現今,將整個驗證設計分割到多個采用最新工藝大容量FPGA中,FPGA通過高速總線互聯,成為大規模ASIC或SOC原型驗證的極佳選擇。

2018-07-02 08:20:00 1695

1695 采用fpga原型技術驗證asic設計,首先需要把asic設計轉化為fpga設計。但asic是基于標準單元庫,fpga則是基于查找表,asic和fpga物理結構上的不同,決定了asic代碼需要一定

2019-07-23 08:07:00 1923

1923

ASIC芯片一旦流片功能就無法改變,基本專片專用。而FPGA可配置特性就可以應用在功能會改變的場合,例如,原型驗證,ASIC設計過程中會使用到FPGA來進行原型驗證;功能升級,在產品中采用FPGA實現一些業內暫時還沒成熟的解決方案,可以在后續功能變動時方便升級。

2019-08-25 10:40:01 10934

10934

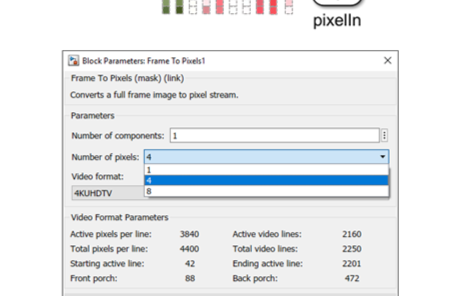

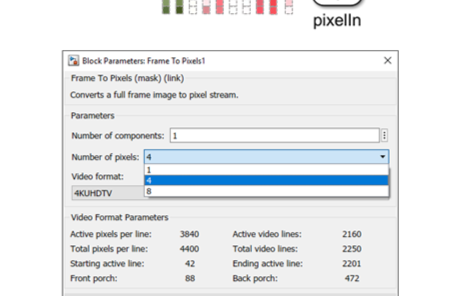

上處理高幀率 (HFR) 和高分辨率視頻的原生多像素流處理支持。視頻、圖像處理和 FPGA 設計工程師在處理 240fps 或更高分辨率的 4k 或 8k 視頻時可以加快權衡表現和實現的探索和仿真速度。

2020-03-01 12:40:38 725

725 MathWorks宣布,HDLVerifier從現已上市的Release2019b開始提供對UniversalVerificationMethodology(UVM)的支持。

2020-03-07 14:29:17 815

815 MathWorks宣布,隨著 2019b 發行版的 MATLAB 和 Simulink 產品系列最近上市,Vision HDL Toolbox提供對在 FPGA 上處理高幀率 (HFR) 和高分辨率視頻的原生多像素流處理支持。

2020-05-09 10:55:41 331

331

本周美國海關及邊境保衛局宣布將在更多機場中實行“簡化到達”計劃,即通過人臉識別驗證乘客身份,加快安檢速度和防止非法入境。

2020-10-15 09:52:43 547

547 Express 5.0的物理層和電氣接口。 新思科技CXL驗證IP基于新一代SystemVerilog的 Universal Verification Methodology(UVM)架構,使驗證IP的集成

2020-12-26 11:04:10 2458

2458 本文是本人對xilinx XC7V系列FPGA用于ASIC前端驗證遇到問題的總結,為自己記錄并分享給大家,如果有歧義或錯誤請大家在評論里指出。

2021-01-12 17:31:44 9

9 大家好,我是一哥,上章內容我們介紹什么是uvm?uvm的特點以及uvm為用戶提供了哪些資源?本章內容我們來看一看一個典型的uvm驗證平臺應該是什么樣子的,來看一個典型的uvm測試平臺的結構。我們

2021-12-09 13:36:13 7

7 需要門級驗證:FPGA 和 ASIC 一樣需要設計級驗證。但是,FPGA 在門級不是細粒度的,因此它們不需要門級驗證。您將每個門都放置在 ASIC 設計中,因此您需要驗證每個門。

2022-06-20 16:13:05 2184

2184

ASIC設計服務暨IP研發銷售廠商智原科技(Faraday Technology Corporation,TWSE:3035)今日發布FPGA-Go-ASIC驗證平臺。

2022-07-29 10:08:16 784

784 利用Systemverilog+UVM搭建soc驗證環境

2022-08-08 14:35:05 5

5 百度百科對UVM的釋義如下:通用驗證方法學(Universal Verification Methodology, UVM)是一個以SystemVerilog類庫為主體的驗證平臺開發框架,驗證工程師可以利用其可重用組件構建具有標準化層次結構和接口的功能驗證環境。

2022-11-30 12:47:00 1061

1061 因為DUT是一個靜態的內容,所以testbench理應也是靜態的,其作為uvm驗證環境和DUT的全局根結點。

2023-03-21 11:33:02 982

982 FPGA原型設計是一種成熟的技術,用于通過將RTL移植到現場可編程門陣列(FPGA)來驗證專門應用的集成電路(ASIC),專用標準產品(ASSP)和片上系統(SoC)的功能和性能。

2023-04-10 09:23:29 947

947 本文使用Easier UVM Code Generator生成包含多個agent和interface的uvm驗證環境。

2023-06-06 09:13:02 584

584 UVM提供了實現 **覆蓋驅動驗證(coverage-driven verification ,CDV)** 的框架。 CDV結合了自動測試向量生成,自檢查和覆蓋率收集,顯著地縮短了用于驗證設計時間。

2023-06-25 11:38:58 861

861

FPGA原型設計是一種成熟的技術,用于通過將RTL移植到現場可編程門陣列(FPGA)來驗證專門應用的集成電路(ASIC),專用標準產品(ASSP)和片上系統(SoC)的功能和性能。

2024-01-12 16:13:01 220

220 FPGA驗證和UVM驗證在芯片設計和驗證過程中都扮演著重要的角色,但它們之間存在明顯的區別。

2024-03-15 15:00:41 94

94

電子發燒友App

電子發燒友App

評論