先給大家簡單快速地介紹一下 Vivado 集成設(shè)計(jì)環(huán)境,即 IDE。當(dāng)打開 Vivado 工程后,會有一個(gè)工程概要,向您介紹工程的設(shè)置、警告和錯(cuò)誤信息以及工程的一般狀態(tài)。

2012-04-25 09:00:43 6408

6408 LINE首度在臺舉辦LINE Taiwan TechPulse,廣邀在地開發(fā)合作伙伴共襄盛舉,會中除介紹LINE平臺上的五大開發(fā)套件外,也公開三大研發(fā)工程部門的團(tuán)隊(duì)文化,宣布擴(kuò)大全球人才,希望吸引各方好手一起加入LINE為行動世代開發(fā)各種創(chuàng)新應(yīng)用!

2016-12-27 11:36:19 887

887 世界領(lǐng)先的生物識別技術(shù)公司Fingerprint Cards (簡稱Fingerprints)宣布在中國成立客戶工程部門,這個(gè)部門的研發(fā)團(tuán)隊(duì)主要為全球及本地的移動設(shè)備OEM客戶提供服務(wù)。在此之前,F(xiàn)ingerprints 在全球設(shè)有四個(gè)研發(fā)中心,這個(gè)在華新設(shè)的客戶工程部門是該公司在研發(fā)投入方面的重大舉措。

2018-04-27 10:06:01 10499

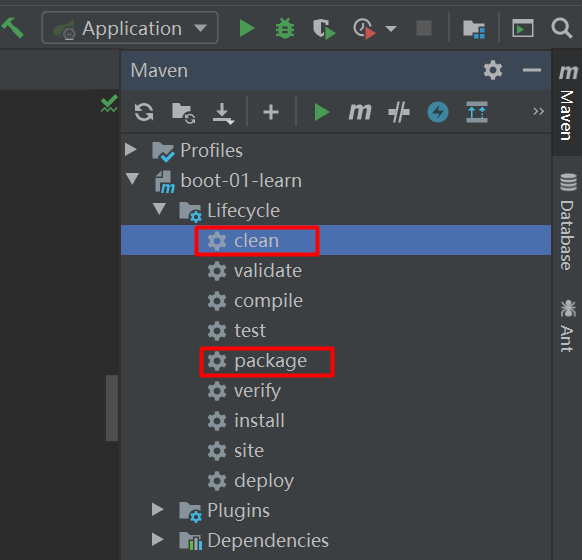

10499 01. Vivado的兩種工作模式 Vivado設(shè)計(jì)有工程和非工程兩種模式: 1. 工程模式: 工程模式是使用Vivado Design Suite自動管理設(shè)計(jì)源文件、設(shè)計(jì)配置和結(jié)果,使用圖形化

2020-11-09 17:15:47 3884

3884

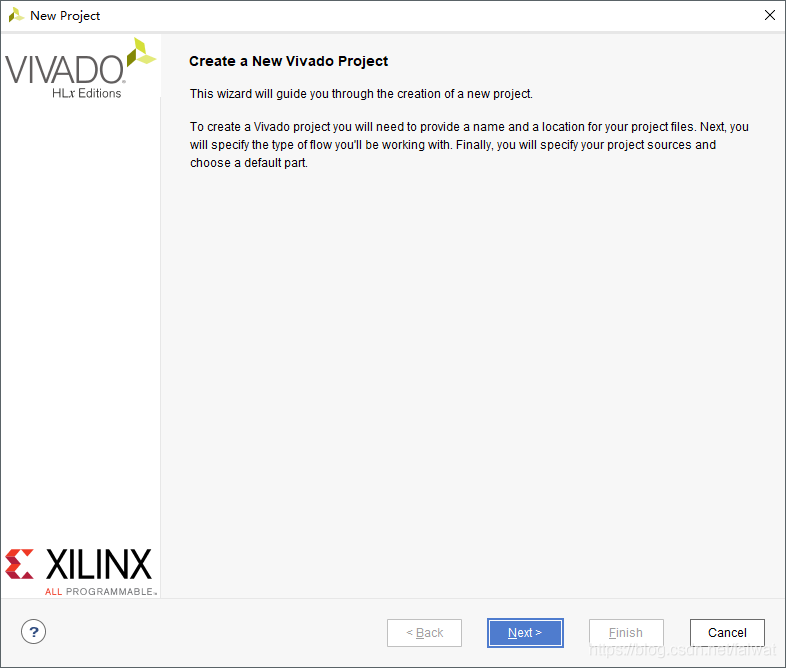

雙擊桌面圖標(biāo)打開Vivado 2017.2,或者選擇開始>所有程序>Xilinx Design Tools> Vivado 2017.2>Vivado 2017.2;

2023-07-30 09:39:11 403

403

大家好,我正在嘗試在Vivado 2013.4上運(yùn)行實(shí)施。我正在使用synplify_proI-2014.03-SP1合成我的設(shè)計(jì)。我能夠合成設(shè)計(jì)并導(dǎo)入并正確創(chuàng)建一個(gè)新的vivado項(xiàng)目。當(dāng)我嘗試

2018-10-18 14:40:02

你好,我試圖在SDK中運(yùn)行基本的“Hello world”程序,但我不斷收到錯(cuò)誤:在vivado硬件管理器中,我看到連接的2個(gè)設(shè)備,但arm_dap_0設(shè)備具有N / A狀態(tài),而xc7z010_1

2020-04-20 09:12:04

嗨,我是新來的,這似乎論壇的這一部分是我的問題的最佳位置。如果有更好的地方發(fā)布或移動它,請告訴我。我已經(jīng)購買了一個(gè)Zedboard,并嘗試根據(jù)Zedboard論壇上的建議升級到更新版本的Vivado

2018-11-01 16:10:41

我已經(jīng)安裝了Vivado 2017.3當(dāng)我打開電腦時(shí),我收到了Vivado 2017.3.1更新的通知。按下“下一步”按鈕后運(yùn)行更新程序時(shí),我進(jìn)入附件中顯示的頁面,該頁面為空白,“下一步”按鈕不執(zhí)行

2019-01-02 14:47:49

請問在Xilinx Vivado之中,沒有PL的工程,能否直接開啟SDK程序,并固化程序到ZYNQ的芯片之上

2021-03-29 17:22:00

`特權(quán)同學(xué)原創(chuàng),轉(zhuǎn)載請保留署名Vivado的工程文件包含了源碼、IP、設(shè)置和各種編譯的中間文件,動輒上百M(fèi)B甚至上GB,非常占硬盤。可以通過以下步驟對編譯過的工程進(jìn)行瘦身,只預(yù)留必要的設(shè)置、IP

2020-08-17 08:41:25

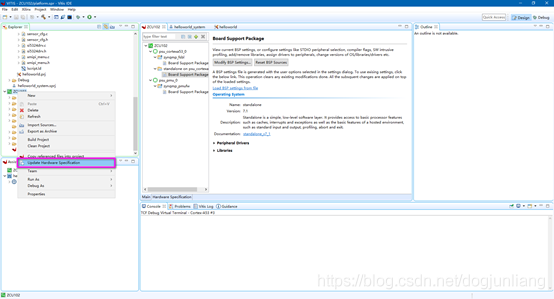

立的硬件平臺上右擊,選擇Update Hardware Specification,選擇最新導(dǎo)出的硬件平臺文件; 在建立的應(yīng)用工程上,選擇應(yīng)用工程對應(yīng)的硬件平臺,將上一個(gè)目錄的硬件平臺Remove,否則刪除上一個(gè)VITIS目錄后,目前移動以后的VITIS工程編譯會出錯(cuò)。

2021-01-15 16:46:02

你好,我需要一些幫助。上電時(shí),我的開發(fā)板DS1 LED發(fā)紅光,Vivado硬件管理無法識別電路板。它工作正常,但在最后一次電源循環(huán)后,這個(gè)問題出現(xiàn)了。嘗試過電源循環(huán),閃存編程(由于vivado硬件管理不再認(rèn)可電路板,因此沒有成功)。我沒有想法。有任何想法嗎。謝謝

2020-05-25 06:33:33

適用于板卡型號: AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG 實(shí)驗(yàn)Vivado工程為

2021-01-22 06:46:21

的 Xilinx Platform Studio(XPS) 和 Vivado 的 IP Integrator 都是用于設(shè)計(jì)嵌入式硬件系統(tǒng)的環(huán)境,但是它們的用戶界面迥然不同。XPS 使用一系列的下拉

2021-01-08 17:07:20

和調(diào)試PRX100-D開發(fā)板注意事項(xiàng)1.與Vivado軟件本身相關(guān)的問題Vivado在添加新的工程/HDL文件后會自動崩潰退出這一問題出現(xiàn)在2018.2版本中。Xilinx官方網(wǎng)站上說明在2017.1版本

2021-07-31 09:09:20

我目前遇到的問題是,我的同事只給一個(gè)SDK程序,但沒有給PL工程文檔,打開vivado的時(shí)候是使用其他的PL工程,進(jìn)去SDK程序查看程序,我納悶的是PL的部分只給了一個(gè).bit文檔,這是幾個(gè)意思,是否能實(shí)現(xiàn)工作、固化程序、debug已及run是否執(zhí)行?

2021-03-29 17:29:14

的編譯狀態(tài),以及Vivado工具的運(yùn)行狀態(tài)。3.2.5 流程導(dǎo)航器此窗口可以輕松訪問指導(dǎo)設(shè)計(jì)從開始到結(jié)束所需的工具和命令,從項(xiàng)目管理開始,包括設(shè)計(jì)輸入,在程序和調(diào)試部分中以比特流文件生成結(jié)束,仿真,綜合

2019-07-18 15:40:33

的編譯狀態(tài),以及Vivado工具的運(yùn)行狀態(tài)。3.2.5 流程導(dǎo)航器此窗口可以輕松訪問指導(dǎo)設(shè)計(jì)從開始到結(jié)束所需的工具和命令,從項(xiàng)目管理開始,包括設(shè)計(jì)輸入,在程序和調(diào)試部分中以比特流文件生成結(jié)束,仿真,綜合

2023-09-06 17:55:44

Vivado常見問題集錦目前在學(xué)習(xí)FPGA的基本知識,之前只是在數(shù)電實(shí)驗(yàn)課上簡單的寫過幾個(gè)小程序,現(xiàn)在屬于兩條腿走路,一邊做硬件一邊分出一定的時(shí)間做FPGA開發(fā)。我的開發(fā)板使用的是賽靈思旗下

2022-01-06 06:12:30

HI,我正在使用Vivado 2014.2和SDK 2014.2進(jìn)行部分重新配置的項(xiàng)目。我想使用AXIHWICAP IP執(zhí)行部分重新配置,我必須生成部分位文件。但是Vivado工具沒有部分重新配置許可證。有沒有任何方法可以生成部分位文件?謝謝,迪夫亞

2020-05-19 08:51:54

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸載過Modelsim,用vivado打開過ISE工程,因?yàn)?b class="flag-6" style="color: red">工程中很多IP核不能用所以在重新生成過程中發(fā)現(xiàn)了這個(gè)問題,還請大神告知是怎么回事?

2023-04-24 23:42:21

按照芯來官方教程使用命令make mcs 的確是可以生成mcs文件,這個(gè)文件就是helloword程序,請問如何修改makefile,將別的文件生成mcs。我的情況是將軟件編譯的.verilog文件

2023-08-12 07:39:10

helloword測試程序下載到開發(fā)板里面出現(xiàn)這種情況

2021-12-31 07:23:16

helloword測試程序下載到開發(fā)板里面出現(xiàn)這種情況Segmentation fault是為什么?

2022-01-13 06:29:20

時(shí)arm啟動失敗。兩個(gè)程序都在同一硬件環(huán)境,同一sdk工程中。如果將memery_test工程里的代碼換成hello world的代碼,則同樣能正常運(yùn)行。我總結(jié)了一下,和代碼沒關(guān)系,和硬件環(huán)境(vivado工程)沒關(guān)系,實(shí)在不清楚是哪里出問題了,還請各位能多多給點(diǎn)建議。謝謝了。

2016-12-20 12:38:45

請教一下,vivado怎么把帶ip核的工程進(jìn)行封裝,保證代碼不可見,可以通過端口調(diào)用。我嘗試了以下方法,ippackage,如果要在另一個(gè)程序里調(diào)用,也要提供源代碼;另一個(gè)方法是將網(wǎng)表文件edf文件與端口聲明結(jié)合,這種方法只能實(shí)現(xiàn)不帶ip核的封裝

2017-07-14 09:18:30

我采用的是vivado2014.2版本,使用的是下面這個(gè)代碼例程。在建立zedbord開發(fā)板例程過程中沒有問題,也能通過在硬件上的測試。但是在建立基于KC705工程的時(shí)候vivado工具總是在

2018-10-08 16:37:04

Twincat是什么?一個(gè)完整的PLC工程中包括哪些部分?

2021-09-23 07:20:38

我的有部分程序是硬體SPI程序,但是51的是模擬SPI,所以需要再硬件SPI下再加模擬SPI程序,這部分程序簡單嗎?我是初學(xué)者,不是很懂。

2016-09-08 14:56:03

28的問題的帖子。我遇到安裝問題,安裝文件安裝完成但安裝程序在生成已安裝部件列表時(shí)會掛起,安裝日志的最后一行除安裝程序試圖調(diào)用Vivado二進(jìn)制文件之外沒有顯示多少Tcl腳本生成已安裝的設(shè)備列表。嘗試

2019-01-08 10:04:15

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

一、總體流程開發(fā)工具:Vivado2020VerilogARTIX-7 FPGA AX7035這是我做的完整流程,涉及到初級開發(fā)的功能;新建工程:(RTL Project)芯片選型;編寫程序:源文件

2021-07-22 07:35:26

我想編譯自己的應(yīng)用程序在開發(fā)板上跑,看了手冊里面只寫到用Qt編譯helloword.bin然后在開發(fā)板上運(yùn)行,但是我不想用Qt,直接makefile交叉編譯要怎么操作呢

2021-12-31 07:26:31

xilinx EDF已經(jīng)綜合過的網(wǎng)表文件怎樣添加到Vivado工程中?買了一個(gè)第三方的IP,給出了端口列表和核心模塊發(fā)射機(jī)的.edf已經(jīng)綜合過的網(wǎng)表文件,該網(wǎng)表文件里面富含了大量的信息,我想知道edf文件怎樣添加到Vivado工程中去?要不然的話,總是提示核心模塊實(shí)例化失敗!

2016-09-07 11:34:10

教程分兩部分,第一部分介紹硬件FPGA程序固化,第二部分介紹嵌入式軟件程序的固化。 1、 硬件FPGA程序固化: 在生成比特流文件前,需要檢查一下,項(xiàng)目設(shè)置中Bitstream選項(xiàng)是否勾選了

2016-12-27 20:22:29

參考書上第9.1章,完成helloZynq的硬件設(shè)計(jì)部分。步驟如下1、新建工程,名字“helloZynq“,注意:工程名字及路徑不能有空格,路徑不能有中文。2、選擇RTL project,NEXT

2015-06-25 21:31:50

今天給大家分享我們VIVADO的系列教程,內(nèi)容包括:VIVADO _介紹和新建工程、VIVADO_設(shè)計(jì)輸入、VIVADO_編譯、配置管腳和下載、VIVADO_ILA介紹、VIVADO_固化程序的方法。

2022-01-07 09:40:11

從硬件管理器中的最后一個(gè)屏幕取消時(shí)(請參閱screen_cap.png圖像),Vivado 2015.1崩潰,沒有任何消息。日志文件表明它是Java的問題(請參閱hs_err_pid7988.log

2019-04-03 14:37:19

善用Vivado工程配置文件xpr快速工程創(chuàng)建對于第一次新建工程,沒啥捷徑,建議大家規(guī)規(guī)矩矩的使用Vivado的GUI創(chuàng)建工程。完成工程創(chuàng)建后,我們找到這個(gè)新建工程下的.xpr文件,它是工程配置文件

2016-10-19 18:05:13

管腳到內(nèi)部的線長也需要考慮。fpga工程師可以在vivado的Tcl Console中執(zhí)行tcl命令,生成對應(yīng)器件的trace length文件提供給硬件工程師。具體命令如下:第一個(gè)命令為鏈接具體

2022-06-17 14:52:14

和IP

1. 新建工程項(xiàng)目

1) 雙擊桌面圖標(biāo)打開Vivado 2017.2,或者選擇開始>所有程序>Xilinx Design Tools>

2023-08-15 19:57:56

、書籍、源碼、技術(shù)文檔…(2023.07.09更新)

本篇掌握基于diagram的Vivado工程設(shè)計(jì)流程,學(xué)會使用IP集成器,添加 IP 目錄并調(diào)用其中的IP。本篇實(shí)現(xiàn)了一個(gè)簡單的數(shù)字鐘

2023-08-18 21:18:47

。

操作步驟

一、基于添加文件和IP

1. 新建工程項(xiàng)目

1) 雙擊桌面圖標(biāo)打開Vivado 2017.2,或者選擇開始>所有程序>Xilinx Design

2023-08-17 19:31:54

/Vivado_2017.2 /Vivado/2017.2并試圖再次安裝。但是安裝程序不允許我使用之前的版本,并假裝仍然安裝了2017.2。必須有其他地方崩潰的安裝留下一些痕跡。問題:在如此崩潰的安裝后

2018-12-25 11:10:25

的使用。 1.按鍵硬件電路 開發(fā)板按鍵部分電路 從圖中可以看到,電路的按鍵松開時(shí)是高電平,按下時(shí)是低電平。 開發(fā)板LED部分電路 而LED部分,高電平滅,低電平亮 2. 程序設(shè)計(jì) 這個(gè)程序沒有

2021-01-06 17:48:21

如何在OpenMV4上運(yùn)行第一個(gè)HelloWord程序呢?其實(shí)驗(yàn)步驟有哪些?

2022-01-27 06:08:37

如何才能成為一個(gè)硬件工程師?

2021-11-11 07:11:12

Layout設(shè)計(jì)逐漸成為主流,本系列文章同時(shí)包含有兩部分內(nèi)容且進(jìn)行融合,歡迎大家持續(xù)關(guān)注,關(guān)注微信公眾號“硬件開發(fā)不完全攻略”。 本次更新內(nèi)容主要講述如何通過Zynq 7000在Vivado下的工程文件評估芯片的各路電源功耗(電流),電源功耗(電流)評估對于電源選型、電源平面設(shè)計(jì)、電源完整仿真評估等都有很重...

2021-11-11 06:43:44

vivado_hlsip_packagexxx.zipIP核projectsolution仿真方案srcHLS工程源碼test_benchHLS工程仿真程序或測試文件vivado_hls.appHLS工程文件HLS詳細(xì)開發(fā)說明可

2021-11-11 09:38:32

親愛的大家,我已成功更新了我的xilinx帳戶配置文件。但是當(dāng)我去下載vivado windows安裝程序時(shí),chrome會自動填寫表單作為我的個(gè)人資料。當(dāng)我點(diǎn)擊下一步時(shí),會顯示此警告。“請更正錯(cuò)誤

2020-05-27 07:17:04

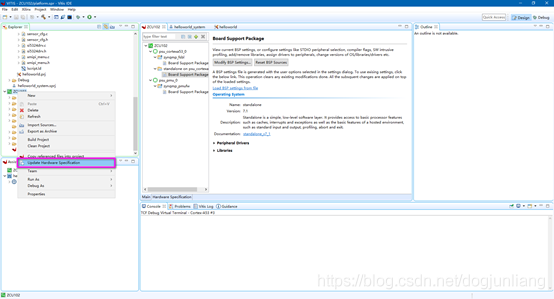

Vivado硬件平臺更新后Vitis工程如何快捷更新

2021-03-08 08:00:55

沒有 jlink仿真器,怎么給板子燒helloword程序暫時(shí)沒有仿真器

2015-09-16 11:19:41

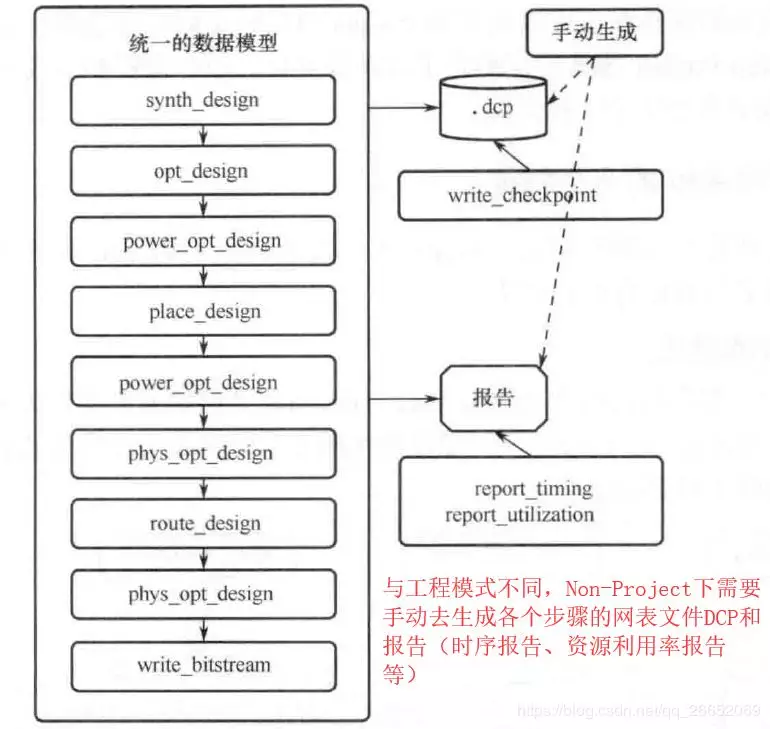

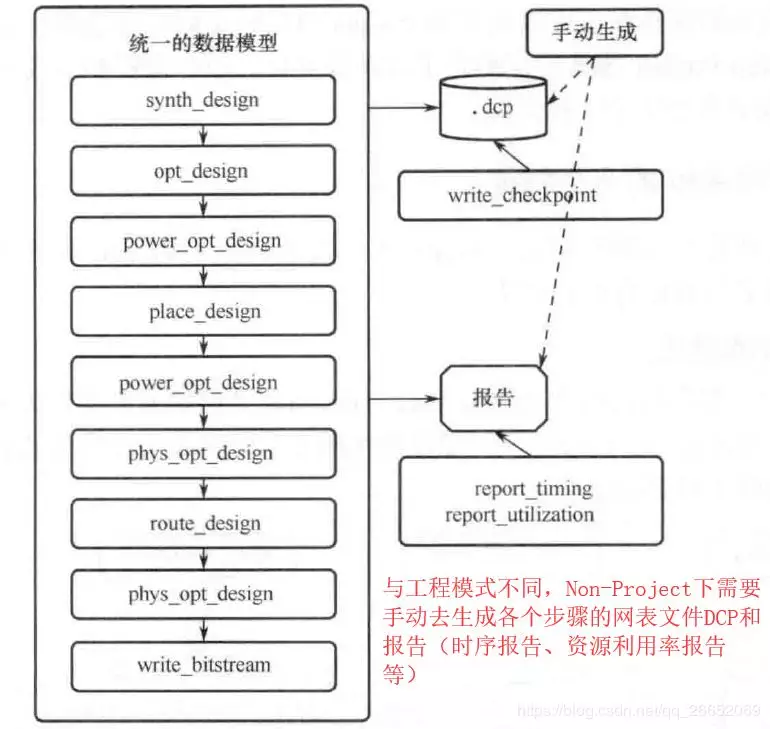

非工程模式下對應(yīng)的Tcl 命令。右圖所示是 Vivado 中設(shè)計(jì)實(shí)現(xiàn)的基本流程,藍(lán)色部分表示實(shí)現(xiàn)的基本 步驟(盡管opt_design 這一步理論上不是必選項(xiàng),但仍強(qiáng)烈建議用戶執(zhí)行),對應(yīng)

2023-06-28 19:34:58

大家好很好地更新到Windows 10已更新至Vivado 2006我的30天許可證已激活一個(gè)問題Vivado是否內(nèi)置了有線驅(qū)動程序,以便USB電纜進(jìn)行交互并上傳到項(xiàng)目板?當(dāng)我的軟件安裝時(shí),我注意到

2020-04-26 12:38:47

智能建筑設(shè)備招標(biāo)技術(shù)文件編制手冊(電氣工程部分)工程建設(shè)中設(shè)備招標(biāo)投標(biāo)制是我國建筑業(yè)和基本管理

2008-09-06 02:02:29 0

0 智能建筑設(shè)備招標(biāo)技術(shù)文件編寫手冊(電氣工程部分)共分五章,內(nèi)容有:高低壓配電設(shè)備,配電變壓器,發(fā)電機(jī)組成報(bào)警與消防聯(lián)動控制系統(tǒng),樓宇自動控制系統(tǒng),綜合布線系統(tǒng),

2008-12-24 20:23:54 0

0 硬件工程師手冊/關(guān)于硬件部分設(shè)計(jì)/單片機(jī)開發(fā)/實(shí)用開發(fā)/工程師養(yǎng)成

2016-07-12 16:05:52 0

0 本文主要詳解Vivado中新建工程或把IP搭建成原理圖,具體的跟隨小編一起來了解一下。

2018-06-30 04:51:00 12345

12345

此篇文章里,我們將通過使用InTime來檢驗(yàn)Vivado 2017.1和Vivado2016.4之間的性能對比。 概要:分別進(jìn)行了3個(gè)Vivado 2017.1對Vivado2016.4的性能測試

2018-07-04 11:23:00 9674

9674

無論此刻你是一個(gè)需要安裝Xilinx Vivado工具鏈的入門菜鳥,還是已有l(wèi)icense過期的Vivado老鐵,今兒咱就借著這篇文章,把學(xué)習(xí)「Vivado如何獲取License」這檔子事兒給說通透咯~ 手把手教程,分三部分講述。

2018-07-03 09:54:00 58889

58889

1 Vivado HLS簡介 2創(chuàng)建一個(gè)Vivado-HLS工程 2.1打開Vivado HLS GUI 2.2創(chuàng)建新工程 在 Welcome Page, 選擇Create New Project

2017-12-04 10:07:17 0

0 隨著嵌入式技術(shù)的普及,硬件工程師的性質(zhì)也有所改變。嵌入式硬件工程師與我們平常所說的硬件工程師不同。嵌入式硬件工程不但要求具備硬件工程師的基本技能,還必須完成部分軟件工程師的工作,例如: 底層驅(qū)動

2018-04-08 08:58:55 68789

68789 了解如何在Vivado中執(zhí)行工程變更單(ECO)。

本視頻將向您介紹ECO的常見用例,我們推薦的完成ECO的流程,優(yōu)勢和局限性,并將演示功能設(shè)計(jì)的ECO。

2018-11-21 06:40:00 4647

4647

本視頻介紹了UltraScale +芯片的部分重配置功能,展示了Vivado Design Suite中部分重配置的新功能,并介紹了對部分重配置的更廣泛的訪問權(quán)限

2018-11-20 06:25:00 3831

3831 物理優(yōu)化是Vivado實(shí)現(xiàn)流程中更快時(shí)序收斂的重要組成部分。

了解如何在Vivado中應(yīng)用此功能以交換運(yùn)行時(shí)以獲得更好的設(shè)計(jì)性能。

2018-11-23 06:06:00 3728

3728 了解如何使用Vivado System Generator for DSP進(jìn)行點(diǎn)對點(diǎn)以太網(wǎng)硬件協(xié)同仿真。

System Generator提供硬件協(xié)同仿真,可以將FPGA中運(yùn)行的設(shè)計(jì)直接整合到Simulink仿真中。

2018-11-23 06:02:00 4262

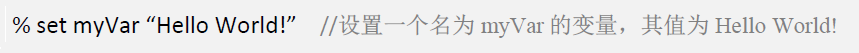

4262 實(shí)際上Tcl的功能可以很強(qiáng)大,用其編寫的程序也可以很復(fù)雜,但要在Vivado或大部分其它EDA工具中使用,則只需掌握其中最基本的幾個(gè)部分

2019-07-24 16:52:00 3179

3179

Vivado硬件平臺更新后Vitis工程如何快捷更新

2021-01-22 05:51:23 1065

1065

本文介紹如何在 vivado 開發(fā)教程(一) 創(chuàng)建新工程 的基礎(chǔ)上, 使用IP集成器, 創(chuàng)建塊設(shè)計(jì)。

2022-02-08 10:47:39 2090

2090

本文主要介紹如何使用Vivado 開發(fā)套件創(chuàng)建硬件工程。

2022-02-08 10:41:59 1012

1012

Vivado硬件平臺更新后Vitis工程如何快捷更新

2021-01-28 09:28:18 12

12 本文主要介紹如何使用Vivado 開發(fā)套件創(chuàng)建硬件工程。

2021-02-02 07:13:32 18

18 vivado搭建一個(gè)簡單PS 的工程(記得勾選uart),生成bit,導(dǎo)出硬件,啟動sdk,新建helloworld的工程就行。然后跑一下,看串口是否能打印helloworld。如果可以,這就成功搭建工程了。

2022-07-05 10:10:46 2136

2136 注意:目前這個(gè)是Micrium官網(wǎng)的最新版本,該版本支持Vivado2019.1。但測試使用的是Vivado2018.3。

2022-08-01 11:53:06 2218

2218 Vivado可以導(dǎo)出腳本,保存創(chuàng)建工程的相關(guān)命令和配置,并可以在需要的時(shí)候使用腳本重建Vivado工程。腳本通常只有KB級別大小,遠(yuǎn)遠(yuǎn)小于工程打包文件的大小,因此便于備份和版本管理。下面把前述腳本升級到Vivado 2020.2為例,討論如何升級Vivado工程腳本。

2022-08-02 10:10:17 1542

1542 一個(gè)完整的vivado工程往往需要占用較多的磁盤資源,少說幾百M(fèi),多的甚至可能達(dá)到上G,為節(jié)省硬盤資源,可以使用Tcl命令對vivado工程進(jìn)行備份,然后刪除不必要的工程文件,需要時(shí)再恢復(fù)即可。

2022-08-02 15:01:06 3696

3696 Spring+Vue工程部署在Linux

2023-01-13 14:19:54 689

689

版本遷移的操作想必大家已經(jīng)做過不少了,其中包括從ISE轉(zhuǎn)換到vivado與vivado老版本遷移到新版本。鄭智海同學(xué)給大家介紹了一下如何把工程從ISE遷移到vivado中。

2023-01-30 09:11:30 3020

3020 vivado的工程創(chuàng)建流程對于大部分初學(xué)者而言比較復(fù)雜,下面將通過這篇博客來講解詳細(xì)的vivado工程創(chuàng)建流程。幫助自己進(jìn)行學(xué)習(xí)回顧,同時(shí)希望可以對有需要的初學(xué)者產(chǎn)生幫助。

2023-07-12 09:26:57 1101

1101

電子發(fā)燒友網(wǎng)站提供《Vivado設(shè)計(jì)套件用戶:使用Vivado IDE的指南.pdf》資料免費(fèi)下載

2023-09-13 15:25:36 3

3 電子發(fā)燒友網(wǎng)站提供《Vivado Design Suite教程:嵌入式處理器硬件設(shè)計(jì).pdf》資料免費(fèi)下載

2023-09-15 10:12:33 1

1 Language,硬件描述語言),而SystemVerilog則是HDVL(Hardware Design and Verification Language,硬件設(shè)計(jì)與驗(yàn)證語言)。由此可見,SystemVerilog也是可以用于硬件設(shè)計(jì)的,也是有可綜合部分的。SystemVerilog本身由3部分構(gòu)成。

2023-10-19 11:19:19 342

342

電子發(fā)燒友App

電子發(fā)燒友App

評論