作者:Mculover666 1.實(shí)驗(yàn)?zāi)康?通過例程探索Vivado HLS設(shè)計(jì)流 用圖形用戶界面和TCL腳本兩種方式創(chuàng)建Vivado HLS項(xiàng)目 用各種HLS指令綜合接口 優(yōu)化Vivado HLS

2020-12-21 16:27:21 3153

3153 當(dāng)我們安裝好Vivado 的時(shí)候,也同時(shí)裝好了Vivado HLS.。 這是個(gè)什么東西?我就有一種想一探究的感覺。網(wǎng)上一查,Vivado High-Level Synthesis。學(xué)習(xí)了一段時(shí)間

2020-10-14 15:17:19 2881

2881

? HLS任務(wù)級(jí)編程第一篇文章可看這里: HLS之任務(wù)級(jí)并行編程 HLS的任務(wù)級(jí)并行性(Task-level Parallelism)分為兩種:一種是控制驅(qū)動(dòng)型;一種是數(shù)據(jù)驅(qū)動(dòng)型。對(duì)于控制驅(qū)動(dòng)

2023-07-27 09:22:10 732

732

該項(xiàng)目通過一個(gè)示例演示了 HLS 中組合電路對(duì)設(shè)計(jì)的影響。

2023-11-03 09:04:09 360

360

了32GB HBM2內(nèi)存和10個(gè)100GbE RoCEv2 RDMA端口。

HLS-1H接口為2x16 PCle Gen4,可連接到外部主機(jī)服務(wù)器,以及多達(dá)40×100Gb以太網(wǎng)鏈路(使用10QSFP DD

2023-08-04 06:06:14

請(qǐng)教一下,我在HLS里面要將以下程序生成IP核,C Synthesis已經(jīng)做好了,但是在export RTL的時(shí)候一直在運(yùn)行

int sum_single(int A int B

2023-09-28 06:03:53

HLS高階綜合(highlevelsynthesis)在被廣泛使用之前,作為商業(yè)技術(shù)其實(shí)已經(jīng)存在了20多年。設(shè)計(jì)團(tuán)隊(duì)對(duì)于這項(xiàng)技術(shù)可以說呈現(xiàn)出兩極化的態(tài)度:要么堅(jiān)信它是先進(jìn)技術(shù)之翹楚,要么對(duì)其持謹(jǐn)慎

2021-07-10 08:00:00

, int n, int o){

for(int i = 2; i >= 0; i--){

#pragma HLS pipeline ii = 1

op_Read;

op_Compute

2023-12-31 21:20:08

1、HLS最全知識(shí)庫介紹高層次綜合(High-level Synthesis)簡稱HLS,指的是將高層次語言描述的邏輯結(jié)構(gòu),自動(dòng)轉(zhuǎn)換成低抽象級(jí)語言描述的電路模型的過程。對(duì)于AMD Xilinx而言

2022-09-07 15:21:54

,openCV允許用戶定義自己的原點(diǎn)設(shè)置。取值0表示原點(diǎn)位于圖片左上角,1表示左下角。1.4 VivadoHLS中圖像數(shù)據(jù)類型hls::Mat《》VivadoHLS視頻處理函數(shù)庫使用hls::Mat

2021-07-08 08:30:00

我在Vivado HLS中有以下錯(cuò)誤的合成。我試圖更新許可證文件但沒有成功。請(qǐng)給我一個(gè)建議。@E [HLS-72]許可證簽出不成功。確保可以訪問許可證或通過環(huán)境變量指定適當(dāng)?shù)脑S可證。 執(zhí)行

2020-05-20 09:13:21

1.實(shí)驗(yàn)?zāi)康耐ㄟ^例程探索Vivado HLS設(shè)計(jì)流用圖形用戶界面和TCL腳本兩種方式創(chuàng)建Vivado HLS項(xiàng)目用各種HLS指令綜合接口優(yōu)化Vivado HLS設(shè)計(jì)來滿足各種約束用不用的指令來探索

2021-11-11 07:09:49

本帖最后由 FindSpace博客 于 2017-4-19 16:57 編輯

在c simulation時(shí),如果使用gcc編譯器報(bào)錯(cuò):/home/find/d/fpga/Vivado_HLS

2017-04-19 16:56:06

vivado可以正常使用,但是HLS總是出現(xiàn)圖片中的錯(cuò)誤。請(qǐng)問該如何解決?謝謝!

2020-08-12 01:36:19

你好!如果我想使用vivado hls來合成具有axi流接口的代碼,是否有必須遵循的標(biāo)準(zhǔn)編碼風(fēng)格?

2020-04-21 10:23:47

HLS高階綜合(highlevelsynthesis)在被廣泛使用之前,作為商業(yè)技術(shù)其實(shí)已經(jīng)存在了20多年。設(shè)計(jì)團(tuán)隊(duì)對(duì)于這項(xiàng)技術(shù)可以說呈現(xiàn)出兩極化的態(tài)度:要么堅(jiān)信它是先進(jìn)技術(shù)之翹楚,要么對(duì)其持謹(jǐn)慎

2021-07-06 08:00:00

了。1.5HLS庫Vivado HLS中包含了一系列的C庫(包括C和C++),方便對(duì)一些常用的硬件結(jié)構(gòu)或功能使用C/C++進(jìn)行建模,并且能夠綜合成RTL。在Vivado HLS中提供的C庫有下面幾種類型:1

2020-10-10 16:44:42

設(shè)計(jì)的綜合。Vivado High Level Synthesis(即HLS,高層次綜合)工具使用C、C++或System C語言在更抽象的算法層次描述設(shè)計(jì),并將C代碼綜合成RTL級(jí)的HDL描述

2020-10-10 16:48:25

【資料分享】Vivado HLS學(xué)習(xí)資料

2013-11-02 11:21:14

1、使用Vitis HLS創(chuàng)建屬于自己的IP高層次綜合(High-level Synthesis)簡稱HLS,指的是將高層次語言描述的邏輯結(jié)構(gòu),自動(dòng)轉(zhuǎn)換成低抽象級(jí)語言描述的電路模型的過程。對(duì)于AMD

2022-09-09 16:45:27

ap_int out_t;int factorial(in1_t N);萬一源文件包括“factorial.h”int factorial(in1_t N){pragma HLS INTERFACE

2020-05-21 13:58:09

嗨,大家好,我有一個(gè)問題,在VIVADO HLS 2017.1中運(yùn)行C \ RTL協(xié)同仿真。我已成功運(yùn)行2014和2016版本的代碼。任何人都可以告訴我為什么報(bào)告NA僅用于間隔

2020-05-22 15:59:30

Vivado 2017.4、Xilinx VivadoHLS 2017.4、Xilinx SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高層次綜合)工具支持

2021-02-19 18:36:48

你好,我使用Vivado HLS生成了一個(gè)IP。從HLS測量的執(zhí)行和測量的執(zhí)行時(shí)間實(shí)際上顯著不同。由HLS計(jì)算的執(zhí)行非常小(0.14 ms),但是當(dāng)我使用AXI計(jì)時(shí)器在真實(shí)場景中測量它時(shí),顯示3.20 ms。為什么會(huì)有這么多差異? HLS沒有告訴實(shí)際執(zhí)行時(shí)間?等待回復(fù)。問候

2020-05-05 08:01:29

嗨? 如何在HLS 14.3中編寫pow功能? HLS 14.3不支持exp和pow功能。我在我的代碼中寫了“#include math.h”。但是,它不起作用。 另外,我想知道C代碼中

2019-03-05 13:40:09

目 錄4 matrix_demo 案例 274.1 HLS 工程說明 274.2 編譯與仿真 304.3 綜合 314.4 IP 核測試 364.4.1 PL 端 IP 核測試 Vivado 工程

2023-01-01 23:50:04

目 錄4 matrix_demo 案例 274.1 HLS 工程說明 274.2 編譯與仿真 304.3 綜合 314.4 IP 核測試 364.4.1 PL 端 IP 核測試 Vivado 工程

2023-08-24 14:52:17

產(chǎn)品上市時(shí)間。

HLS 基本開發(fā)流程如下:(1) HLS 工程新建/工程導(dǎo)入(2) 編譯與仿真(3) 綜合(4) IP 核封裝(5) IP 核測試測試板卡是基于創(chuàng)龍科技Xilinx Zynq-7000

2023-08-24 14:54:01

產(chǎn)品上市時(shí)間。HLS 基本開發(fā)流程如下:(1) HLS 工程新建/工程導(dǎo)入(2) 編譯與仿真(3) 綜合(4) IP 核封裝(5) IP 核測試測試板卡是基于創(chuàng)龍科技Xilinx Zynq-7000系列

2023-01-01 23:46:20

。

Xilinx Vivado HLS (High-Level Synthesis,高層次綜合) 工具支持將 C 、C++等語言轉(zhuǎn)化成硬件描述語言,同時(shí)支持基于 OpenCL 等框架對(duì) Xilinx

2023-08-24 14:40:42

。Xilinx Vivado HLS (High-Level Synthesis,高層次綜合) 工具支持將 C 、C++等語言轉(zhuǎn)化成硬件描述語言,同時(shí)支持基于 OpenCL 等框架對(duì) Xilinx

2023-01-01 23:52:54

SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高層次綜合)工具支持將C、C++等語言轉(zhuǎn)化成硬件描述語言,同時(shí)支持基于OpenCL等框架

2021-11-11 09:38:32

新思科技公司(Synopsys)目前推出該公司最新研發(fā)的Synphony HLS (High Level Synthesis)解決方案。該解決方案集成了M語言和基于模型的綜合法,與 傳統(tǒng)RTL流程

2019-08-13 08:21:49

我照著xapp1167文檔,用HLS實(shí)現(xiàn)fast_corners的opencv算法,并生成IP。然后想把這個(gè)算法塞到第三季的CH05_AXI_DMA_OV5640_HDMI上,這個(gè)demo里

2017-01-16 09:22:25

您好我有一個(gè)關(guān)于vivado hls的問題。RTL是否來自xivix FPGA的vivado hls onyl?我們可以在Design Compiler上使用它進(jìn)行綜合嗎?謝謝

2020-04-13 09:12:32

SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高層次綜合)工具支持將C、C++等語言轉(zhuǎn)化成硬件描述語言,同時(shí)支持基于OpenCL等框架

2021-11-11 15:54:48

的結(jié)果(0 LUT,0 REGISTERS,...)問題是什么? Vivado HLS不會(huì)合成這個(gè)特殊聲明嗎?我附上兩個(gè)文件:proof.cpp和“利用率估算”的屏幕截圖proof.cpp 1 KB

2019-11-05 08:21:53

嗨伙計(jì),在我的PC Vivado設(shè)計(jì)套件2015.2和SDK 2015.2工作,但只有vivado HLS 2015.2沒有打開,這就是為什么我想重新安裝Vivado HLS 2015.2。如何下載

2018-12-27 10:57:49

描述 HLS系列霍爾效應(yīng)液位傳感器(HLS)是用于連續(xù)液位監(jiān)測的定制設(shè)計(jì)解決方案,適用溫度范圍寬廣,可校準(zhǔn)定制編程輸出以適應(yīng)各種幾何形狀的液位儲(chǔ)存箱。HLS系列是一款智能傳感器,帶有板載

2021-07-14 14:08:24

Synopsys天宣布推出其Synphony HLS (High Level Synthesis)解決方案

新思科技公司,今天宣布推出其Synphony HLS (High Level Synthesis)解決方案。該解決方案集成了M語言和基于模型的綜合

2009-11-04 16:55:53 962

962 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高層次綜合 (HLS) 進(jìn)行 FPGA 設(shè)計(jì)的簡介

2016-01-06 11:32:55 65

65 高層次綜合設(shè)計(jì)最常見的的使用就是為CPU創(chuàng)建一個(gè)加速器,將在CPU中執(zhí)行的代碼移動(dòng)到FPGA可編程邏輯去提高性能。本文展示了如何在Zynq AP SoC設(shè)計(jì)中使用HLS IP。 在Zynq器件

2017-02-07 18:08:11 3207

3207

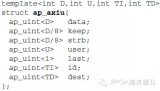

: 數(shù)組通常都被綜合成ap_memory端口,它用來同外部的RAM或者ROM進(jìn)行數(shù)據(jù)交互,并且?guī)в械刂沸盘?hào),意味著對(duì)數(shù)據(jù)的存取順序可以隨機(jī)/任意。如果對(duì)外部存儲(chǔ)資源的訪問是順序的,那么可以考慮ap_fifo端口,它用來同F(xiàn)IFO進(jìn)行通信,不

2017-02-08 02:42:41 801

801

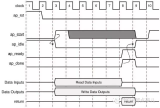

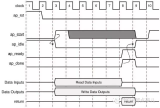

Burst): 如下的代碼,在綜合時(shí)若設(shè)置端口d用ap_bus實(shí)現(xiàn),那么就會(huì)生成ap_bus的standard mode,它每次只發(fā)起single read/write(右邊是其綜合后的端口): Single Read的時(shí)序圖: d_rsp

2017-02-08 02:46:31 322

322

繼續(xù)HLS的基本概念。 1、DataFlow的概念,以及Dataflow和Pipeline的區(qū)別 如下所示的圖像處理過程,數(shù)據(jù)處理由2個(gè)濾波器構(gòu)成: 默認(rèn)情況下,HLS會(huì)遵循c邏輯中的先后順序,依次

2017-02-08 03:20:41 622

622

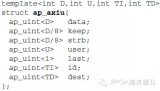

在上一章HLS的端口綜合里有提及,HLS綜合后的端口分為2中類型:BlockLevel和Port Level Interface。其中Port level是我們需要重點(diǎn)關(guān)注的,它又可以細(xì)分為4中類型

2017-02-08 03:27:11 475

475

在上一章HLS提到了axi lite端口的綜合方式,以及directive的一些語法規(guī)則。這一章里面,介紹一下axi-stream和full axi端口的綜合實(shí)現(xiàn)問題。 1. AXI-Stream

2017-02-08 03:31:04 414

414

在上一章HLS提到了axi lite端口的綜合方式,以及directive的一些語法規(guī)則。這一章里面,介紹一下axi-stream和full axi端口的綜合實(shí)現(xiàn)問題。 AXI FULL端口的實(shí)現(xiàn)

2017-02-08 03:35:34 776

776

在之前的3章里,著重講解了HLS對(duì)AXI端口(包括axi-lite,axi-stream和full axi端口)的綜合實(shí)現(xiàn)問題,下面讓我們來介紹一下其它的端口類型是如何實(shí)現(xiàn)的。 在開始之前,先來

2017-02-08 03:39:11 354

354

下面先介紹下No I/OProtocol ap_none: ap_none是HLS最簡單的一種接口協(xié)議類型,不論是input還是output端口,綜合后都不附帶額外的控制信號(hào),在rtl里面所呈現(xiàn)的唯一端口

2017-02-08 03:45:02 500

500

眾所周知,HLS是Xilinx于幾年前推出的一個(gè)高級(jí)綜合工具,可以直接把C/C++代碼,轉(zhuǎn)換成可綜合的verilog/VHDL代碼。聽起來很高級(jí),是不是?。但看新鮮的人多,愿意吃螃蟹的人卻很少。這里

2017-02-08 05:07:20 1183

1183

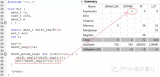

在這個(gè)系列的上一篇文章“HighLevel Synthesis(HLS) 從一個(gè)最簡單的fir濾波器開始1”中,我們從一個(gè)最簡單的FIR濾波器,介紹了HLS是如何把C映射成RTL代碼的一些基本細(xì)節(jié)

2017-02-08 05:10:34 349

349 在上一章“High LevelSynthesis(HLS) 從一個(gè)最簡單的fir濾波器開始2”中,我們通過修改c的頭文件里面的類型精度定義,把DSP48E的消耗數(shù)量從8個(gè)壓縮到了2個(gè): 但這個(gè)結(jié)果

2017-02-08 05:11:11 341

341

在這個(gè)系列的前3篇文章“HighLevel Synthesis(HLS) 從一個(gè)最簡單的fir濾波器開始1-3”中,我們從一個(gè)最簡單的FIR濾波器,一步步優(yōu)化,得到了一個(gè)比較理想的HLS綜合結(jié)果

2017-02-08 05:13:37 983

983

在這個(gè)系列的前4篇文章“HighLevel Synthesis(HLS) 從一個(gè)最簡單的fir濾波器開始1-4”中,我們從一個(gè)最簡單的FIR濾波器,一步步優(yōu)化,得到了一個(gè)資源和Latency都比

2017-02-08 05:18:11 456

456

)和VHDL(2000),綜合過程中,一般還需要特定的directives(約束腳本)來控制綜合結(jié)果。 HLS對(duì)標(biāo)準(zhǔn)C基本都支持,除了以下4個(gè)特例: a)System Calls系統(tǒng)調(diào)用,比如printf

2017-02-08 05:23:11 674

674

1. HLS僅支持一個(gè)主時(shí)鐘和復(fù)位 因此,目前還沒有辦法完全用HLS做出一個(gè)多時(shí)鐘域的設(shè)計(jì)。 2. 對(duì)于同一個(gè)參數(shù),HLS可以綜合出各種各樣的端口類型 這也需要額外的約束去進(jìn)行設(shè)置 3. 雖然

2017-02-08 05:24:31 271

271

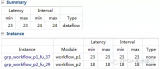

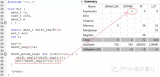

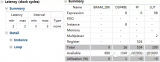

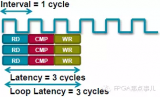

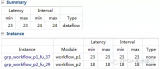

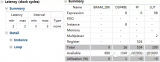

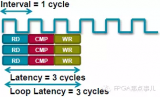

繼續(xù)HLS的基本概念。 Latency 和 Interval(II)的區(qū)別 當(dāng)HLS綜合完后,在performance報(bào)告中,會(huì)看到這2個(gè)指標(biāo),它們都跟性能相關(guān)。那么這兩個(gè)參數(shù)的區(qū)別和含義具體

2017-02-08 05:28:12 708

708

HLS工具 以個(gè)人的理解,xilinx將HLS(高層次綜合)定位于更方便的將復(fù)雜算法轉(zhuǎn)化為硬件語言,通過添加某些配置條件HLS工具可以把可并行化的C/C++的代碼轉(zhuǎn)化為vhdl或verilog,相比于純?nèi)斯な褂胿hdl實(shí)現(xiàn)圖像算法,該工具綜合出的代碼的硬件資源占用可能較多。

2019-10-12 17:34:00 1961

1961

,Xilinx Vivado HLS是一個(gè)高級(jí)綜合工具,能夠?qū)語言轉(zhuǎn)換成硬件描述語言(HDL),也就是說我們可以用C語言來實(shí)現(xiàn)HDL模塊編程了。 圖1 Vivado HLS工作流程 第一位Hacker

2017-02-08 20:01:59 550

550

窗口中,鍵入:vivado_hls -p fir_prj在vivado用戶界面打開工程,Vivado HLS打開,如下圖所示。方案1的綜合已經(jīng)完

2017-02-09 05:07:11 411

411

高層次綜合(High Level Synthesis, HLS)是Xilinx公司推出的最新一代的FPGA設(shè)計(jì)工具,它能讓用戶通過編寫C/C++等高級(jí)語言代碼實(shí)現(xiàn)RTL級(jí)的硬件功能。隨著這款工具

2018-07-14 06:42:00 5868

5868 在特定圖像處理硬件設(shè)計(jì)中成功運(yùn)用 High-Level Synthesis (HLS) 和 High-Level Verification (HLV) 數(shù)年之后, Qualcomm 認(rèn)識(shí)到了 HLS

2017-09-11 11:37:38 9

9 1 Vivado HLS簡介 2創(chuàng)建一個(gè)Vivado-HLS工程 2.1打開Vivado HLS GUI 2.2創(chuàng)建新工程 在 Welcome Page, 選擇Create New Project

2017-12-04 10:07:17 0

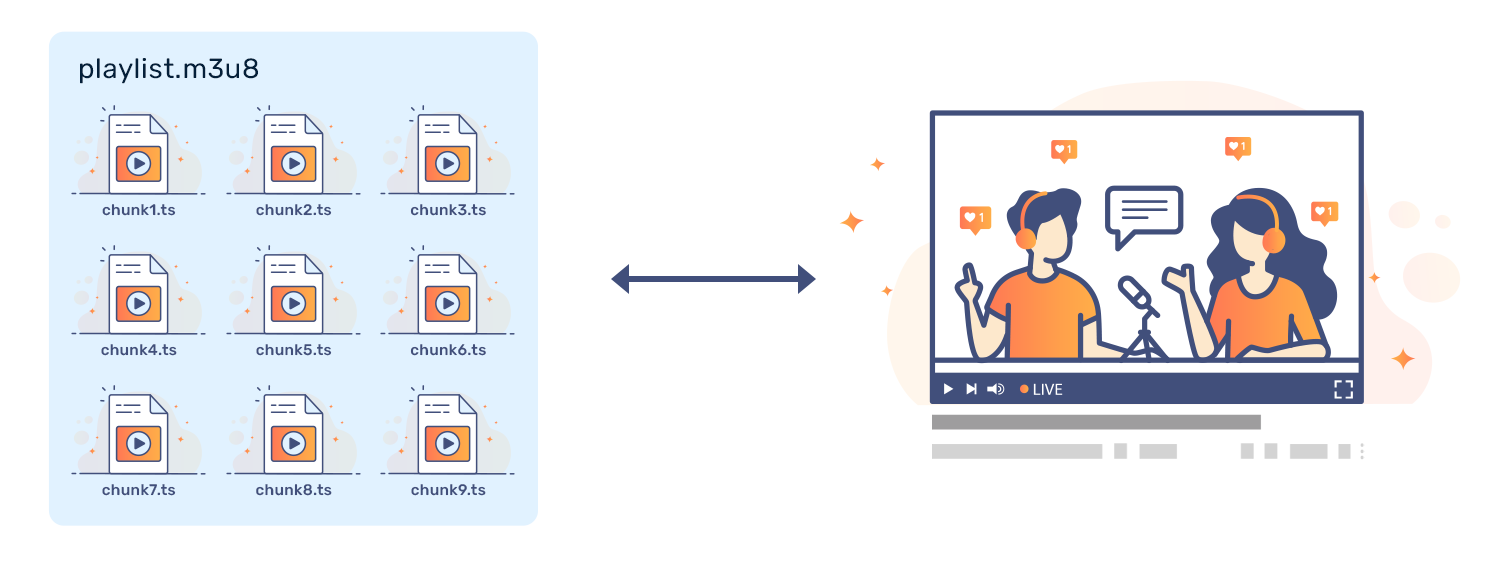

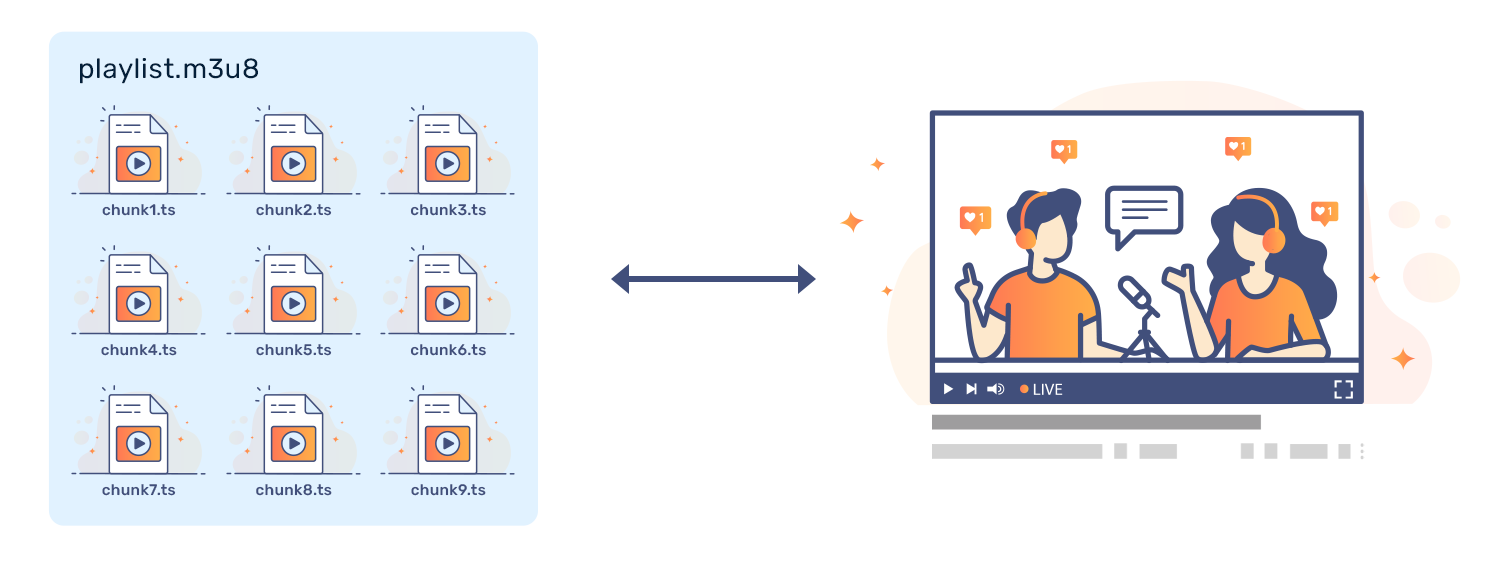

0 摘要:HTTP Live Streaming(縮寫是HLS)是一個(gè)由蘋果公司提出的基于HTTP的流媒體網(wǎng)絡(luò)傳輸協(xié)議。今天主要以HLS協(xié)議為中心講述它的一些原理。

2017-12-10 09:25:37 54718

54718 本文內(nèi)容介紹了基于用Vivado-HLS為軟件提速,供參考

2018-03-26 16:09:10 7

7 HLS,高層綜合)。這個(gè)工具直接使用C、C++或SystemC 開發(fā)的高層描述來綜合數(shù)字硬件,這樣就不再需要人工做出用于硬件的設(shè)計(jì),像是VHDL 或Verilog 這樣的文件,而是由HLS 工具來做這個(gè)事情。

2018-06-04 01:43:00 7171

7171

Achronix的Speedcore系列eFPGA可得到Catapult HLS的全面支持。

Catapult HLS為FPGA流程提供集成化設(shè)計(jì)與開發(fā)環(huán)境,率先支持5G無線應(yīng)用。

2018-08-30 10:09:32 7368

7368 接著開始正文。據(jù)觀察,HLS的發(fā)展呈現(xiàn)愈演愈烈的趨勢,隨著Xilinx Vivado HLS的推出,intel也快馬加鞭的推出了其HLS工具。HLS可以在一定程度上降低FPGA的入門門檻(不用編寫

2019-07-31 09:45:17 6232

6232

HLS高階綜合(high level synthesis)在被廣泛使用之前,作為商業(yè)技術(shù)其實(shí)已經(jīng)存在了20多年。設(shè)計(jì)團(tuán)隊(duì)對(duì)于這項(xiàng)技術(shù)可以說呈現(xiàn)出兩極化的態(tài)度:要么堅(jiān)信它是先進(jìn)技術(shù)之翹楚,要么對(duì)其持謹(jǐn)慎懷疑態(tài)度。

2020-11-04 13:45:03 3035

3035 Vivado HLS 2020.1將是Vivado HLS的最后一個(gè)版本,取而代之的是VitisHLS。那么兩者之間有什么區(qū)別呢? Default User Control Settings

2020-11-05 17:43:16 37066

37066 <!--<img src="ams"-->HLS442_HLS440P_HPS100 (issued 2017-Apr)

2021-02-04 07:06:06 8

8 1.實(shí)驗(yàn)?zāi)康耐ㄟ^例程探索Vivado HLS設(shè)計(jì)流用圖形用戶界面和TCL腳本兩種方式創(chuàng)建Vivado HLS項(xiàng)目用各種HLS指令綜合接口優(yōu)化Vivado HLS設(shè)計(jì)來滿足各種約束用不用的指令來探索

2021-11-06 09:20:58 6

6 gitee-monitor-rtsp-hls.zip

2022-05-07 11:06:57 4

4 Vitis HLS 是一種高層次綜合工具,支持將 C、C++ 和 OpenCL 函數(shù)硬連線到器件邏輯互連結(jié)構(gòu)和 RAM/DSP 塊上。Vitis HLS 可在Vitis 應(yīng)用加速開發(fā)流程中實(shí)現(xiàn)硬件

2022-05-25 09:43:36 1930

1930 對(duì)于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統(tǒng)一將HLS集成到Vitis里了,集成之后增加了一些功能,同時(shí)將這部分開源出來了。Vitis HLS是Vitis AI重要組成部分,所以我們將重點(diǎn)介紹Vitis HLS。

2022-09-02 09:06:23 2857

2857 vivado本身集成了opencv庫以及hls視頻庫了,opencv不能被綜合導(dǎo)出為RTL電路,hls視頻庫的功能有所欠缺,因此引入xfopencv作為既可以被綜合導(dǎo)出為RTL電路,也能夠?qū)崿F(xiàn)opencv豐富的功能。

2022-09-09 15:07:05 997

997 1、HLS簡介 HLS(High-Level Synthesis)高層綜合,就是將 C/C++的功能用 RTL 來實(shí)現(xiàn),將 FPGA 的組件在一個(gè)軟件環(huán)境中來開發(fā),這個(gè)模塊的功能驗(yàn)證在軟件環(huán)境

2022-12-02 12:30:02 2571

2571 對(duì)于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統(tǒng)一將HLS集成到Vitis里了,集成之后增加了一些功能,同時(shí)將這部分開源出來了。Vitis HLS是Vitis AI重要組成部分,所以我們將重點(diǎn)介紹Vitis HLS。

2023-01-15 11:27:49 1317

1317 HLS ?(high-level synthesis)稱為高級(jí)綜合, 它的主要功能是用 C/C++為 FPGA開發(fā) 算法。這將提升FPGA 算法開發(fā)的生產(chǎn)力。 ?? Xilinx 最新的HLS

2023-01-15 12:10:04 2968

2968 HLS,Http Live Streaming 是由Apple公司定義的用于實(shí)時(shí)流傳輸?shù)膮f(xié)議,HLS基于HTTP協(xié)議實(shí)現(xiàn),傳輸內(nèi)容包括兩部分,一是M3U8描述文件,二是TS媒體文件。

2023-04-06 09:29:50 428

428 AMD Vitis HLS 工具允許用戶通過將 C/C++ 函數(shù)綜合成 RTL,輕松創(chuàng)建復(fù)雜的 FPGA 算法。Vitis HLS 工具與 Vivado Design Suite(用于綜合、布置和布線)及 Vitis 統(tǒng)一軟件平臺(tái)(用于所有異構(gòu)系統(tǒng)設(shè)計(jì)和應(yīng)用)高度集成。

2023-04-23 10:41:01 652

652

Xilinx平臺(tái)的Vivado HLS 和 Vitis HLS 使用的 export_ip 命令會(huì)無法導(dǎo)出 IP

2023-07-07 14:14:57 338

338

在HLS中用C語言實(shí)現(xiàn)8192點(diǎn)FFT,經(jīng)過測試,實(shí)驗(yàn)結(jié)果正確,但是時(shí)序約束不到100M的時(shí)鐘,應(yīng)該是設(shè)計(jì)上的延時(shí)之類的比較大,暫時(shí)放棄這個(gè)方案,調(diào)用HLS中自帶的FFT庫(hls:fft

2023-07-11 10:05:35 580

580

電子發(fā)燒友網(wǎng)站提供《Vitis HLS移植指南.pdf》資料免費(fèi)下載

2023-09-13 09:21:12 0

0 電子發(fā)燒友網(wǎng)站提供《將VIVADO HLS設(shè)計(jì)移植到CATAPULT HLS平臺(tái).pdf》資料免費(fèi)下載

2023-09-13 09:12:46 2

2 -自適應(yīng)流- HTTP) HLS(HTTP- Live-流) 兩種協(xié)議的工作方式相似——數(shù)據(jù)被編碼(分割)成塊并發(fā)送到客戶端進(jìn)行查看。 一、HLS(HTTP直播) HLS(即HTTP Live

2023-10-09 17:16:54 485

485

。XilinxVivadoHLS(High-LevelSynthesis,高層次綜合)工具支持將C、C++等語言轉(zhuǎn)化成硬件描述語言,同時(shí)支持基于OpenCL等框架對(duì)Xilinx可編程邏輯器件進(jìn)行開發(fā),可

2023-01-03 15:47:38 7

7 電子發(fā)燒友網(wǎng)站提供《使用Vivado高層次綜合(HLS)進(jìn)行FPGA設(shè)計(jì)的簡介.pdf》資料免費(fèi)下載

2023-11-16 09:33:36 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論