作者:Mculover666 1.實驗目的 通過例程探索Vivado HLS設計流 用圖形用戶界面和TCL腳本兩種方式創建Vivado HLS項目 用各種HLS指令綜合接口 優化Vivado HLS

2020-12-21 16:27:21 3153

3153 當我們安裝好Vivado 的時候,也同時裝好了Vivado HLS.。 這是個什么東西?我就有一種想一探究的感覺。網上一查,Vivado High-Level Synthesis。學習了一段時間

2020-10-14 15:17:19 2881

2881

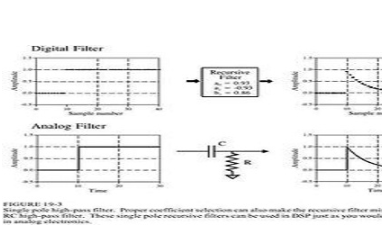

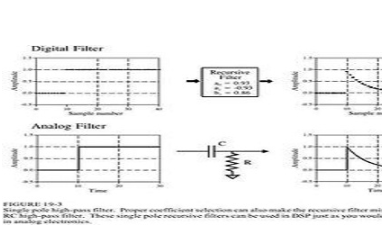

169數字FIR濾波器

2010-04-07 14:44:08

的系數來實現。(如果需要,FIR濾波器的總的增益可以在輸出調整)。當使用定點DSP的時候,這也是一個考慮因素,它能使得實現更加地簡單。 7、 相較于IIR濾波器, FIR濾波器的缺點是什么,相比較于

2011-09-24 16:05:53

本帖最后由 xie0517 于 2016-8-8 08:52 編輯

FIR是有限沖擊響應;IIR是無限沖擊響應。 FIR和IIR濾波器的一個主要區別:FIR是線性相位,IIR為非線性

2016-08-08 08:49:32

FIR和IIR濾波器的一個主要區別:FIR是線性相位,IIR為非線性相位(雙線性變換法),對于非線性相位會造成的影響,可以這樣考慮:對于輸入的不同頻率分量,造成的相位差與頻率不成正比,則輸出

2018-03-12 13:21:07

濾波;IIR需要等待上一個信號的濾波輸出,存在一定的時間延遲,所以處理速度上沒有FIR快。圖6 FIR和IIR濾波對比圖從上面的簡單比較可以看到IIR與FIR濾波器各有所長,所以在實際應用時應該從多方面

2019-06-27 04:20:31

我在長度為2500的信號上執行46階FIR低通濾波器;在16 MIPS下使用PIC24FJ256GB206。所有的值都是浮動的。使用該鏈路實現算法。目前,正在執行2.76秒來執行對我的應用程序不可

2019-10-17 06:28:21

FIR濾波器的實現方法有哪幾種?基于Verilog HDL的FIR數字濾波器設計與仿真

2021-04-09 06:02:50

數字濾波器的類型有FIR(有限長沖擊與IIR(無限長。離散數字系統中,濾波器的表述為差分方程。FIRFIR基本特性:FIR 濾波器永遠是穩定的(系統只有零點);FIR 濾波器的沖激響應是有限長序列

2021-08-17 06:19:17

。首先數據經過18個點FIR濾波器,這個濾波器系數是根據不同空間環境總結出來,這里提供一份18抽樣點做參考,它是模擬波士頓交響樂演播廳得到的。然后會經過6個低通的梳妝濾波器,最后在經過1個全通濾波器。二、回音echo效果。echo效果結構較為簡單,只是需要較多的內存存放數據,結構如下。decay為衰

2021-08-17 09:24:44

請教一下,我在HLS里面要將以下程序生成IP核,C Synthesis已經做好了,但是在export RTL的時候一直在運行

int sum_single(int A int B

2023-09-28 06:03:53

對于fir濾波器,已經在前面的文章中記錄了仿制DIY&關于MATLAB中濾波器設計工具的使用心得記錄),其設計和實現都非常簡單。如果在嵌入式系統中可以滿足且有必要實時iir運算,那么

2021-12-22 08:29:40

最近在做一個FPGA的課程設計,遇到一個比較煩人的問題,希望大神們可以指點迷律。一個16階的FIR濾波器,采用分布式算法實現的,采樣率1M,fc=100K,頻率到了30K以上時就會出現那些尖刺,很

2018-02-25 19:25:50

就說明,要增加DSP的計算量。DSP需要更多的計算時間,對DSP的實時性有影響。 以下都是低通濾波器的設計。 FIR的設計: FIR濾波器的設計比較簡單,就是要設計一個數字濾波器去逼近一個理想

2019-09-29 14:06:31

1、HLS最全知識庫介紹高層次綜合(High-level Synthesis)簡稱HLS,指的是將高層次語言描述的邏輯結構,自動轉換成低抽象級語言描述的電路模型的過程。對于AMD Xilinx而言

2022-09-07 15:21:54

,它具有線性相位、容易設計的優點。這也就說明,IIR濾波器具有相位不線性,不容易設計的缺點。而另一方面,IIR卻擁有FIR所不具有的缺點,那就是設計同樣參數的濾波器,FIR比IIR需要更多的參數。這也就說明,要增加DSP的計算量。DSP需要更多的計算時間,對DSP的實時性有影響。以下都是低通濾波器的設計。

2019-06-26 06:15:35

像素訪問對應方法2.3 用HLS實現OpenCV應用的實例(快速角點濾波器image_filter)我們通過快速角點的例子,說明通常用VivadoHLS實現OpenCV的流程。首先,開發

2021-07-08 08:30:00

多個HLS解決方案2.實驗內容實驗中文件中包含一個矩陣乘法器的實現,實現兩個矩陣inA和inB相乘得出結果,并且提供了一個包含了計算結果的testbench文件來與所得結果進行對比驗證。...

2021-11-11 07:09:49

問題 1:如何利用labview來設計一個升余弦FIR濾波器問題2:labview中digital filter toolkit是個怎么回事?我看了一些英文的書里,經常介紹這個,但是我安裝的版本里沒有。

2014-01-16 17:01:20

不同的編譯器,Xilinx Vivado High-Level Synthesis(高層綜合,HLS)工具同樣是一種編譯器,只不過它是用來將C或者C++程序部署到FPGA上,而不是部署到傳統的處理器上。在

2020-10-10 16:44:42

,形成了圖像的主要邊緣結構;高頻信息形成了圖像的邊緣和細節,是在中頻信息上對圖像內容的進一步強化。我們也可以通過空間濾波器(也稱為空間掩模、模板或窗口)直接作用于圖像本身而對圖像進行濾波處理。空間濾波器

2020-10-16 16:22:38

結構。本案例實現了具有線性相位的半串行結構的FIR濾波器。所謂串行結構,即串行實現濾波器的累加運算,將每級延時單元與相應系數的乘積結果進行累加后輸出,因此整個濾波器實際上只需要一個乘法器運算單元。串行

2017-04-14 15:20:31

FIR濾波器如何定義?為什么要使用FIR濾波器?

2021-04-06 07:48:45

。HLS 采用 C 和 C++ 描述并將它們轉換為自定義硬件 IP,完成后我們就可以在 Vivado 項目中使用該IP。Vitis HLS創建一個新的 HLS 項目:通過從Linux 終端鍵入 vitis_hls 或從 Windows 開始菜單運行HLS。原作者:碎思思

2022-09-09 16:45:27

最近進行FPGA學習,使用FIR濾波器過程中出現以下問題:使用FIR濾波器IP核中,輸入數據為1~256,濾波器系數為,coef =-1469,-14299 ,-2185,10587

2018-11-02 17:17:57

FIR濾波器的原理是什么?基于DSP Builder的FIR濾波器該如何去設計?

2021-06-02 06:26:02

脈沖響應(ⅡR)濾波器和有限長單位脈沖響應(FIR)濾波器兩種,其中,FIR濾波器能提供理想的線性相位響應,在整個頻帶上獲得常數群時延從而得到零失真輸出信號,同時它可以采用十分簡單的算法實現,這兩個

2019-08-30 07:18:39

:文章設計了一種基于TI 公司的DSP(TMS320VC5402)的FIR 數字濾波器系統。主要包括了DSP 最小系統電路設計、AD 和DA 轉換接口電路設計,并給出了系統初始化程序設計和FIR 程序設計

2008-05-14 23:30:12

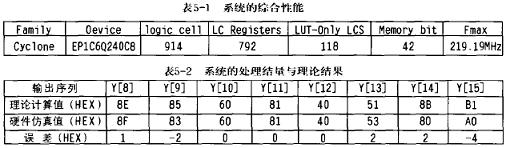

DSPBuilder設計了一個4階FIR濾波器,并用QuartusII進行硬件仿真,仿真結果表明設計FIR濾波器的正確性。同時使用IPCore開發基于FPGA的FIR數字濾波器,利用現有的IPCore在FPGA器件上實現濾波器設計。

2012-08-11 15:32:34

你好,我使用Vivado HLS生成了一個IP。從HLS測量的執行和測量的執行時間實際上顯著不同。由HLS計算的執行非常小(0.14 ms),但是當我使用AXI計時器在真實場景中測量它時,顯示3.20 ms。為什么會有這么多差異? HLS沒有告訴實際執行時間?等待回復。問候

2020-05-05 08:01:29

FIR數字濾波器的基本特性有哪些?如何利用stm32去完成FIR濾波器的設計呢?有哪些步驟?

2021-11-18 06:39:46

嗨? 如何在HLS 14.3中編寫pow功能? HLS 14.3不支持exp和pow功能。我在我的代碼中寫了“#include math.h”。但是,它不起作用。 另外,我想知道C代碼中

2019-03-05 13:40:09

本文提出一種基于Stratix系列FPGA器件的新的實時高速脈動FIR濾波器的快速實現方法。

2021-05-06 09:50:42

本文首先介紹了FIR濾波器和脈動陣列的原理,然后設計了脈動陣列結構的FIR濾波器,畫出電路的結構框圖,并進行了時序分析,最后在FPGA上進行驗證。結果表明,脈動陣列的模塊化和高度流水線的結構使FIR

2021-04-20 07:23:59

相位,簡單可擴展到多速率情況,以及充足的硬件支持除了其他原因之外。此示例展示了DSP System Toolbox?中用于設計具有各種特性的低通FIR濾波器的功能。內容獲得低通FIR濾波器系數最小階低通濾波器

2018-08-23 10:00:16

FIR濾波器的原理及結構是什么基于分布式算法的FIR濾波器的實現

2021-05-08 08:39:41

SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高層次綜合)工具支持將C、C++等語言轉化成硬件描述語言,同時支持基于OpenCL等框架

2021-11-11 09:38:32

頻率分量,為了節省資源,使用IIR濾波器即可。FIR濾波器FIR的最大特點就是其系統響應 h(n)是一個N點的有限長序列,FIR的輸出y(n)本質上就是輸入信號x(n)和h(n)的卷積(根據傅里葉變換

2020-09-25 17:44:38

目前FIR濾波器的硬件實現的方式有哪幾種?怎么在FPGA上實現FIR濾波器的設計?

2021-05-07 06:03:13

相對無限沖擊響應(IIR)濾波器,有限沖擊響應(FIR)能夠在滿足濾波器幅頻響應的同時獲得嚴格的線性相位特性,而數據通信、語音信號處理等領域往往要求信號在傳輸過程中不能有明顯的相位失真,所以FIR

2019-08-23 06:39:46

相對無限沖擊響應(IIR)濾波器,有限沖擊響應(FIR)能夠在滿足濾波器幅頻響應的同時獲得嚴格的線性相位特性,而數據通信、語音信號處理等領域往往要求信號在傳輸過程中不能有明顯的相位失真,所以FIR

2019-08-27 07:16:54

最近在學習全相位濾波器,請問有人做過全相位FIR濾波器嗎?能不能用matlab程序來比較一下全相位FIR濾波器與傳統方法設計的FIR濾波器有什么區別??希望有人能幫我解答。。。感激不盡。。。。

2011-05-10 15:34:03

用窗函數設計FIR濾波器實驗一、實驗目的1、熟悉FIR濾波器設計的基本方法。2、掌握用窗函數設計FIR數字濾波器的原理及方法,熟悉相應的計算機高級語言編程。3、熟悉線性相位FIR濾波器的幅頻特性

2009-05-12 01:47:22

轉dsp系列教程 FIR濾波器設計到的內容比較多,本章節主要經行了總結性的介紹,以幫助沒有數字信號處理基礎的讀者能夠有個整體的認識,有了這個整體的認識之后再去查閱相關資料可以到達事半功倍的效果

2016-09-29 08:23:26

轉dsp系列教程 本章節講解FIR濾波器的低通,高通,帶通和帶阻濾波器的實現。 37.1 FIR濾波器介紹 37.2 Matlab工具箱生成C頭文件 37.3 FIR低通濾波器設計 37.4 FIR

2016-09-29 08:32:34

最近總是遇到很多大俠在問濾波器相關的問題,之前對這一方面接觸不是很多,最近也是在學習一些這方面的知識,今天先和大俠簡單聊一聊FIR濾波器和IIR濾波器的區別,后續等研究的差不多了,再更新有關濾波器

2023-05-29 16:47:16

AD9361的FIR濾波器是否可以配置成RRC濾波器?只能用作低通濾波器嗎?另外,FIR濾波器的2/4倍插值是對原信號進行補0嗎?

2019-01-07 11:31:53

你好,我有一個與switch語句的合成有關的問題。我開始使用Vivado HLS并且我已經創建了一個小的file.cpp,僅用于學習,但是當Vivado HLS合成文件時,我沒有得到任何開關語句

2019-11-05 08:21:53

FIR濾波器是什么?DSPBuilder是什么?FIR數字濾波器的DSPBuilder設計

2021-04-30 07:14:19

描述 HLS系列霍爾效應液位傳感器(HLS)是用于連續液位監測的定制設計解決方案,適用溫度范圍寬廣,可校準定制編程輸出以適應各種幾何形狀的液位儲存箱。HLS系列是一款智能傳感器,帶有板載

2021-07-14 14:08:24

用窗函數設計FIR濾波器一、實驗目的1、熟悉FIR濾波器設計的基本方法。2、掌握用窗函數設計FIR數字濾波器的原理及方法,熟悉相應的計算機高級語言編程。3、熟悉線性

2009-05-10 10:02:15 97

97 什么是fir數字濾波器

Part 1: Basics1.1 什么是FIR濾波器?FIR 濾波器是在數字信號處理(DSP)中經常使用的兩種

2008-01-16 09:42:22 16243

16243 DA算法的FIR濾波器設計

1.引言 在數字信號處理系統中,FIR數字濾波器多采用專用DSP芯片(如TMS320CXX系列),這種基于DSP的處理系統存

2008-01-16 09:49:42 2065

2065

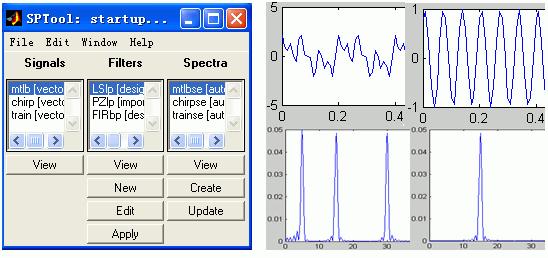

用MATLAB設計FIR濾波器的方法

摘? 要 介紹了利用MATLAB信號處理工具箱進行FIR濾波器設計的三種方法:程序設計法、FDATool設計法和SPTool設計法,給

2008-01-16 18:12:15 14763

14763

FIR 濾波器FAQ (基本知識問答)

1.1 什么是FIR濾波器?

FIR 濾波器是在數字信號處理(DSP)中經常使用的兩種基本的濾波器之一

2009-10-30 08:06:45 1301

1301

Synopsys天宣布推出其Synphony HLS (High Level Synthesis)解決方案

新思科技公司,今天宣布推出其Synphony HLS (High Level Synthesis)解決方案。該解決方案集成了M語言和基于模型的綜合

2009-11-04 16:55:53 962

962 fir濾波器的有關資料 fir_濾波器sourc.rar

2015-12-14 14:12:56 24

24 基于MATLAB的FIR濾波器設計與濾波。

2016-12-14 22:08:25 63

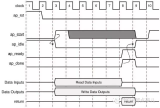

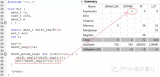

63 繼續HLS的基本概念。 1、DataFlow的概念,以及Dataflow和Pipeline的區別 如下所示的圖像處理過程,數據處理由2個濾波器構成: 默認情況下,HLS會遵循c邏輯中的先后順序,依次

2017-02-08 03:20:41 622

622

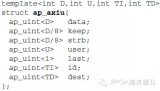

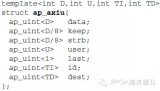

在上一章HLS的端口綜合里有提及,HLS綜合后的端口分為2中類型:BlockLevel和Port Level Interface。其中Port level是我們需要重點關注的,它又可以細分為4中類型

2017-02-08 03:27:11 475

475

在之前HLS的基本概念1里有提及,HLS會把c的參數映射成rtl的端口實現。本章開始總結下HLS端口綜合的一些知識。 1.HLS綜合后的rtl端口大體可以分成2類: Clock Reset端口

2017-02-08 03:29:11 544

544

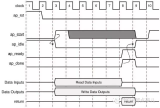

在上一章HLS提到了axi lite端口的綜合方式,以及directive的一些語法規則。這一章里面,介紹一下axi-stream和full axi端口的綜合實現問題。 1. AXI-Stream

2017-02-08 03:31:04 414

414

在上一章HLS提到了axi lite端口的綜合方式,以及directive的一些語法規則。這一章里面,介紹一下axi-stream和full axi端口的綜合實現問題。 AXI FULL端口的實現

2017-02-08 03:35:34 776

776

在之前的3章里,著重講解了HLS對AXI端口(包括axi-lite,axi-stream和full axi端口)的綜合實現問題,下面讓我們來介紹一下其它的端口類型是如何實現的。 在開始之前,先來

2017-02-08 03:39:11 354

354

在這個系列的上一篇文章“HighLevel Synthesis(HLS) 從一個最簡單的fir濾波器開始1”中,我們從一個最簡單的FIR濾波器,介紹了HLS是如何把C映射成RTL代碼的一些基本細節

2017-02-08 05:10:34 349

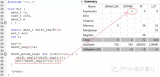

349 在上一章“High LevelSynthesis(HLS) 從一個最簡單的fir濾波器開始2”中,我們通過修改c的頭文件里面的類型精度定義,把DSP48E的消耗數量從8個壓縮到了2個: 但這個結果

2017-02-08 05:11:11 341

341

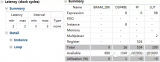

在這個系列的前3篇文章“HighLevel Synthesis(HLS) 從一個最簡單的fir濾波器開始1-3”中,我們從一個最簡單的FIR濾波器,一步步優化,得到了一個比較理想的HLS綜合結果

2017-02-08 05:13:37 983

983

在這個系列的前4篇文章“HighLevel Synthesis(HLS) 從一個最簡單的fir濾波器開始1-4”中,我們從一個最簡單的FIR濾波器,一步步優化,得到了一個資源和Latency都比

2017-02-08 05:18:11 456

456

相信通過前面5篇fir濾波器的實現和優化過程,大家對HLS已經有了基本的認識。是時候提煉一些HLS的基本概念了。 HLS支持C,C++,和SystemC作為輸入,輸出為Verilog(2001

2017-02-08 05:23:11 674

674

1. HLS僅支持一個主時鐘和復位 因此,目前還沒有辦法完全用HLS做出一個多時鐘域的設計。 2. 對于同一個參數,HLS可以綜合出各種各樣的端口類型 這也需要額外的約束去進行設置 3. 雖然

2017-02-08 05:24:31 271

271

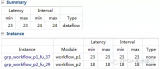

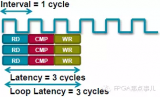

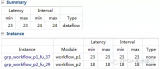

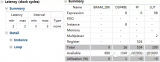

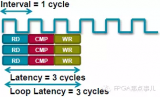

繼續HLS的基本概念。 Latency 和 Interval(II)的區別 當HLS綜合完后,在performance報告中,會看到這2個指標,它們都跟性能相關。那么這兩個參數的區別和含義具體

2017-02-08 05:28:12 708

708

窗口中,鍵入:vivado_hls -p fir_prj在vivado用戶界面打開工程,Vivado HLS打開,如下圖所示。方案1的綜合已經完

2017-02-09 05:07:11 411

411

數字濾波器廣泛應用于硬件電路設計,一般分為FIR濾波器和IIR濾波器。那么FIR濾波器和IIR濾波器有什么區別呢?本文通過幾個例子做一個簡單的總結。

2017-05-03 11:36:31 19

19 在特定圖像處理硬件設計中成功運用 High-Level Synthesis (HLS) 和 High-Level Verification (HLV) 數年之后, Qualcomm 認識到了 HLS

2017-09-11 11:37:38 9

9 摘要:HTTP Live Streaming(縮寫是HLS)是一個由蘋果公司提出的基于HTTP的流媒體網絡傳輸協議。今天主要以HLS協議為中心講述它的一些原理。

2017-12-10 09:25:37 54718

54718 實值數字有限脈沖響應(FIR)濾波器是許多數字信號處理(DSP)應用的基礎。這些濾波器在TMS320C55xxE DSP家族中的高效實現需要專門的算法結構,其可以利用雙片上硬件乘法器單元。該應用程序報告最適合于塊FIR和單樣本FIR濾波器的簡單化還提供了示例匯編代碼。

2018-05-04 14:31:45 5

5 你知道FIR濾波器與IIR濾波器的不同點嗎?它有有什么特點?濾波器是工程師工作中必不可少的器件,濾波器分為很多種,本文詳細介紹一下FIR濾波器與IIR濾波器之間的區別。

2020-08-09 14:15:00 31385

31385

【導讀】:前面的文章介紹了移動平均濾波器、IIR濾波器、梳狀濾波器,今天來談談FIR濾波器的設計實現。

2022-02-07 11:34:32 13

13 對于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統一將HLS集成到Vitis里了,集成之后增加了一些功能,同時將這部分開源出來了。Vitis HLS是Vitis AI重要組成部分,所以我們將重點介紹Vitis HLS。

2022-09-02 09:06:23 2857

2857 1.根據沖激響應的不同,將數字濾波器分為有限沖激響應(FIR)濾波器和無限沖激響應(IIR)濾波器。對于FIR濾波器,沖激響應在有限時間內衰減為零,其輸出僅取決于當前和過去的輸入信號值。對于IIR

2022-12-30 23:45:05 2276

2276 對于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統一將HLS集成到Vitis里了,集成之后增加了一些功能,同時將這部分開源出來了。Vitis HLS是Vitis AI重要組成部分,所以我們將重點介紹Vitis HLS。

2023-01-15 11:27:49 1317

1317 HLS ?(high-level synthesis)稱為高級綜合, 它的主要功能是用 C/C++為 FPGA開發 算法。這將提升FPGA 算法開發的生產力。 ?? Xilinx 最新的HLS

2023-01-15 12:10:04 2968

2968 FIR濾波器設計方法主要有窗函數法、線性最小均方差法、最大似然法、自適應濾波法、線性預測法等。窗函數法是一種簡單的設計方法,它可以通過選擇合適的窗函數來實現濾波器的設計;而線性最小均方差法則是一種更加復雜的設計方法,它可以通過最小化濾波器的均方差來實現濾波器的設計。

2023-02-15 14:58:37 1199

1199 FIR濾波器設計方法主要有窗函數法、線性最小均方差法、最大似然法、自適應濾波法、線性預測法等。窗函數法是一種簡單的設計方法,它可以通過選擇合適的窗函數來實現濾波器的設計;而線性最小均方差法則是一種更加復雜的設計方法,它可以通過最小化濾波器的均方差來實現濾波器的設計。

2023-02-15 15:29:19 2794

2794 數字濾波器是數字信號處理中最常用的一種技術,可以對數字信號進行濾波、降噪、增強等處理,其中最常見的兩種數字濾波器是IIR濾波器和FIR濾波器。本文將從IIR濾波器和FIR濾波器的原理、特點和應用等方面進行詳細介紹,以便更好地理解兩種濾波器的區別。

2023-06-03 10:21:43 12909

12909 電子發燒友網站提供《如何使用HLS加速FPGA上的FIR濾波器.zip》資料免費下載

2023-06-14 15:28:49 1

1 FIR(Finite Impulse Response,有限脈沖響應)濾波器是一種數字濾波器,其輸出信號僅由輸入信號和濾波器的沖激響應決定。FIR濾波器的名稱源于其沖激響應是一個有限長度的序列。

2023-06-20 11:26:04 787

787 該項目包含使用高級綜合 (HLS) 的 2D 中值濾波器算法的實現。該項目的目標是在不到 3 ms的時間內對測試圖像進行去噪,同時消耗不到 25% 的可用 PL 資源。特征如下:

2023-07-03 09:06:43 466

466

電子發燒友網站提供《將VIVADO HLS設計移植到CATAPULT HLS平臺.pdf》資料免費下載

2023-09-13 09:12:46 2

2

電子發燒友App

電子發燒友App

評論