資源利用率、邏輯層次和時序約束。 2時序基線設定:在每個實現步驟后檢查并解決時序違例,從而幫助布線后收斂時序。 3時序違例解決:識別建立時間違例或保持時間違例的根源,并解決時序違例。 01 初始設計檢查詳細介紹 在賽靈思器件上實現設計,是一個自動化程度相當

2021-11-05 15:10:26 4603

4603

大家好,我正在使用Virtex 5,并試圖實現我的設計的時序收斂。速度等級為-2,為150Mhz。從.srp報告中,我的設計的最大頻率非常接近。但是,我想我必須在那里保留一些余量以防止P&amp

2019-04-11 12:13:44

的負載和金屬線網的延遲l增加Tskewn在時鐘路徑上,插入buffer,增加時鐘路徑的延遲,但是不能影響hold timing。 Holdtime violation:保持時間在靜態時序分析時必須滿足

2018-11-26 14:39:04

:FTM0_Ch0_Ch1_IrqHandler 第 287 行: 如果 (chan0IntFlag && g_ftmChannelRunning[0][0]) { TIMING_Ftm_IrqHandler(0U, 0U

2023-03-29 08:20:52

見 AD5700 DatsSheet Page9,Carrier Detect Off Timing:請問圖中紅圈標記的RXD波形是如何來的呢?在示波器上也觀察到了此現象,這個波形對于UART

2018-12-14 09:22:48

知道“時間分析器”和“planahead”可以幫助我,但我無法理解它的報告。我該怎么做才能解決時間問題。我找不到一些材料來幫助我理解“時序分析”,“代碼風格”,“如何糾正時間問題” ','時序收斂'等等

2019-03-18 13:37:27

ISE Timing Anlayzer report 是看post-map 還是 post-place&route我現在有個工程 post-map 有錯post-place&route 通過這該以哪個為準

2017-08-24 14:15:26

本帖最后由 beHancock 于 2020-3-8 16:14 編輯

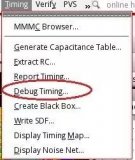

如題。補充幾個圖//-----------------------------------------這個目錄上Static Timing的圖標都和其它的不一樣了。。。

2020-03-07 22:43:51

最近用到sopc,設計片外ram,故整理“SOPC中SDRAM controller 的Timing配置”一文以備忘。Timing選項:CAS latency cycles(CAS等待時間):即為

2012-03-01 10:20:50

在使用庫函數(3.5版本),將通用定時器選用TIM_OCMode_Timing模式,同時使能4個通道中斷,可是進不了定時器的中斷函數。當選擇TIM_OCMode_Toggle模式時,就能進入到中斷

2019-09-19 17:42:20

Setup/Hold Time ProblemConclusionIf the Setup/Hold time error happen on the Input Register (Example

2008-09-11 09:23:30

fpga_timing技術文檔 xilinx官方

2016-08-17 09:02:16

niScope Configure Horizontal Timing 的說明中,參數number of records,根據我的測試,應該是設置獲取信號的通道數。但min record

2018-01-09 15:44:28

: Timing requirements not met這個錯誤,之前那些正常的工程全都報這個錯誤,別人電腦里的工程我軟件打開還是報錯,我的給別人編譯又能通過,然后我quartus已經卸載重裝好多次了,版本也從10.0 到11.0,然而還是沒有什么卵有,請問有大神知道這個應該怎么搞么?難道重裝系統?!

2016-01-15 10:51:47

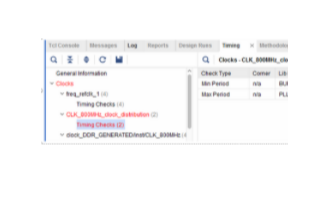

窗口里面可以查看相關的時序違例信息,這里只顯示了10個,可以在report timing summary中選擇要查看的個數,比如選擇100個五:我們可以打開setting ->synthesis

2018-08-22 11:45:54

to!! ---------------+---------+---------+---------+---------+ Timing summary: --------------- Timing errors: 0Score: 0(Setup/Max: 0, Hold: 0) Constraints

2019-02-26 10:15:03

Until now, verifying that timing in 33 MHz 64-bit PCI designs met the setup and hold specification

2019-04-28 06:35:34

如果出現了時序違例,我們會關注兩點: 為什么會出現時序違例? 如何解決? 首先我們要搞清楚時序是在哪個階段違例: 在綜合階段或者post opt階段出現了時序違例,那么很有可能的原因如下

2021-01-08 17:10:25

如圖所示,在TC397的ASCLIN SPI Master Timing表格中,控制器所需要的最小setup time大于最小clock period,這是不滿足時序要求的,請問datasheet是否有誤?

2024-01-29 08:00:24

嗨,如何消除負面松弛?如果我把時間忽略約束放到松弛路徑上,它會破壞邏輯嗎?謝謝你以上來自于谷歌翻譯以下為原文Hi, How to remove negative slack?. If i put

2019-03-29 12:48:58

the concepts of timing analysis such as setup hold time, skew , transport delay, other timing violation etc.

2019-02-14 08:16:03

). I mean, how to measure the setup or hold time of input signal in FPGA andcompare with the values given from static timing report. FPGA freak

2019-01-15 11:07:15

FPGA開發板,工程編譯后,Timequest timing analyzer 顯示紅色,是否是錯誤,需要改正?編譯結果中,messages框中,并沒有錯誤,只是有一些警告,這樣看來,是不是那個timequest并不需要改正,也不會影響工程燒錄和運行?(見下圖)求指點

2019-04-22 15:37:41

您好,如果我想為我的設計獲得最佳時序收斂,我應該使用什么實施策略?例如,如果我想改善設置和保持的松弛度,我應該選擇哪種最佳策略?以上來自于谷歌翻譯以下為原文Hello,If i want

2018-11-05 11:40:14

喜我在Windows XP上安裝了xilinx ISE 10.1。我在地圖中遇到了一些時間問題,所以我在ISE的tcl窗口中將xil_timing_allow_impossible設置為1。地圖經歷

2019-03-05 07:48:54

玩轉Vivado之Timing Constraints特權同學,版權所有最近在熟悉Xilinx已經推出好幾年的Vivado,雖然特權同學之前已經著手玩過這個新開發工具,但只是簡單的玩玩,沒有深入

2016-01-11 16:55:48

剛開始學vhdl,想寫一個波形發生器的代碼,但過程中編譯老是出現Critical Warning (332148): Timing requirements not met的警告,想用

2016-12-10 15:43:14

在AD80370的datasheet里面有SYSREF± Setup and Hold Timing 這個時序圖,但是為什么圖中標示的holdup time是負值,如果這樣的話那device

2018-10-09 16:09:24

MIPI CS2 input timing和CX3 mipi interface configuration 的關系是什么?

CX3 mipi interface configuration中的值設置成什么是合理的?

2024-02-29 07:25:02

在quartus的仿真里面有兩種選項,functional simulation和timing simulation,請問他們的區別是什么?

2019-07-29 05:52:59

Timing Summary is from "Phase 6.1 Hold Fix Iter", but there is no hold violation

2018-11-01 16:13:49

Monitor Timing Standard

VESA and Industry Standards and Guidelinesfor Computer Display Monitor

2008-08-08 13:21:30 507

507 timing and jitter measurements have become crucial

in the design, verification, characterization, and application of electron

2009-07-21 10:21:09 0

0 Without Timing Constraints• This design had no timingconstraints or pin assignments– Note

2010-01-11 08:54:44 6

6 Timing Groups and OFFSET Constraints:

•Use the Constraints Editor to create groups of path

2010-01-11 08:55:47 4

4 Achieving Timing Closure:Timing Reports• Timing reports enable you to determine how and why

2010-01-11 08:56:19 0

0 Path-Specific Timing Constraints:Constraining Between Risingand Falling Clock Edges•

2010-01-11 08:56:50 10

10 IntroductionUntil now, verifying that timing in 33 MHz 64-bit PCI designs met thesetup and hold

2010-07-13 09:39:34 4

4 Implement Master-Slave Timing-Card Redundancy Using Maxim Timing ICs

Abstract

2009-04-07 23:43:36 666

666

Timing Con

2009-04-24 09:12:31 740

740

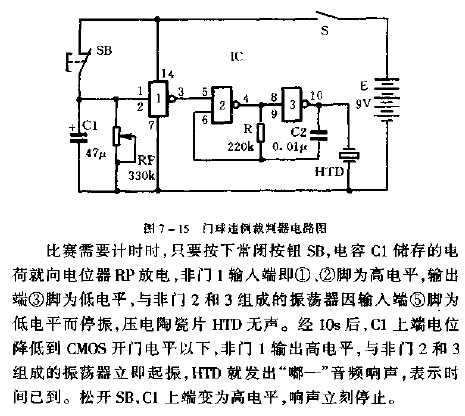

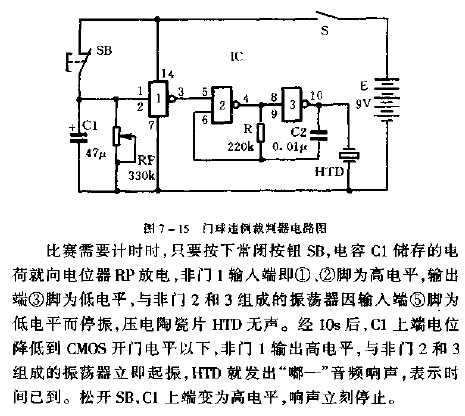

門球違例裁判器電路圖

2009-07-29 09:53:35 494

494

The DS31415 is a flexible, high-performance timing IC for diverse frequency conversion

2011-08-01 16:27:04 25

25 本內容介紹了邏輯分析儀中Timing-State存儲方式的應用

2011-09-22 14:26:50 14

14 TimeQuest_Timing_Analyzer快速入門教程

2015-12-14 14:21:13 22

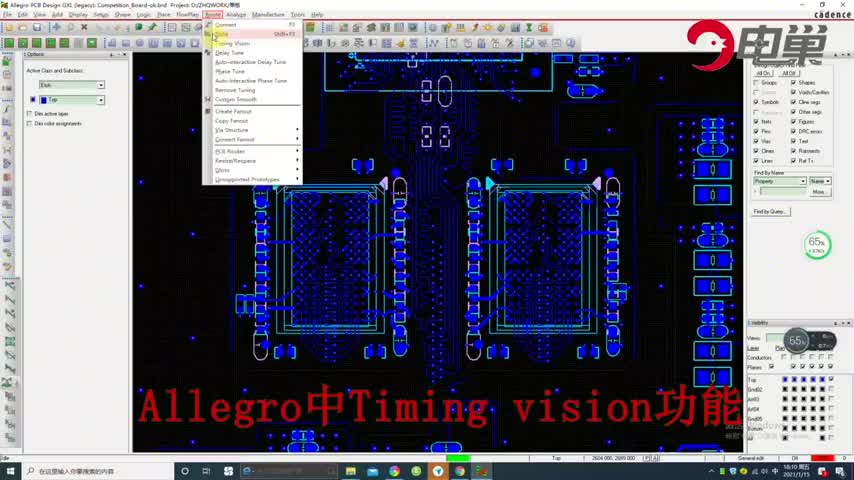

22 Timing,PCB學習好資料,歡迎下載學習。

2016-03-23 10:06:24 0

0 隨著FPGA規模越來越大,設計本身的復雜度也同樣增加。Xilinx UFDM中也經常提到了Design Complexity這樣一個概念。Timing/Complexity/congestion

2017-02-08 05:46:09 3042

3042

Perfect Timing II Book

2017-10-27 09:23:52 6

6 時序分析基本概念介紹——Timing Arc

2018-01-02 09:29:04 23487

23487

來維持嗎? 1、Vivado基本操作流程 2、時序基本概念 3、時序基本約束和流程 4、Baselining時序約束 5、CDC時序約束 6、I/O時序 7、例外時序約束 8、時序收斂優化技術

2018-08-06 15:08:02 400

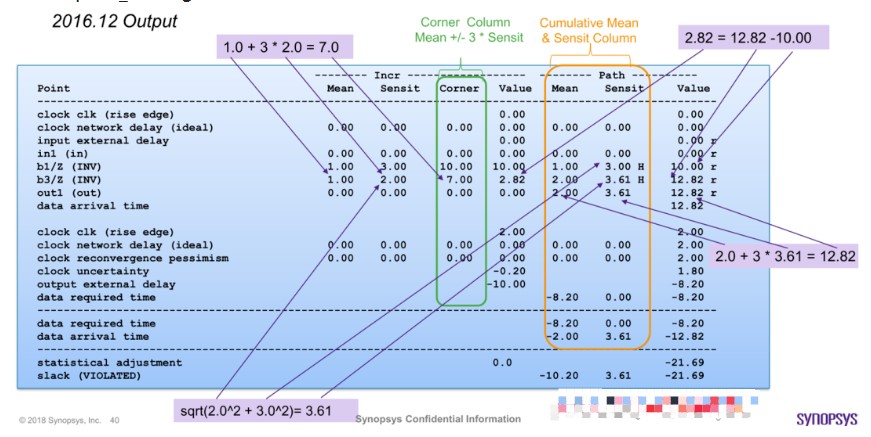

400 上述四個數值,無論是在timing report(通過report_timing_summary生成)還是design analysis report(通過report_design_analysis生成)中都有所體現。以timingreport為例,如下圖所示,可清晰地顯示上述四個數值。

2018-10-19 10:32:39 5175

5175 然后會出現如下窗口, 使用GTD前, 需要有一個machine readable格式的timing report文件, 該文件可以通過report_timing -machine_readable

2020-05-19 16:14:47 7022

7022

生成時序報告后,如何閱讀時序報告并從時序報告中發現導致時序違例的潛在問題是關鍵。 首先要看Design Timing Summary在這個Summary里,呈現了Setup、Hold和Pulse Width的總體信息,但凡WNS、WHS或WPWS有一個小于0,就說明時序未收斂。

2020-08-31 13:49:10 5370

5370

生成時序報告后,如何閱讀時序報告并從時序報告中發現導致時序違例的潛在問題是關鍵。 首先要看Design Timing Summary在這個Summary里,呈現了Setup、Hold和Pulse Width的總體信息,但凡WNS、WHS或WPWS有一個小于0,就說明時序未收斂。

2020-08-31 13:52:36 3098

3098

- 低脈沖寬度違例 - 高脈沖寬度違例 如需了解脈沖寬度違例的詳情,請參閱報告時序匯總(Report Timing Summary) 的TPWS部分。 最嚴重的脈沖寬度違例在報告中顯示為 WPWS。 如需了解

2020-11-19 13:48:45 4673

4673

AD9928:雙通道、14位CCD信號處理器,內置垂直驅動器和Precision Timing發生器

2021-03-19 01:16:56 7

7 AD9923A: CCD 信號處理器,內置垂直驅動器和Precision Timing發生器 數據手冊

2021-03-19 06:53:40 0

0 如果你參加過IC校招面試,自然會被問到“setup/hold的概念,以及setup/hold違例怎么辦?”

2021-04-27 14:15:54 3875

3875

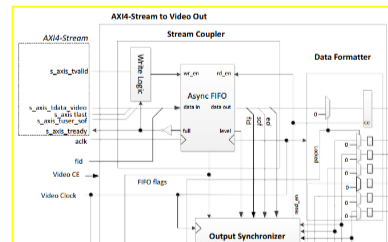

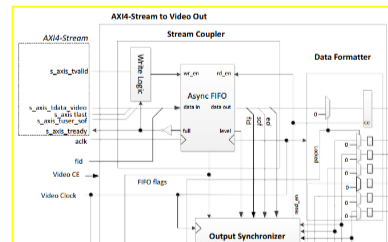

本文對Video out IP和Video Timing Controller IP進行簡要介紹,為后文完成使用帶有HDMI接口的顯示器構建圖像視頻顯示的測試工程做準備。

2021-05-08 10:03:16 5452

5452

VIVADO中時序報告中WNS,WHS,TNS,THS含義運行“report_timing”或“report_timing_summary”命令后,會注意到 WNS、TNS、WHS 和 THS

2021-10-21 14:32:35 18650

18650

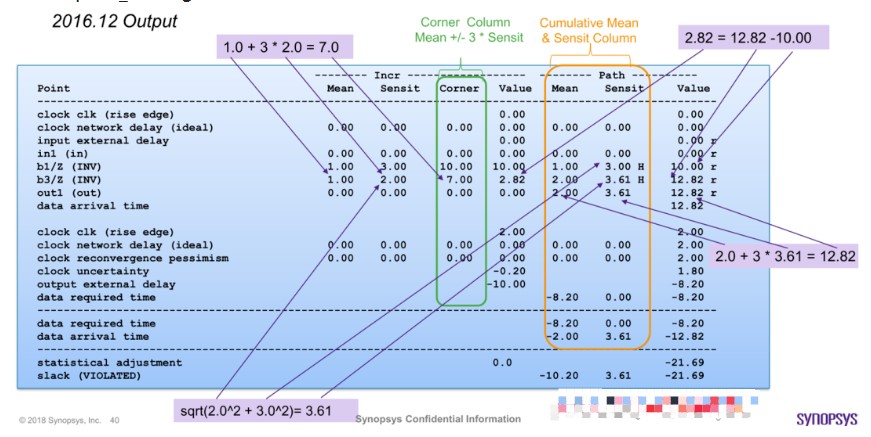

Corner: 高斯分布3個(具體幾個是可以設置的)Sigma邊界的最差值,比如Setup的話就是Mean+3*Sensit,如果是Hold的話就是Mean-3*Sensit。

2022-10-12 17:37:41 2295

2295

Path1容易出現hold問題,path2容易出現setup問題;如果在path1和path2的commen part修timing就會導致另外一個path的惡化;所以應該分別在path1的非commen part修hold,在path2的非commen part修setup。

2022-10-18 09:36:22 2679

2679 在Place Design之后再去看Hold Time,如果此時Hold Time的違例比較小(比如-0.05ns),還是不需要理會的

2023-01-11 09:05:41 2397

2397 就是SRAM MBIST_CLK延時下來剛好和SRAM測試地址TADDR的跳變完全對齊了,造成了SRAM的memory model的建立/保持時間違例,SRAM model在timing違例情況下Q端輸出為X態。下文具體內容請移步知識星球查看。

2023-02-08 16:09:02 1994

1994 包括shape 和re-shape 、 cell density map 、pin density map 、timing map 、timing chart 、highlight timing

2023-02-12 11:13:49 10107

10107 SDF后仿中往往生成的log中會有一些違例信息,Timing violation路徑或者$setuphold違例,這些信息混雜在后仿log中。

2023-03-07 14:55:20 567

567 Timing Commander 硬件 Interfaces 用戶指南

2023-03-15 19:24:19 1

1 9FGV1005 PhiClock PCIe Timing Commander 軟件 用戶指南

2023-03-21 19:28:49 2

2 9FGV1006 Timing Commander 用戶指南

2023-03-21 19:29:17 1

1 9FGV100x Timing Commander 用戶指南

2023-03-21 19:29:27 0

0 Timing Commander 軟件 for VersaClock 3S - 5P3502x

2023-03-23 19:42:47 1

1 VersaClock 6 Timing Commander 用戶指南

2023-03-29 19:02:31 1

1 默認report_timing中會出現換行的情況,如下圖所示,如何避免換行呢?

2023-04-15 10:20:33 2089

2089 今天這期小編將繼續與大家一起學習DFT的相關知識和流程代碼,在開始之前,先解決一下上期DFT學習的章節最后留下的問題—DFT工程師在收斂時序timing的時候經常遇到的hold的問題,即不同時鐘域的兩個SDFF(掃描單元的SI端hold違例問題。

2023-04-16 11:34:59 4291

4291 Timing Commander 軟件 for Programmable Buffers

2023-05-15 19:16:04 0

0 今天我們要介紹的時序分析概念是 **時序路徑** (Timing Path)。STA軟件是基于timing path來分析timing的。

2023-07-05 14:54:43 985

985

今天我們要介紹的時序基本概念是Timing arc,中文名時序弧。這是timing計算最基本的組成元素,在昨天的lib庫介紹中,大部分時序信息都以Timing arc呈現。

2023-07-06 15:00:02 1397

1397

Timing Commander 硬件 Interfaces 用戶指南

2023-07-06 18:35:05 0

0 9FGV1005 PhiClock PCIe Timing Commander 軟件 用戶指南

2023-07-07 19:27:28 0

0 9FGV1006 Timing Commander 用戶指南

2023-07-07 19:28:06 0

0 9FGV100x Timing Commander 用戶指南

2023-07-07 19:28:21 0

0 Timing Commander 軟件 for VersaClock 3S - 5P3502x

2023-07-10 19:34:18 0

0 VersaClock 6 Timing Commander 用戶指南

2023-07-11 19:27:17 1

1 Timing Commander 軟件 for Programmable Buffers

2023-07-11 20:27:38 0

0 積 (PPA)。 通過采用 Tempus Timing Solution,Realtek 將生產力提升了 2 倍,與之前使用的方法相比,設計收斂周轉時間縮短了 50%。此外,Realtek 的計算成本和內存占用

2023-11-06 10:10:01 206

206 今天想來聊一聊timing model。Top層在做STA的時候,為了速度的考量,有的時候不會把所有block都做flatten(展平化)處理

2023-12-06 14:03:13 270

270

電子發燒友App

電子發燒友App

評論