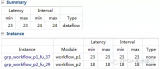

的Zynq 7000, 找了一個(gè)HLS的教程,就開(kāi)始了如下入門(mén)實(shí)驗(yàn),體驗(yàn)高級(jí)語(yǔ)言綜合設(shè)計(jì)IP。Vivado HLS是Xilinx 推出的高層次綜合工具,采用C/C++語(yǔ)言進(jìn)行FPGA設(shè)計(jì)。HLS提供了一些

2020-10-14 15:17:19 2881

2881

卡,一個(gè)4.0代PCle交換機(jī),由您選擇的外部主機(jī)CPU管理。HL-205符合oCP OAM(開(kāi)放式計(jì)算項(xiàng)目加速器模塊)規(guī)范。Eachcard包含Gaudi HL-2000處理器,該處理器集成

2023-08-04 06:06:14

利用所有可能的數(shù)據(jù)通信方式-沒(méi)有功能概述,也沒(méi)有對(duì)用戶代碼進(jìn)行優(yōu)化轉(zhuǎn)換-支持代碼報(bào)告得太晚了-在某些情況下,工具的高效實(shí)施是不可能的,例如當(dāng)必須將太多的加速器映射到硬件部分時(shí)。HLS工具無(wú)法預(yù)先檢測(cè)

2021-07-10 08:00:00

不同類(lèi)型的DMAHigh performance w/DMA幾種DMA的總結(jié)ZYNQ中不同應(yīng)用的DMA幾個(gè)常用的 AXI 接口 IP 的功能(上面已經(jīng)提到):AXI-DMA:實(shí)現(xiàn)從 PS 內(nèi)存

2022-03-31 11:39:10

壇友們,誰(shuí)用過(guò)Zynq7000的處理,交流一些問(wèn)題!

2017-08-14 20:53:12

`本才鳥(niǎo)想求圖像處理的范例,但求范例。`

2013-04-25 14:53:35

實(shí)驗(yàn)室進(jìn)了臺(tái)儀器,需要進(jìn)行二次開(kāi)發(fā) 主要是通過(guò)圖像采集卡進(jìn)行圖像采集,然后用matlab 進(jìn)行處理。目前在糾結(jié)于用labview還是C++ ,求大神給個(gè)指教,最好附一個(gè)理由

2012-05-14 11:27:40

圖像采集完,之后是保存后再調(diào)用處理還是直接將攝像頭連續(xù)采集的圖像進(jìn)行后續(xù)處理?包括ROI,灰度處理,二值法等。直接處理計(jì)算機(jī)好像處理不過(guò)來(lái)哈。處理后的圖像顯示花屏,求解。

2017-07-04 18:17:35

算法加速圖像處理目標(biāo)跟蹤 產(chǎn)品規(guī)格芯片型號(hào)ZYNQ 7010+ADAPIVE DSP(16)ARM核CORTEX-A7 DUAL 800MHZDRAM1GBYTE(4GB MAX)EMMC1G外圍

2017-06-08 10:33:07

輕松實(shí)現(xiàn)OpenCV C++視頻處理設(shè)計(jì)到RTL代碼的轉(zhuǎn)換,輸出硬件加速器或者直接在FPGA上實(shí)現(xiàn)實(shí)時(shí)視頻處理功能。同時(shí),Zynq All-programmable SOC是實(shí)現(xiàn)嵌入式計(jì)算機(jī)視覺(jué)

2021-07-08 08:30:00

Vivado HLS視頻庫(kù)加速Zynq-7000 All Programmable SoC OpenCV應(yīng)用加入賽靈思免費(fèi)在線研討會(huì),了解如何在Zynq?-7000 All Programmable

2013-12-30 16:09:34

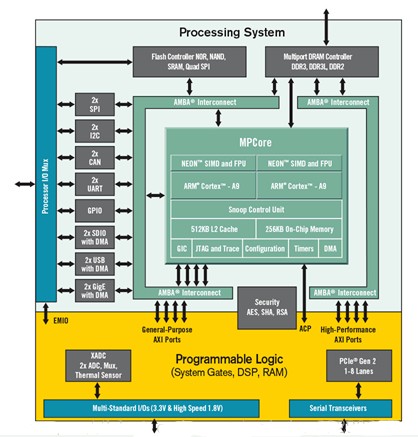

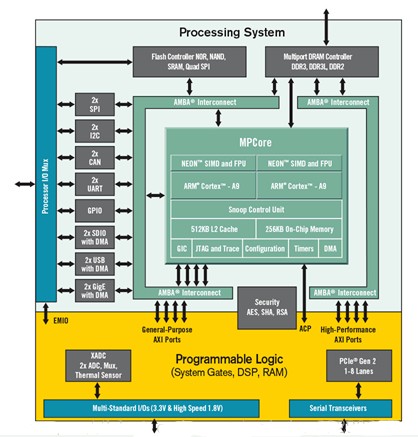

今天給大俠帶來(lái)簡(jiǎn)談Xilinx Zynq-7000嵌入式系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn),話不多說(shuō),上貨。Xilinx的ZYNQ系列FPGA是二種看上去對(duì)立面的思想的融合,ARM處理器的串行執(zhí)行+FPGA的并行執(zhí)行

2021-11-09 06:43:27

誰(shuí)會(huì)做基于labview的圖像采集,灰度處理,二值化處理,還有識(shí)別的界面。求指教

2014-04-17 16:46:23

vivado可以正常使用,但是HLS總是出現(xiàn)圖片中的錯(cuò)誤。請(qǐng)問(wèn)該如何解決?謝謝!

2020-08-12 01:36:19

利用所有可能的數(shù)據(jù)通信方式-沒(méi)有功能概述,也沒(méi)有對(duì)用戶代碼進(jìn)行優(yōu)化轉(zhuǎn)換-支持代碼報(bào)告得太晚了-在某些情況下,工具的高效實(shí)施是不可能的,例如當(dāng)必須將太多的加速器映射到硬件部分時(shí)。HLS工具無(wú)法預(yù)先檢測(cè)

2021-07-06 08:00:00

三、硬件加速之—使用PL加速FFT運(yùn)算(Vivado)

前四期測(cè)評(píng)計(jì)劃:

一、開(kāi)箱報(bào)告,KV260通過(guò)網(wǎng)線共享PC網(wǎng)絡(luò)

二、Zynq超強(qiáng)輔助-PYNQ配置,并使用XVC(Xilinx Virtual

2023-10-02 22:03:13

四、硬件加速之—使用PL加速矩陣乘法運(yùn)算(Vitis HLS)

前四期測(cè)評(píng)計(jì)劃:

一、開(kāi)箱報(bào)告,KV260通過(guò)網(wǎng)線共享PC網(wǎng)絡(luò)

二、Zynq超強(qiáng)輔助-PYNQ配置,并使用XVC(Xilinx

2023-10-13 20:11:51

項(xiàng)目名稱(chēng):基于ZYNQ的圖像算法加速試用計(jì)劃:本人在FPGA設(shè)計(jì)有三年多的工作經(jīng)驗(yàn),對(duì)zynq,做過(guò)petalinux移植、非petalinux的Ubuntu移植、基于lwip的數(shù)據(jù)處理系統(tǒng)、ps

2019-09-18 14:17:42

Detection模塊就設(shè)計(jì)的硬件加速模塊,旨在利用FPGA的并行處理能力加速圖像的處理效率。PL處理完的數(shù)據(jù),將以同樣的路徑返回到PS部分,處理結(jié)束的消息可以通過(guò)中斷方式進(jìn)行告知PS部分,以同步PS與PL的工作。本系統(tǒng)的組成架構(gòu)如下

2015-07-07 20:41:04

庫(kù)函數(shù),當(dāng)中的HLS OpenCV library可應(yīng)用于Zynq系列中ARM處理器的任務(wù)中。HLS OpenCV Library是可綜合的圖像處理庫(kù),本算法中的OpenCV功能函數(shù)被HLS OpenCV

2015-07-07 20:41:34

就是加速開(kāi)發(fā)的周期。加速策略可以從兩個(gè)方面考慮:(一)設(shè)計(jì)的重用和(二)抽象層次的提升。Xilinx Vivado開(kāi)發(fā)套件中的IP集成功能可以實(shí)現(xiàn)設(shè)計(jì)的重用,而Vivado HLS工具則能夠?qū)崿F(xiàn)對(duì)高層次

2020-10-10 16:48:25

的“HLS視頻庫(kù)”中的函數(shù),來(lái)進(jìn)行基于HLS的視頻圖像處理。對(duì)于上面列出的各個(gè)庫(kù),我們同樣會(huì)在后續(xù)章節(jié)中用到時(shí)候再進(jìn)行介紹。

2020-10-10 16:44:42

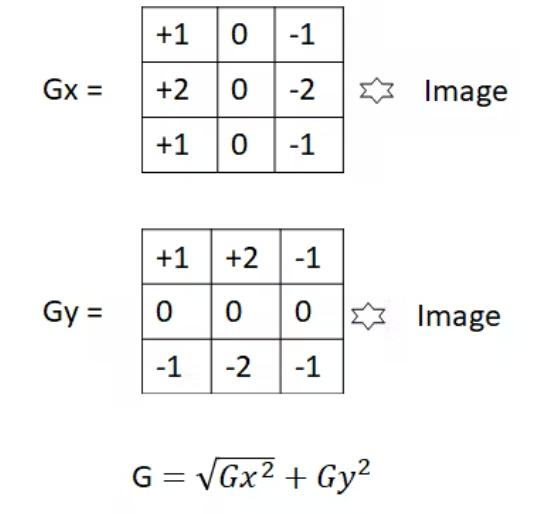

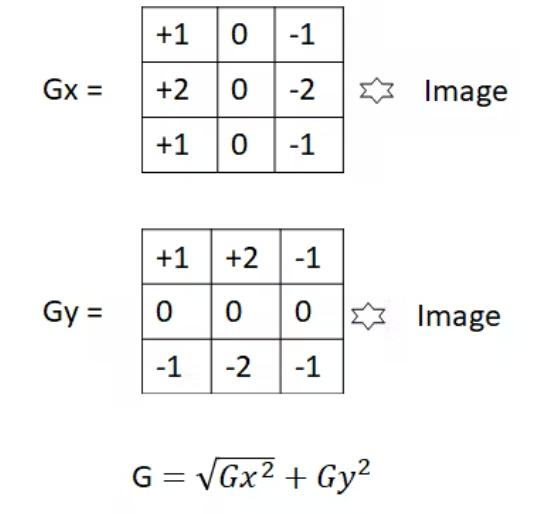

原子公眾號(hào),獲取最新資料第七章OV5640攝像頭Sobel邊緣檢測(cè)邊緣檢測(cè)是圖像處理和計(jì)算機(jī)視覺(jué)中的基本問(wèn)題,邊緣檢測(cè)的目的是標(biāo)識(shí)數(shù)字圖像中亮度變化明顯的點(diǎn)。在本章我們將通過(guò)OV5640攝像頭Sobel

2020-10-13 17:05:04

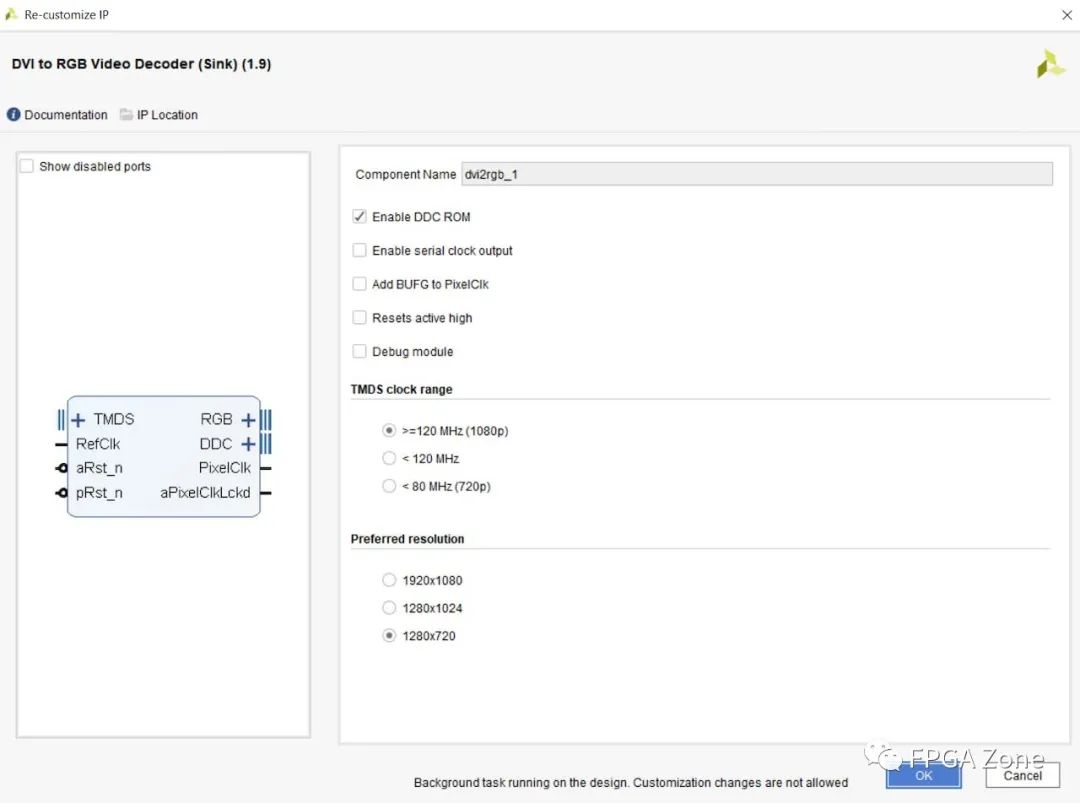

“Start of frame”是幀傳輸開(kāi)始信號(hào)。它在一幀圖像像素傳輸開(kāi)始的時(shí)候拉高一個(gè)時(shí)鐘周期。5.2實(shí)驗(yàn)任務(wù)本節(jié)的實(shí)驗(yàn)任務(wù)是使用Vivado HLS設(shè)計(jì)彩條顯示的IP核,并在Vivado中

2020-10-13 16:56:47

、醫(yī)學(xué)成像等方面應(yīng)用越來(lái)越廣。本章節(jié)我們將使用Vivado HLS生成一個(gè)圖像彩條疊加的IP核,來(lái)進(jìn)行基于OV5640的視頻圖像疊加實(shí)驗(yàn)。本章包括以下幾個(gè)部分:88.1簡(jiǎn)介8.2實(shí)驗(yàn)任務(wù)8.3HLS

2020-10-13 17:06:26

實(shí)現(xiàn)的圖像處理模塊已經(jīng)被綜合成FPGA中的硬件模塊,可以實(shí)時(shí)地處理FPGA中的視頻流。Vivado HLS所綜合出來(lái)的視頻處理模塊同樣可以部署在ZYNQ器件的PL端,其常用的架構(gòu)如下圖所示:圖

2020-10-13 16:58:56

是灰度圖做了自適應(yīng)二值化算法處理后的圖像,可以發(fā)現(xiàn)圖像經(jīng)過(guò)自適應(yīng)二值化計(jì)算出來(lái)的閾值比手動(dòng)指定閾值二值化的效果更好。11.2實(shí)驗(yàn)任務(wù)本節(jié)的實(shí)驗(yàn)任務(wù)是使用Vivado HLS設(shè)計(jì)OTSU自適應(yīng)二值化

2020-10-14 16:04:34

簡(jiǎn)介13.2實(shí)驗(yàn)任務(wù)13.3HLS設(shè)計(jì)13.4IP驗(yàn)證13.5下載驗(yàn)證13.1簡(jiǎn)介空間濾波是圖像處理領(lǐng)域應(yīng)用非常廣泛的工具之一,它可以改善圖像質(zhì)量,包括去除高頻噪聲與干擾、圖像平滑等。我們常見(jiàn)的空間濾波

2020-10-16 16:22:38

和抗干擾性,是直線檢測(cè)中效果最好的算法之一。霍夫變換也可用來(lái)檢測(cè)任意幾何形狀(比如圓),在圖像處理和模式識(shí)別領(lǐng)域得到了廣泛的應(yīng)用。本章我們將在HLS中實(shí)現(xiàn)基于霍夫變換的直線檢測(cè)。本章包括以下幾個(gè)部分

2020-10-14 16:06:47

。由于直方圖統(tǒng)計(jì)在軟件中計(jì)算簡(jiǎn)單,有助于商用硬件實(shí)現(xiàn),因此已經(jīng)成為一種流行的實(shí)時(shí)圖像處理工具。本章我們將在HLS中實(shí)現(xiàn)圖像的直方圖均衡算法。本章包括以下幾個(gè)部分:1010.1簡(jiǎn)介10.2實(shí)驗(yàn)任務(wù)

2020-10-14 16:02:01

漸滅,并且PS可以通過(guò)AXI接口來(lái)控制呼吸燈的開(kāi)關(guān)和呼吸的頻率。4.3HLS設(shè)計(jì)我們?cè)陔娔X中的“F:\ZYNQ\High_Level_Synthesis”目錄下新建一個(gè)名為breath_led的文件夾

2020-10-10 17:01:29

手把手教你設(shè)計(jì)人工智能芯片及系統(tǒng)(全階設(shè)計(jì)教程+AI芯片F(xiàn)PGA實(shí)現(xiàn)+開(kāi)發(fā)板)詳情鏈接:http://url.elecfans.com/u/c422a4bd15項(xiàng)目名稱(chēng):基于zynq的監(jiān)控視頻圖像

2019-10-30 17:03:31

大家好,我要做一個(gè)基于labview的圖像處理的一個(gè)畢業(yè)設(shè)計(jì),需要實(shí)現(xiàn)圖像求反、二值化、灰度處理等功能。輸入圖像的功能要怎么實(shí)現(xiàn)呢。我現(xiàn)在對(duì)于整體的設(shè)計(jì)沒(méi)有大概的思路。請(qǐng)求大神幫忙提供下思路。謝謝了。

2017-02-04 15:25:50

` ZYNQ系列是Xilinx推出的高端嵌入式SoC,其在片上集成了ARM處理器和FPGA。ZYNQ與傳統(tǒng)的嵌入式CPU相比,具有強(qiáng)大的并行處理能力。開(kāi)發(fā)人員利用FPGA強(qiáng)大的并行處理能力,不僅

2021-01-15 17:09:15

Vivado項(xiàng)目中使用以下IP塊。Xilinx I2S接收器 - 設(shè)置16位數(shù)據(jù)Xilinx I2S發(fā)送器 - 設(shè)置16位數(shù)據(jù)Zynq處理系統(tǒng)HLS IP核 - 一旦我們有初始音頻鏈傳遞數(shù)據(jù),這將

2019-07-31 05:30:00

,一路用于邊緣檢測(cè)處理(Sobel算法),另一路直接回顯。利用Video Mixer IP核將圖像疊加,通過(guò)HDMI輸出原始圖像或者算法處理后的圖像。本案例支持CameraLink Base/Full

2020-09-17 09:48:13

FPGA的HLS案例開(kāi)發(fā)|基于Kintex-7、Zynq-7045_7100開(kāi)發(fā)板前 言本文主要介紹HLS案例的使用說(shuō)明,適用開(kāi)發(fā)環(huán)境:Windows 7/10 64bit、Xilinx

2021-02-19 18:36:48

嗨,大家好,我是新手SDK用戶。我使用vivado hls來(lái)合成一個(gè)簡(jiǎn)單的圖像處理算法,并構(gòu)建了我現(xiàn)在使用sdk的硬件平臺(tái),我想使用sdk在獨(dú)立模式下使用opencv應(yīng)用程序在zynq fpga上

2020-05-04 17:09:19

利用labview處理圖像的后面板設(shè)計(jì),比如圖像的取反,二值化等

2015-03-31 09:45:36

你好我有Zynq 7z020板,我想訪問(wèn)它的GPIO,但我找不到Zynq處理器文檔,所以我知道如何訪問(wèn)Zynq GPIO?問(wèn)候

2019-09-11 10:48:04

Vivado HLS 2017.4 、Xilinx SDK 2017.4。

測(cè)試板卡是基于創(chuàng)龍科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗處理器設(shè)計(jì)的異構(gòu)多核SoC

2023-08-24 14:44:10

Vivado HLS 2017.4 、Xilinx SDK 2017.4。測(cè)試板卡是基于創(chuàng)龍科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗處理器設(shè)計(jì)的異構(gòu)多核SoC工業(yè)

2023-01-01 23:51:35

是基于創(chuàng)龍科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗處理器設(shè)計(jì)的異構(gòu)多核SoC工業(yè)級(jí)核心板。HLS 案例位于產(chǎn)品資料“4-軟件資料\Demo

2023-08-24 14:40:42

龍科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗處理器設(shè)計(jì)的異構(gòu)多核SoC工業(yè)級(jí)核心板。HLS 案例位于產(chǎn)品資料“4-軟件資料\Demo\FPGA-HLS

2023-01-01 23:52:54

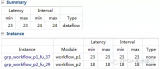

Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗處理器設(shè)計(jì)的異構(gòu)多核SoC工業(yè)級(jí)核心板。4 matrix_demo 案例案例功能: 實(shí)現(xiàn) 32*32 浮點(diǎn)矩陣乘法運(yùn)算功能

2023-01-01 23:50:04

龍科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗處理器設(shè)計(jì)的異構(gòu)多核SoC工業(yè)級(jí)核心板。

4 matrix_demo 案例案例功能: 實(shí)現(xiàn) 32*32 浮點(diǎn)矩陣乘法

2023-08-24 14:52:17

opencv_image_filter()處理結(jié)果圖 80 原始圖像5.3 IP 核測(cè)試請(qǐng)參考本文檔 HLS 開(kāi)發(fā)流程說(shuō)明章節(jié),完成 IP 核測(cè)試前的準(zhǔn)備工作。HLS 工程生成的 IP 核為

2023-01-01 23:46:20

_image_filter()處理結(jié)果圖 79 opencv_image_filter()處理結(jié)果圖 80 原始圖像

5.3 IP 核測(cè)試請(qǐng)參考本文檔 HLS 開(kāi)發(fā)流程說(shuō)明章節(jié),完成 IP 核測(cè)試前的準(zhǔn)備工作。HLS 工程生成

2023-08-24 14:54:01

對(duì)Xilinx可編程邏輯器件進(jìn)行開(kāi)發(fā),可加速算法開(kāi)發(fā)的進(jìn)程,縮短產(chǎn)品上市時(shí)間。本次案例用到的是創(chuàng)龍科技的TLZ7x-EasyEVM-S開(kāi)發(fā)板,它是一款基于Xilinx Zynq-7000系列XC7Z010

2021-11-11 09:38:32

。圖 75 hls_image_filter()處理結(jié)果圖 76 opencv_image_filter()處理結(jié)果圖 77 原始圖像IP核測(cè)試請(qǐng)參考本文檔HLS開(kāi)發(fā)流程說(shuō)明章節(jié),完成IP核測(cè)試前

2021-11-11 16:02:09

我在做數(shù)字圖像處理的時(shí)候,二值化是邊緣是斷開(kāi)的,我怎么幫邊緣鏈接成封閉的。。。。。

2014-08-26 14:08:30

是video in to AXI4-Stream,接到DMA,而HLS生成的算法IP是AXI4-Stream in and out。我想把AXI-Stream信號(hào)輸出接到HLS輸出的IP,IP經(jīng)過(guò)圖像處理后

2017-01-16 09:22:25

誰(shuí)有 LabVIEW Vision圖像處理開(kāi)發(fā)寶典。二手的賣(mài)給我。

2017-06-06 19:13:18

誰(shuí)可以給個(gè)圖像二值化處理的程序,通過(guò)閾值分割來(lái)實(shí)現(xiàn)二值化的???

2013-01-15 09:22:05

您好Xilinx的用戶和員工,我們正在考慮購(gòu)買(mǎi)Zynq 7000用于機(jī)器視覺(jué)任務(wù)。我們沒(méi)有編程FPGA的經(jīng)驗(yàn),并希望使用Vivado HLS來(lái)指導(dǎo)和加速我們的工作。關(guān)于這種方法的一些問(wèn)題:您對(duì)

2020-03-25 09:04:39

的請(qǐng)求,并驅(qū)動(dòng)液晶顯示器顯示視頻圖像。本實(shí)例除了前面提到對(duì)原始圖像做DDR3緩存和顯示,還會(huì)在原始圖像緩存到DDR3之前,另外做圖像的多行緩存和平滑處理運(yùn)算,獲得新的平滑后的圖像流,這個(gè)圖像流通

2019-12-12 16:47:28

、提取和跟蹤? 圖像分割與擬合? 攝像頭校準(zhǔn)、立體化和3D處理? 機(jī)器學(xué)習(xí):檢測(cè)、識(shí)別 圖3 OpenCV算法庫(kù)開(kāi)發(fā)的運(yùn)動(dòng)檢測(cè)應(yīng)用實(shí)例用HLS加速OPENCV函數(shù) 一旦完成了嵌入式視覺(jué)系統(tǒng)架構(gòu)的分區(qū)

2014-04-21 15:49:33

對(duì)Xilinx可編程邏輯器件進(jìn)行開(kāi)發(fā),可加速算法開(kāi)發(fā)的進(jìn)程,縮短產(chǎn)品上市時(shí)間。本次案例用到的是創(chuàng)龍科技的TLZ7x-EasyEVM-S開(kāi)發(fā)板,它是一款基于Xilinx Zynq-7000系列XC7Z010

2021-11-11 15:54:48

為性能加速的空間圖像處理開(kāi)發(fā)FPGA協(xié)處理器快速、精確的圖像數(shù)據(jù)的板上分類(lèi)是現(xiàn)代衛(wèi)星圖像處理的關(guān)鍵部分。對(duì)于地球科學(xué)和其它應(yīng)用而言,空間智能有效載荷利用智能機(jī)器

2010-04-27 08:30:31 15

15 高層次綜合設(shè)計(jì)最常見(jiàn)的的使用就是為CPU創(chuàng)建一個(gè)加速器,將在CPU中執(zhí)行的代碼移動(dòng)到FPGA可編程邏輯去提高性能。本文展示了如何在Zynq AP SoC設(shè)計(jì)中使用HLS IP。 在Zynq器件

2017-02-07 18:08:11 3207

3207

IP那節(jié)用過(guò))。這些模塊是連接到HP0的AXI4從端口,使得zynq7處理系統(tǒng)的數(shù)據(jù)通過(guò)AXI DMA IP核。硬件加速模塊是免費(fèi)的運(yùn)行,并不需要驅(qū)動(dòng),只要數(shù)據(jù)被CPU推送(通常簡(jiǎn)稱(chēng)為處理系統(tǒng)或PS)。

2017-02-07 18:13:35 3135

3135 繼續(xù)HLS的基本概念。 1、DataFlow的概念,以及Dataflow和Pipeline的區(qū)別 如下所示的圖像處理過(guò)程,數(shù)據(jù)處理由2個(gè)濾波器構(gòu)成: 默認(rèn)情況下,HLS會(huì)遵循c邏輯中的先后順序,依次

2017-02-08 03:20:41 622

622

在之前HLS的基本概念1里有提及,HLS會(huì)把c的參數(shù)映射成rtl的端口實(shí)現(xiàn)。本章開(kāi)始總結(jié)下HLS端口綜合的一些知識(shí)。 1.HLS綜合后的rtl端口大體可以分成2類(lèi): Clock Reset端口

2017-02-08 03:29:11 544

544

HLS工具 以個(gè)人的理解,xilinx將HLS(高層次綜合)定位于更方便的將復(fù)雜算法轉(zhuǎn)化為硬件語(yǔ)言,通過(guò)添加某些配置條件HLS工具可以把可并行化的C/C++的代碼轉(zhuǎn)化為vhdl或verilog,相比于純?nèi)斯な褂胿hdl實(shí)現(xiàn)圖像算法,該工具綜合出的代碼的硬件資源占用可能較多。

2019-10-12 17:34:00 1961

1961

源碼是官方的2014.4 TRD工程里的,整個(gè)工程是基于zc702板子的,但手里只有塊小zybo >_ 里面的硬件設(shè)計(jì)很有參考價(jià)值,最近想用FPGA加速surf算法,先在這分析下TRD工程

2017-02-08 10:12:11 458

458 大,我是否能夠利用Vivado HLS完成這項(xiàng)要求較高的運(yùn)算呢? 我開(kāi)始從軟件方面考慮這個(gè)轉(zhuǎn)換,我開(kāi)始關(guān)注軟件界面。畢竟,HLS創(chuàng)建專(zhuān)用于處理硬件接口的硬件。幸好Vivado HLS支持創(chuàng)建AXI slave的想法,同時(shí)工作量較少。 我發(fā)現(xiàn)Vivado HLS編碼限制相當(dāng)合理。它支持大多數(shù)C + +語(yǔ)言

2017-02-09 02:15:11 310

310 為期 ?1? 天的加速器開(kāi)發(fā)流程介紹主要講解如何測(cè)量系統(tǒng)性能、確定什么軟件功能應(yīng)該移至硬件,如何使用 ?Vivado? HLS? 工具裝配一款定制加速器,如何將該定制加速器添加至 ?Zynq SoC? 設(shè)計(jì),以及如何測(cè)量加速性能。 了解更多 ??

2017-02-09 06:23:11 286

286 Missing Link Electronics? 基于德國(guó)弗朗霍夫海因里希赫茲研究所 ?(HHI)? 的加速技術(shù)提供 2015.02a? 修訂版 ?Zynq SoC? 評(píng)估參考設(shè)計(jì)。支持

2017-02-09 08:17:06 212

212 在特定圖像處理硬件設(shè)計(jì)中成功運(yùn)用 High-Level Synthesis (HLS) 和 High-Level Verification (HLV) 數(shù)年之后, Qualcomm 認(rèn)識(shí)到了 HLS

2017-09-11 11:37:38 9

9 的FPGA架構(gòu)使得Xilinx Zynq-7000更加強(qiáng)悍,應(yīng)用領(lǐng)域更加廣泛。下面將從以下方面介紹Zynq-7000的應(yīng)用領(lǐng)域:汽車(chē)、通信系統(tǒng)、機(jī)器人、控制和儀器 、圖像和視頻處理 、醫(yī)藥、工業(yè)控制和許多其他領(lǐng)域。

2018-05-18 07:07:00 2584

2584 IP那節(jié)用過(guò))。這些模塊是連接到HP0的AXI4從端口,使得zynq7處理系統(tǒng)的數(shù)據(jù)通過(guò)AXI DMA IP核。硬件加速模塊是免費(fèi)的運(yùn)行,并不需要驅(qū)動(dòng),只要數(shù)據(jù)被CPU推送(通常簡(jiǎn)稱(chēng)為處理系統(tǒng)或PS

2018-10-02 07:25:11 394

394 OPENCV(Open Source Computer Vision)被廣泛的使用在計(jì)算機(jī)視覺(jué)開(kāi)發(fā)上。使用Vivado HLS視頻庫(kù)在zynq-7000全可編程soc上加速OPENCV 應(yīng)用的開(kāi)發(fā),將大大提升我們的計(jì)算機(jī)視覺(jué)開(kāi)發(fā)。

2018-11-10 10:47:49 1323

1323 了解協(xié)處理的價(jià)值,Zynq-7000加速器一致性端口,使用協(xié)處理器加速器的方法以及協(xié)處理器設(shè)計(jì)實(shí)例的概述。

2018-11-30 06:15:00 3960

3960 ADI公司在Embedded World 2015上展示了采用Zynq SDR套件的DDS HLS IP

2018-11-30 06:44:00 3026

3026 Adam Taylor討論了使用Zynq?和Zynq UltraScale +?SoC開(kāi)發(fā)圖像處理應(yīng)用程序時(shí)學(xué)到的一些技巧

2018-11-30 06:37:00 2023

2023 行業(yè)抓取式演示視頻重點(diǎn)介紹了Zynq UltraScale + MPSoC裝有專(zhuān)用處理引擎,面向圖像處理,實(shí)時(shí)處理和功能安全性。

2018-11-23 06:59:00 2723

2723 RTL代碼),也可以在某些場(chǎng)合加速設(shè)計(jì)與驗(yàn)證(例如在FPGA上實(shí)現(xiàn)OpenCV函數(shù)),但個(gè)人還是喜歡直接從RTL入手,這樣可以更好的把握硬件結(jié)構(gòu)。Xilinx官方文檔表示利用HLS進(jìn)行設(shè)計(jì)可以大大加速設(shè)計(jì)進(jìn)度:

2019-07-31 09:45:17 6232

6232

ZYNQ系列是Xilinx推出的高端嵌入式SoC,其在片上集成了ARM處理器和FPGA。ZYNQ與傳統(tǒng)的嵌入式CPU相比,具有強(qiáng)大的并行處理能力。開(kāi)發(fā)人員利用FPGA強(qiáng)大的并行處理能力,不僅

2019-10-27 10:43:12 3225

3225

ThunderImage 是深維科技(DeePoly)的旗艦級(jí)產(chǎn)品,基于賽靈思 Alveo 加速器卡進(jìn)行圖像處理加速。隨著目前高清圖片內(nèi)容越來(lái)越多,大家需要對(duì)圖片的尺寸/壓縮率做進(jìn)一步提升,這其中比較流行的一種格式是 Google從VP8 編碼提取出來(lái)的一套標(biāo)準(zhǔn) WebP。

2020-04-30 15:58:42 2917

2917 近日,元腦生態(tài)伙伴深維科技與浪潮聯(lián)合發(fā)布業(yè)內(nèi)首個(gè)基于FPGA的HEIF圖像處理加速方案。

2020-10-23 11:16:53 2201

2201

的是VivadoIP,用于支持Vivado IP 設(shè)計(jì)流程。后者用于Vitis應(yīng)用加速流程,此時(shí),Vitis HLS會(huì)自動(dòng)推斷接口,無(wú)需在代碼里通過(guò)Pragma或Directive的方式定義Interface,最終會(huì)輸出.xo文件。 User Control Settings還有其他的一些變化,如下表

2020-11-05 17:43:16 37066

37066 基于嵌入式Linux系統(tǒng)的Qt-Embedded圖像處理界面開(kāi)發(fā)總結(jié)(嵌入式開(kāi)發(fā)培訓(xùn)網(wǎng))-文檔為基于嵌入式Linux系統(tǒng)的Qt-Embedded圖像處理界面開(kāi)發(fā)總結(jié)文檔,是一份不錯(cuò)的參考資料,感興趣的可以下載看看,,,,,,,,,,,,,

2021-08-04 15:23:20 7

7 Vitis Vision庫(kù)是OpenCV和Vision功能的加速庫(kù),可在Vitis環(huán)境中使用,這些庫(kù)的L1目錄是示例設(shè)計(jì)。為了適應(yīng)各種用戶環(huán)境,從2020.1版本開(kāi)始,Xilinx不再

2022-02-16 16:21:38 2016

2016

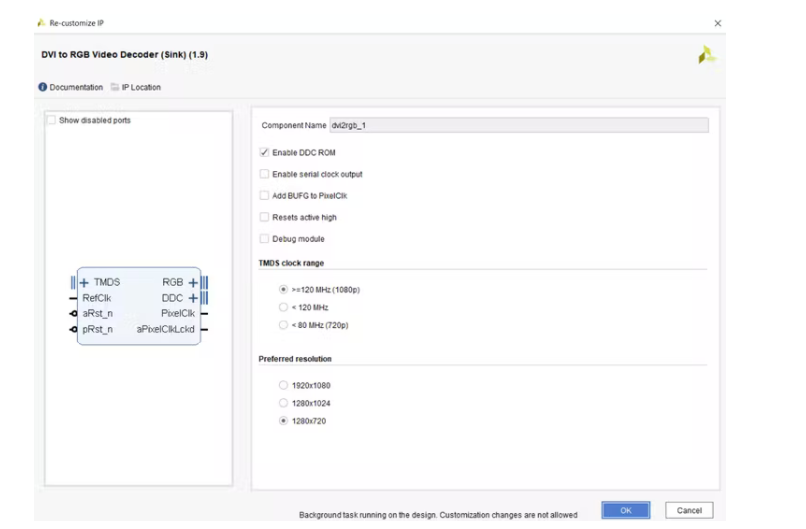

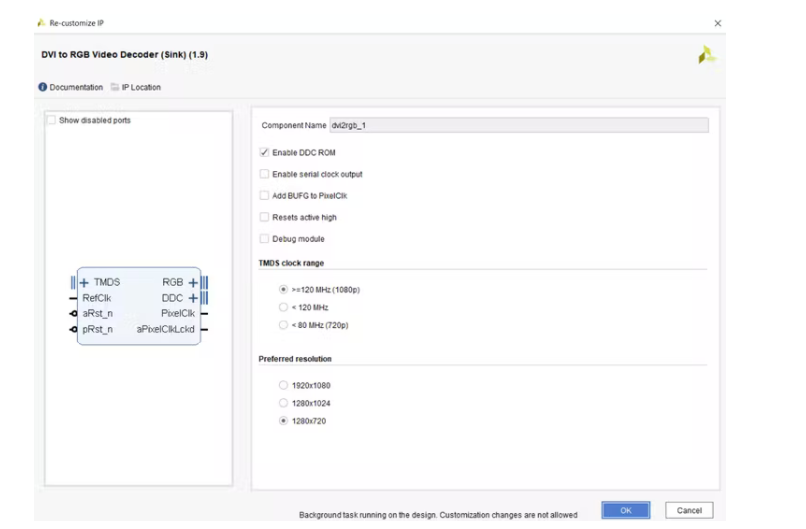

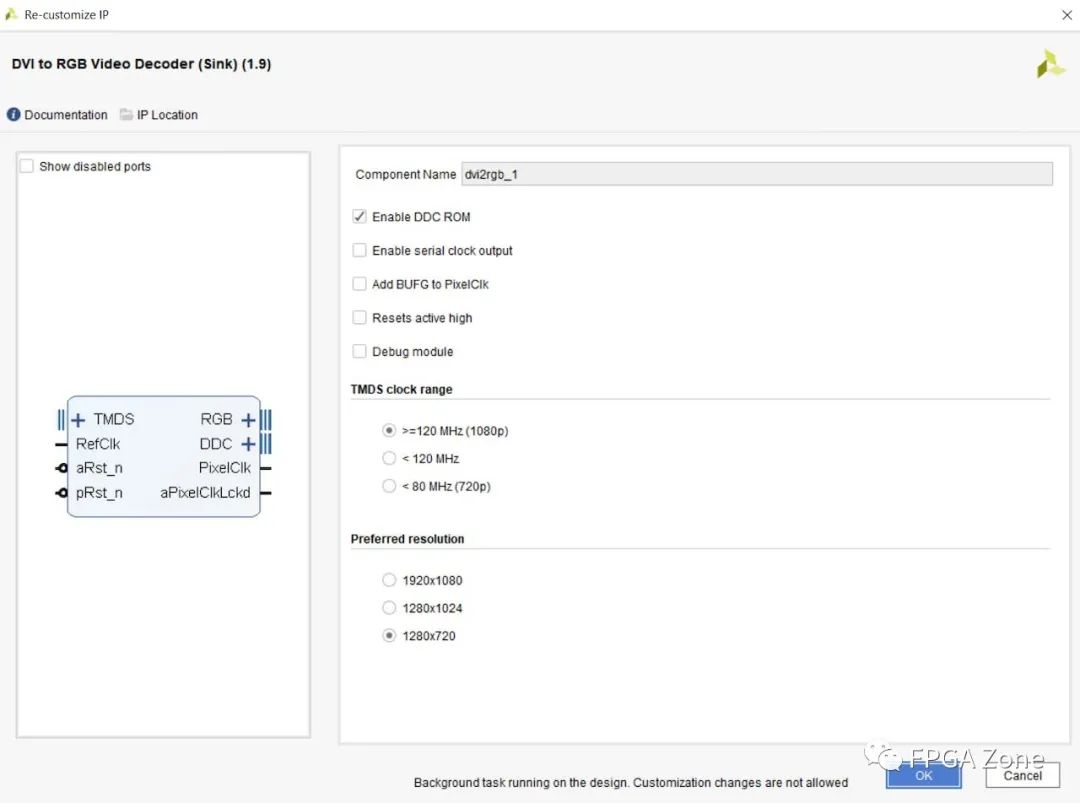

本文將介紹如何創(chuàng)建一個(gè)支持HDMI輸入到輸出的圖像處理平臺(tái)。這可以用作基于HLS的圖像處理演示的基礎(chǔ)。

2022-03-31 10:22:46 2400

2400

本方案利用 HLS 功能創(chuàng)建圖像處理解決方案,在可編程邏輯中實(shí)現(xiàn)邊緣檢測(cè) (Sobel)。

2022-05-13 17:47:17 2597

2597

Vitis HLS 是一種高層次綜合工具,支持將 C、C++ 和 OpenCL 函數(shù)硬連線到器件邏輯互連結(jié)構(gòu)和 RAM/DSP 塊上。Vitis HLS 可在Vitis 應(yīng)用加速開(kāi)發(fā)流程中實(shí)現(xiàn)硬件

2022-05-25 09:43:36 1930

1930 對(duì)于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統(tǒng)一將HLS集成到Vitis里了,集成之后增加了一些功能,同時(shí)將這部分開(kāi)源出來(lái)了。Vitis HLS是Vitis AI重要組成部分,所以我們將重點(diǎn)介紹Vitis HLS。

2022-09-02 09:06:23 2857

2857 這里向大家介紹使用HLS封裝的縮放IP來(lái)實(shí)現(xiàn)視頻圖像縮放功能。將HLS封裝的縮放IP加入到OV5640圖像傳輸系統(tǒng),驗(yàn)證圖像放大和縮小功能。

2022-10-11 14:21:50 1517

1517 電子發(fā)燒友網(wǎng)站提供《ThunderGP:基于HLS的FPGA圖形處理框架.zip》資料免費(fèi)下載

2022-10-27 16:49:59 0

0 電子發(fā)燒友網(wǎng)站提供《帶有PYNQ和Vitis HLS的SHA256加密加速器.zip》資料免費(fèi)下載

2023-02-09 10:32:49 2

2 電子發(fā)燒友網(wǎng)站提供《如何使用HLS加速FPGA上的FIR濾波器.zip》資料免費(fèi)下載

2023-06-14 15:28:49 1

1 最近有人問(wèn)我圖像處理怎么研究,怎么入門(mén),怎么應(yīng)用,我竟一時(shí)語(yǔ)塞。仔細(xì)想想,自己也搞了兩年圖像方面的研究,做個(gè)兩個(gè)創(chuàng)新項(xiàng)目,發(fā)過(guò)兩篇論文,也算是有點(diǎn)心得,于是總結(jié)總結(jié)和大家分享,希望能對(duì)大家有所幫助

2023-06-16 10:00:29 617

617 本文介紹如何搭建一個(gè)通用的圖像處理平臺(tái),采用HDMI接口進(jìn)行輸入、輸出,可用于測(cè)試基于HLS的FPGA圖像處理項(xiàng)目。

2023-09-04 18:20:19 1050

1050

電子發(fā)燒友網(wǎng)站提供《CTAccel圖像處理(CIP)加速器.pdf》資料免費(fèi)下載

2023-09-15 14:21:36 0

0 Zynq器件將arm和FPGA結(jié)合,利用了兩者各自的優(yōu)勢(shì),arm可以實(shí)現(xiàn)靈活的控制,而FPGA部分可以實(shí)現(xiàn)算法加速,這大大擴(kuò)展了zynq的應(yīng)用。比如深度學(xué)習(xí)加速,圖像處理等等。PL側(cè)表示FPGA的邏輯部分,PS側(cè)為arm端以及一些AXI接口控制部分,二者實(shí)際上通過(guò)AXI接口實(shí)現(xiàn)通信和互聯(lián)。

2023-11-09 11:28:04 1460

1460

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論