電子發燒友網核心提示 :本文介紹了最新的Xilinx Zynq-7000 FPGA開發板 Zedboard 。Zedboard是基于Xilinx Zynq-7000擴展式處理平臺(EPP)的低成本開發板,也是行業首個面向開源社區的Zynq-7000擴展

2012-11-26 15:09:01 55135

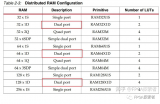

55135 真雙口RAM給設計帶來很多便利。在高速存儲中,需要對連續的數據同時處理,使用簡單雙口RAM只能讀取一個數據,而使用真雙口RAM可以同時讀取兩個數據,這樣明顯提高讀取速度以及處理速度。

2018-06-29 08:54:07 32478

32478

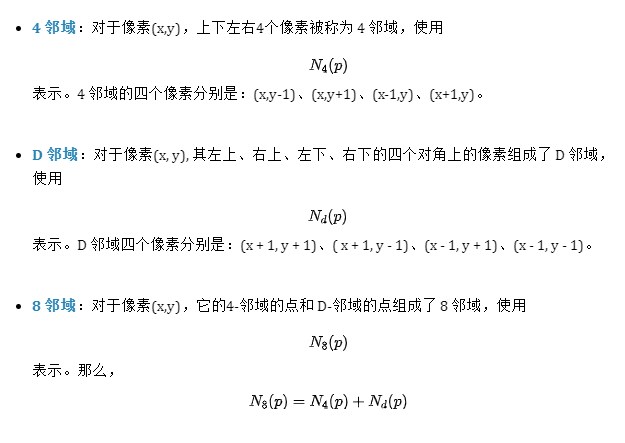

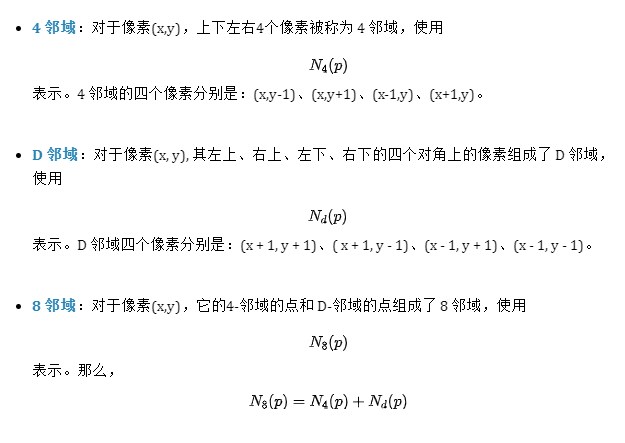

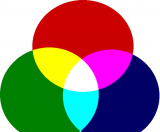

像素是圖像的基本元素,像素與像素之間存在著某些聯系,理解像素間的基本關系是數字圖像處理的基礎。常見的像素間的基本關系包括:鄰域、鄰接、通路、連通、距離。

2023-12-28 10:41:56 923

923

電子發燒友網編輯現為讀者整合《玩轉賽靈思Zedboard開發板》系列文章, 其中包括在ZedBoard開發板上的一些應用實例。本文主要講述Zedboard上的嵌入式linux應用,包括使用SDK設計最簡單的linux應用程序、linux交叉編譯環境搭建、設備驅動編寫等內容...

2013-01-24 13:38:18 16892

16892 大家好。我設計并模擬了簡單的RTL with Block RAMin Kintex 7。在合成和實現之后,vivado用于功率估計。當我使用分布式RAM時,會正確報告每個RAM的功耗。但是

2019-03-13 14:21:13

ZedBoard學習筆記(一)—永遠的led.pdf

2023-10-09 07:19:11

Helo人,我一直在使用Zedboard進行一些項目。我的USB_UART適配器與電路板斷開連接,無法再次連接。我聯系了Xilinx和Digilent,但根據它們無法修復。現在有一個解決方案是買一個

2020-04-02 07:00:45

如何下載Xilinx的uboot,網上有,不多說,下載最新的版本是u-boot-xlnx-xilinx-v2018.1.tar.gz在虛擬機里面進行編譯,過程中會出現些問題,本帖,不多說,會另發帖

2018-06-06 10:33:53

你好我已經在zedboard上成功開發了SD / MMC驅動程序,我的海量存儲應用程序運行正常。 zedboard是否支持SDIO?我正在為AR6K3無線驅動程序工作。在開發SDIO驅動程序時,當我

2019-03-14 07:59:03

修改為7.9.2009根據所需版本修改版本號:NACOS_VERSION執行構建鏡像命令: docker build -t nacos/nacos-serve:2.0.4 .構建完成,出現以下標識:原作者: Kongfu Panda 華為云社區

2022-06-16 14:29:34

;0x40004000----0x4000FFFF;64KB片內RAM;0x00000000—0x0000003f,ARM異常向量位置; 存儲器映射控制:MAP=00:由任何硬件復位激活,boot block中斷向量映射到存儲器

2014-03-24 11:49:13

大家好,我正試圖從microblaze_mcs轉移到一個完整的微系統,所以我從EDK生成了一個核心。我正在使用ISE版本14.5。我要經歷的步驟是:1.在ISE中打開現有設計。2.打開XPS,配置

2019-07-09 09:14:01

我今天正在實現FIFO,我想知道FIFOPrimitive和Block RAM實現之間的區別是什么。根據我的理解,它們使用相同的底層RAM原語,但FIFOPrimitive不能有不同的R / W方面

2019-02-27 14:16:45

圖像在采集和傳輸的過程中,通常會產生噪聲,使圖像質量降低,影響后續處理。因此須對圖像進行一些圖像濾波、圖像增強等預處理。為改善圖像質量,去除噪聲通常會對圖像進行濾波處理 ,這樣既能去除噪聲,又能保持

2020-12-26 15:57:01

圖像在采集和傳輸的過程中,通常會產生噪聲,使圖像質量降低,影響后續處理。因此須對圖像進行一些圖像濾波、圖像增強等預處理。為改善圖像質量,去除噪聲通常會對圖像進行濾波處理 ,這樣既能去除噪聲,又能保持圖像細節。

2021-02-04 07:03:26

如果N個攝像頭同時采集,HDVPSS的主通路(PRI)和輔助通路(AUX)是同時處理N路中某一路數據的,然后依次處理完N路?還是各自處理N路中不同路視頻,分別處理N/2路?求指教

2020-08-17 09:59:21

膨脹處理,其中B是一個卷積模板或卷積核,其形狀可以為正方形或圓形,通過模板B與圖像A進行卷積計算,掃描圖像中的每一個像素點,用模板元素與二值圖像元素做“與”運算,如果都為0,那么目標像素點為0,否則

2018-11-23 16:39:34

嗨,為了調試系統,我需要在系統運行時動態讀取Block-RAM內容....我只有JTAG線,我不能在FPGA中制作一個特定的塊用于讀取內容并通過JTAG等發送它們。我可以使用ISMP 13.2作為

2019-06-11 07:36:08

大家好,我正在嘗試根據生成的報告文件確定我實現的初始化9k Block Ram的tcl命令是否正常工作。我試圖在tcl中實現基于AR#39999的“-g INIT_9K:YES”命令。當我將開關設置

2018-10-26 15:06:01

我在Xilinx Spartan-3E(XC3S500E)上使用Verilog創建了一個使用多個雙端口Block RAM的設計,所有這些都通過Verilog原語實例化,例如

2019-04-24 07:35:02

我正在運行Spartan 6 block ram的模擬。時鐘速度為100Mhz。塊ram的寫作運作良好。我可以在內存中看到數據。但是當我讀取數據時,輸出有2個時鐘的延遲。在塊ram用戶guidt中

2019-07-25 08:15:27

你好,我使用Ubuntu 14.4 lts并且我安裝了vivado和petalinux(V2015.4),所以當我想使用SD卡在ZEDboard上啟動時,我嘗試做我的第一個項目,所以當我嘗試下面

2020-05-25 09:17:33

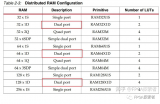

您好!分布式RAM和Block RAM之間究竟有什么區別?兩者都只是芯片內存,對吧?但我不知道兩者之間的區別。和..下一個問題.. isaboutMUX ..根據7系列概述,7系列FPGA支持全范圍

2020-07-19 06:37:51

DCM_SP為spartan 3E創建50Mhz DCM時鐘的IP,并且它可以工作。我不確定為什么當我嘗試創建Block RAM IP時它不起作用。我真的很感激一些幫助。歡迎來到Xilinx CORE

2019-06-05 13:39:14

本文介紹了如何在FPGA 中利用Block RAM 的特殊結構實現HDTV 視頻增強算法中灰度直方圖統計。灰度直方圖統計灰度直方圖統計是圖像處理過程中很常用的一個步驟,簡單來講,就是對一幅圖像各個

2012-05-14 12:37:37

你好我正在嘗試構建一個具有不同讀寫位寬的異步雙端口RAM模塊。我已經參考了Xilinx綜合指南(UG901)和Xilinx用戶指南(UG687)中提供的示例。這兩個指南都會使用寫入數據寬度小于讀取

2020-08-04 08:15:09

你好我正在開發一個項目,即使用Zedboard進行形狀識別。所以我需要將圖像作為一個位數組傳遞給電路板;為此,我想將圖像存儲在板載內存中。所以我有以下想法:1)在外部存儲圖像SD卡并使用VHDL讀取

2019-09-24 07:25:05

我們試圖從 OTG USB 啟動。我們搜索了相同但無法找到任何有用的資源。如果可能的話,你能指出我們如何實現這一目標嗎? 我們試圖為 OTG 構建 yocto 圖像。怎么做?是否可以直接從 OTG 啟動,或者我們需要從其他設備啟動并加載內核和文件系統?

2023-03-20 08:02:50

我們如何使用Virtex-4 FPGA的Block-RAM來存儲矩陣/ Vector的內容。例如,如何在BRAM中存儲矢量A = [1 2 4 5 6 7 9 3]?OR矩陣B = 1 2 3 45 6 7 8 9 1 4 5

2020-05-27 06:43:47

我們如何使用Virtex-4 FPGA的Block-RAM來存儲矩陣/ Vector的內容。例如,如何在BRAM中存儲矢量A = [1 2 4 5 6 7 9 3]?OR矩陣B = 1 2 3 45 6 7 8 9 1 4 5

2020-05-29 09:16:36

我們如何使用Virtex-4 FPGA的Block-RAM來存儲矩陣/ Vector的內容。例如,如何在BRAM中存儲矢量A = [1 2 4 5 6 7 9 3]?OR矩陣B = [1 2 3 45 6 7 8 9 1 4 5 232 1]

2020-05-29 14:41:56

嗨......我想在ZedBoard上安裝Linux,我遵循Zynq?-7000 SoC指南中Tutorial:Ubuntu附帶的所有說明,但是我遇到了構建uImage的問題。如果有人可以上傳uImage文件可以幫我很多。在此先感謝賈西姆

2019-10-31 09:59:20

套件的塊rams中,另一個塊ram用于存儲另一個與R G B陣列相同的可變溫度。Xilinx已經提到XC5LX110T具有5328Kb的內部RAM存儲器,因此我必須使用多大的圖像來確保使用內部DDR

2019-01-30 08:36:28

如何對照 Yocto 生成的圖像檢查設備上的圖像版本 ?

2023-11-13 07:41:49

大家好,我有FPGA virtext -5 ML510板,我想將圖像存儲在DD RAM中,我聲明一個數組,并希望存儲在DD RAM的基地址中,如果有人可以幫助我,那么使用Xilinx SDK 11從RAM寫入和讀取圖像數據的過程是什么。

2020-06-03 12:03:38

大家好。 我收到了一個項目文件,如何知道xilinx的哪個版本用于構建項目?謝謝納文

2020-03-20 06:33:53

嗨,我正在嘗試從源代碼中為xilinx zedboard交叉編譯u-boot。我可以按照本指南成功構建主分支:http://www.wiki.xilinx.com/Build+U-Boot我的問題是

2020-04-17 07:20:25

我正在嘗試使用virtex 5上的Block RAM來實現延遲線。延遲線需要將數據延遲一個時鐘周期。這可能使用Block RAM嗎?我嘗試使用簡單的雙端口RAM,“先讀”作為操作模式。我正在寫一個

2020-06-18 15:40:33

我有一個關于Zedboard輸出的快速問題。我試圖通過其中一個PMOD連接器在我的Zedboard上生成25MHz時鐘信號輸出。我用LVTTL將端口限制在3.3V。有一個警告,我正在抑制,所以我不期

2020-03-18 10:12:09

大家好,我需要將8位SRAM(例如,http://www.issi.com/WW/pdf/61LV5128AL.pdf)連接到我的Zedboard。我想我可以制作PCB,將SRAM焊接到其上并

2020-03-20 08:29:27

喜我使用synplify_pro作為綜合工具,vivado作為virtex7上的實現工具。我用block ram編寫了單獨的portsram,如下所示

2020-08-24 10:21:02

1、圖像的變換和壓縮,利用離散余弦變換(DCT)2、實現圖像的真彩色增強3、實現圖像的灰度變換,利用直方圖均衡化的方法4、使用常用的濾波器對數字圖像進行處理利用MATLAB GUI 做成界面,不足之處請高手修正。MATLAB版本為2011b。

2013-04-11 23:33:54

我有spartan-3an入門套件。我正在研究圖像處理項目,我想知道有什么方法可以將圖像從計算機讀取到工具包的RAM(我正在使用matlab simulink)請給我推薦一些對我有幫助的書

2019-08-29 10:43:16

你好,我正在開發一個在VC709開發板上使用Virtex7 FPGA的系統。該應用程序使用32Mb的板載Block RAM作為設計中的存儲元件。 FPGA配置序列完成后,有沒有一種方法可以使用PC上的JTAG / USB接口直接寫入和讀取Block RAM的內容?謝謝,

2019-09-29 14:00:01

生成公鑰基礎設施 (PKI) 樹后下一步是什么?是否修改 BSP 以生成簽名圖像?如果是,可以提供有關如何修改 BSP 以構建簽名圖像的文檔。謝謝。

2023-03-15 08:06:37

我有一個現有項目,可以使用幾個不同的構建配置正確構建。我想添加一個新的構建配置來克隆現有的配置,除了它使用我們使用的庫的更新版本。除了資源列表外,我一切正常。看起來項目中所有構建配置的資源列表都是

2023-04-14 08:19:39

嗨,我正在使用“RAMB16_S36”原始實現一個512內存寬度的Block Ram。我通讀了XAPP463用戶指南,但我顯然不了解初始化屬性。INIT_00是否對應于[255:0] Block

2019-07-22 08:10:27

交流通路電源的處理,理想的壓源作短路處理,理想的電流源作開路處理,非理想電源保留其內阻,這種處理辦法論基礎是什么?

再者,求解放大倍數,輸入電阻,輸出電阻等電路參數要在其交流通路上求解?

2024-01-21 20:53:00

你好,我正在為我的ZedBoard使用OV7670相機。我的項目是從相機捕獲并將其存儲在DDR內存中,并通過VGA輸出到顯示器。我的Block設計看起來像這樣:HTTP://lauri.v

2020-04-08 09:26:23

的。

FPGA中的Block Ram是重要和稀缺資源,能緩存的圖像數據行數是有限的,所以這個NxN的算子中的N不能特別大。當然FPGA也可以接DDR把圖像緩存到其中再讀出來進行處理,但這種處理模式就和CPU

2023-06-08 15:55:34

,維克多Rdp_fifo3.v 3 KB以上來自于谷歌翻譯以下為原文I am trying to use the block ram on Xilinx Spartan 3AN (XC3S400AN

2019-06-04 09:08:32

嗨,我想為我的設計使用比特流加密,我遇到了一個關于9K Block RAM的問題,在答案記錄39999中描述了r然后我決定在我的設計中刪除所有9k Block RAM并將它們更改為16k Block

2019-06-06 07:23:18

你好 我最近在使用Zedboard開發板上的音頻芯片,已經能夠把音頻通過ADAU1761放出來了,但是還沒有用到音頻芯片中的DSP。 現在已經使用ADAU1761評估板和sigmastudio

2018-08-14 07:41:04

嗨!我有一個關于分布式RAM和Block RAM的問題。芯片中有menexternalmemory或內存嗎?請詳細告訴我。謝謝!

2019-11-07 09:07:16

本文介紹了一種基于FPGA的網絡圖像處理系統設計和實現方法。系統主要包括圖像采集模塊、RAM控制模塊、JPEG編碼器3部分邏輯。在單片FPGA上實現圖像的采集、裁剪、緩存和JPEG編碼,構建

2012-02-08 14:41:59 1731

1731

電子發燒友網核心提示 :ZedBoard是基于Xilinx Zynq-7000擴展式處理平臺(EPP)的低成本開發板,也是行業首個面向開源社區的Zynq-7000擴展式處理平臺。此板可以運行基于Linux、Android、Windo

2012-11-23 16:40:08 13585

13585 基于ZedBoard和linux的應用程序HelloWorld的實現(完整工程)獲取Zedboard可運行的linux Digilent官網給出Zedboard的可運行linux

2013-01-24 14:15:46 152

152 ZEDBoard官方資料合集,包括用戶手冊、電路原理圖

2016-01-20 15:53:21 336

336 為vivado2014.1版本) 開發板:zedboard version d xc7z020clg484-1 串口軟件:SecureCRT 1. lab2.2 Adding IP cores in PL 監測開關

2017-02-09 05:59:30 576

576 整個工程進展到這一步也算是不容易吧,但技術含量也不怎么高,中間亂起八糟的錯誤太煩人了,不管怎么樣,現在面臨了最大的困難吧,圖像處理算法。

2017-02-10 12:48:37 778

778

首先基于前面的工作,通過調整已經很好的把指甲邊緣顯示出來了,不曾想我卻從那時開始走上了彎路,使用matlab去處理靜態圖片,以獲得更好的指甲和特征提取效果,結果就是,效果不理想(光照影響)并且用到攝像頭上來一點都不實用。

2017-02-10 16:16:09 895

895 本文主要介紹Zedboard HDMI核的構建和輸出顯示測試,具體的跟隨小編一起來了解一下。

2018-06-29 11:15:00 6042

6042

程度和輪廓熵值4個層次的圖像輪廓,同時結合Sobel算子和信息熵對交通路標圖像進行了提取與分塊處理。通過實驗仿真結果表明:在圖像的提取過程中,交通路標圖像隨著其DMOS值的增大,圖像的質量越差,清晰度越低,其NRSS值越小

2017-11-03 16:16:12 8

8 ZedBoard是Xilinx公司首款融合了ARM Cortex A9雙核和7系列FPGA的全可編程片上系統,兼具ARM和FPGA兩者的優勢,是小型化SCA實現的最佳嵌入式平臺之一。本文介紹

2017-11-17 07:19:14 5298

5298

根據VGA(Video Graphic Array)的原理,采用VHDL硬件描述語言,設計了一種基于Zedboard FPGA板卡的圖像顯示方案。實驗結果表明,在FPGA實現圖片顯示,達到了預期

2017-11-18 12:42:02 2114

2114 數字圖像處理技術正在向處理算法更優化、處理速度更快、處理后的圖像清晰度更高的方向發展,實現圖像的智能生成、處理、識別和理解是數字圖像處理的最終目標。

2018-01-12 17:47:03 54588

54588 本文介紹了如何在FPGA 中利用Block RAM 的特殊結構實現HDTV視頻增強算法中灰度直方圖統計。

2019-07-10 08:10:00 2578

2578 : Zedboard ARM處理器 : Cortex-A9 ARM操作系統: Linaro 12.11 ROS版本: indigo 移植前提 1. 開發板可以連接網絡 2. 使用SSH等對開發板進行遠程控制 編譯方法

2018-10-26 11:52:01 933

933 ZedBoard(Zynq評估和開發委員會)

ZedBoard是一款完整的開發套件,適用于對使用Xilinx:Zynq?-7000 All Programmable SoC探索設計感興趣的設計人員。

2018-11-30 06:05:00 2982

2982 了解新的Block RAM級聯功能,如何使用它,以及如何利用其功能和性能優勢。

2018-11-23 06:56:00 4470

4470 本文檔的主要內容詳細介紹的是Zedboard物料清單第2版免費下載

2019-02-12 17:20:36 0

0 在簡紹虛擬儀器的基礎上,本文基于Labwindows/CVI軟件開發平臺利用圖像處理技術設計并實現了一個圖像處理系統。重點討論如何增強圖像細節,去除圖像噪聲以及對圖像進行邊緣檢測。該系統在測控領域具有很廣的應用范圍。

2019-06-14 16:39:45 15

15 些大材小用,因此xilinx公司在其FPGA內部專門集成了很多存儲器模塊,稱作Block RAM,其猶如slice海洋當中的一顆顆明珠,專門實現數據暫存功能,且每個時鐘區域都布置了若干個Block

2020-11-23 14:08:43 7379

7379

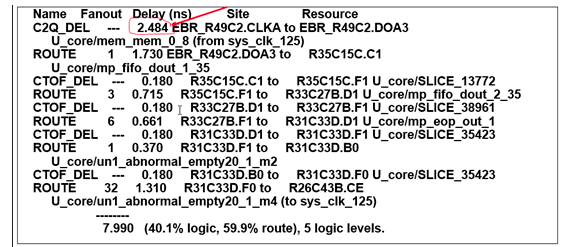

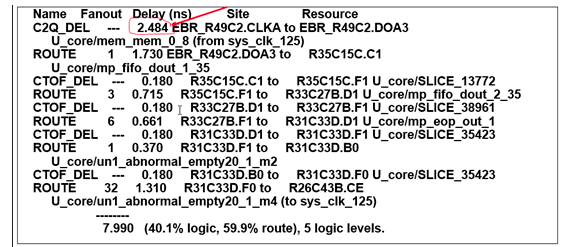

關于Block RAM的寄存器輸出,我們在《通過RTL改善時序的技巧之Block RAM的輸出》中介紹過。如果我們在時序報告中關鍵路徑上看到這樣一條信息: 在第一級的C2Q delay(clock

2021-03-26 15:50:27 1570

1570

本文檔的主要內容詳細介紹的是FPGA的RAM存儲資源詳細資料說明包括了:1、 FPGA存儲資源簡介,2、 不同廠家的 Block RAM 布局,3、 塊 RAM 和分布式 RAM 資源,4、 Xilinx Block RAM 架構及應用

2020-12-09 15:31:00 10

10 在FPGA中block ram是很常見的硬核資源,合理的利用這些硬件資源一定程度上可以優化整個設計,節約資源利用率,充分開發FPGA芯片中的潛在價值,本文結合安路科技FPGA做簡單總結,說明基本原理。

2020-12-24 14:28:09 916

916 FPGA可以調用分布式RAM和塊RAM兩種RAM,當我們編寫verilog代碼的時候如果合理的編寫就可以使我們想要的RAM被綜合成BRAM(Block RAM)或者DRAM(Distributed

2020-12-30 16:27:52 9

9 陣列,則需要大于等于訂個RAM或FIFO作為圖像數據緩沖,特別是對于高分辨率的掃描圖像進行處理而言,不僅浪費了很多FPGA寶貴的片上RAM資源,而且會使邊界效應的處理復雜化。不僅如此,由于在處理前需要存儲多行圖像數據,導致整個系統的

2021-01-26 16:22:00 30

30 私信聯系批評指正。 對于 BRAM(Block RAM,塊 RAM) 在 BRAM Controller 控制器下,支持單口 RAM、真雙口 RAM、單口 ROM 和雙口 ROM; 在不使用 AXI 的控制器情況下,

2021-05-03 09:47:00 7234

7234

VivadoHLS嵌入式實時圖像處理系統的構建與實現優先出版(嵌入式開發電腦推薦)-VivadoHLS嵌入式實時圖像處理系統的構建與實現優先出版 ? ? ? ? ?

2021-07-30 12:39:03 0

0 CV-CUDA (Computer Vision – Compute Unified Device Architecture)高性能圖像處理加速庫,近日發布 Alpha 版本,正式向全球開發者開源

2022-12-21 20:45:02 732

732 本文主要講述了Speedster7t FPGA的片上SRAM,也就是Block RAM針對傳統的結構所做出的一些優化。

2023-07-13 17:24:15 302

302

圖像處理是利用復雜的算法對圖像進行技術分析。在圖像處理中,圖像是輸入,有用的信息是輸出。據報道,到2021年,圖像處理行業產值將達到389億美元。

2023-07-24 15:00:31 417

417 交流通路電流源怎么處理 交流通路電流源是一種可以用來保證完整的電路通路中存在恒定交流電流的電源。它主要由信號發生器和振蕩器組成,可以應用在各種領域中,如通信、測量和控制等。在應用中,如果不得當,會出

2023-09-13 11:23:12 1094

1094 對原始獲取圖像進行一系列的運算處理,稱為圖像處理。圖像處理是機器視覺技術的方法基礎,包括圖像增強、邊緣提取、圖像分割、形態學處理、圖像投影、配準定位和圖像特征提取等方法。

2023-10-23 10:43:08 193

193

電子發燒友App

電子發燒友App

評論