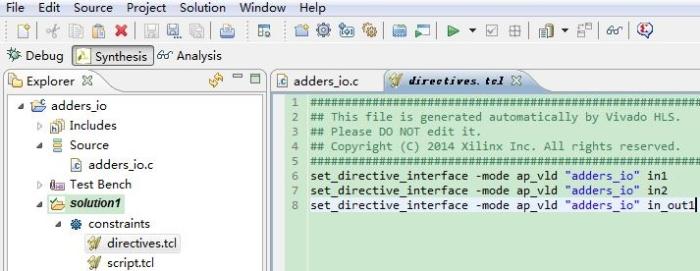

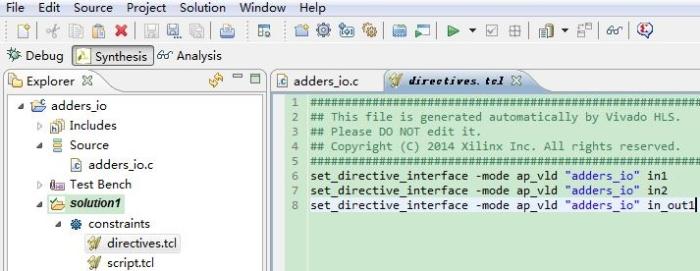

作者:Mculover666 1.實驗目的 通過例程探索Vivado HLS設計流 用圖形用戶界面和TCL腳本兩種方式創建Vivado HLS項目 用各種HLS指令綜合接口 優化Vivado HLS

2020-12-21 16:27:21 3153

3153 當我們安裝好Vivado 的時候,也同時裝好了Vivado HLS.。 這是個什么東西?我就有一種想一探究的感覺。網上一查,Vivado High-Level Synthesis。學習了一段時間

2020-10-14 15:17:19 2881

2881

每次我們更改硬件時,我們都需要告訴 HLS 將其導出為硬件描述語言并生成 Vivado 需要的所有各種源數據。

2022-09-22 09:15:34 1283

1283 , Mat 類型的關系和VivadoHLS中圖像hls::Mat類型介紹OpenCv中常見的與圖像操作有關的數據容器有Mat,cvMat和IplImage,這三種類型都可以代表和顯示圖像,但是,Mat類型

2021-07-08 08:30:00

Vivado HLS視頻庫加速Zynq-7000 All Programmable SoC OpenCV應用加入賽靈思免費在線研討會,了解如何在Zynq?-7000 All Programmable

2013-12-30 16:09:34

我在Vivado HLS中有以下錯誤的合成。我試圖更新許可證文件但沒有成功。請給我一個建議。@E [HLS-72]許可證簽出不成功。確保可以訪問許可證或通過環境變量指定適當的許可證。 執行

2020-05-20 09:13:21

1.實驗目的通過例程探索Vivado HLS設計流用圖形用戶界面和TCL腳本兩種方式創建Vivado HLS項目用各種HLS指令綜合接口優化Vivado HLS設計來滿足各種約束用不用的指令來探索

2021-11-11 07:09:49

本帖最后由 FindSpace博客 于 2017-4-19 16:57 編輯

在c simulation時,如果使用gcc編譯器報錯:/home/find/d/fpga/Vivado_HLS

2017-04-19 16:56:06

vivado可以正常使用,但是HLS總是出現圖片中的錯誤。請問該如何解決?謝謝!

2020-08-12 01:36:19

你好!如果我想使用vivado hls來合成具有axi流接口的代碼,是否有必須遵循的標準編碼風格?

2020-04-21 10:23:47

本人在學習vivado系列軟件開發套件的時候遇到以下問題.硬件平臺:米爾科技 Z-turn 7020 Board.問題描述:我在Vivado hls 里面寫了一個函數int add(int a

2016-01-28 18:40:28

本人在學習vivado系列軟件開發套件的時候遇到以下問題.硬件平臺:米爾科技 Z-turn 7020 Board.問題描述:我在Vivado hls 里面寫了一個函數int add(int a

2016-01-28 18:39:13

HLS高階綜合(highlevelsynthesis)在被廣泛使用之前,作為商業技術其實已經存在了20多年。設計團隊對于這項技術可以說呈現出兩極化的態度:要么堅信它是先進技術之翹楚,要么對其持謹慎

2021-07-06 08:00:00

,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統一將HLS集成到Vitis里了,集成之后增加了一些功能,同時將這部分開源出來了。Vitis HLS是Vitis AI

2022-09-07 15:21:54

了。1.5HLS庫Vivado HLS中包含了一系列的C庫(包括C和C++),方便對一些常用的硬件結構或功能使用C/C++進行建模,并且能夠綜合成RTL。在Vivado HLS中提供的C庫有下面幾種類型:1

2020-10-10 16:44:42

【資料分享】Vivado HLS學習資料

2013-11-02 11:21:14

Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統一將HLS集成到Vitis里了,集成之后增加了一些功能,同時將這部分開源出來了。Vitis

2022-09-09 16:45:27

模擬過程完成沒有0錯誤,但在合成期間顯示錯誤。我無法找到錯誤。我在合成期間在HLS工具中收到這樣的錯誤“在E中包含的文件:/thaus / fact_L / facoriall

2020-05-21 13:58:09

嗨,大家好,我有一個問題,在VIVADO HLS 2017.1中運行C \ RTL協同仿真。我已成功運行2014和2016版本的代碼。任何人都可以告訴我為什么報告NA僅用于間隔

2020-05-22 15:59:30

Vivado 2017.4、Xilinx VivadoHLS 2017.4、Xilinx SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高層次綜合)工具支持

2021-02-19 18:36:48

你好,我使用Vivado HLS生成了一個IP。從HLS測量的執行和測量的執行時間實際上顯著不同。由HLS計算的執行非常小(0.14 ms),但是當我使用AXI計時器在真實場景中測量它時,顯示3.20 ms。為什么會有這么多差異? HLS沒有告訴實際執行時間?等待回復。問候

2020-05-05 08:01:29

將Vivado HLS與Virtex 6(ML605評估套件)一起使用時,我遇到以下問題。我想導出一個RTL Designas Pcore,以便稍后將其導入XPS作為完整設計的一部分。根據相對

2018-12-28 10:33:38

我很好奇為什么在Vivado HLS 2017.2的Linux版本上有這么多的PE32可執行文件和庫?Vivado HLS 2017.2似乎安裝了545個PE32可執行文件和庫,總共消耗了743M

2018-12-26 11:37:29

嗨,我是HLS的新手,想要將opencv用于zynq-7000。我有兩個主要問題:1)一旦我可以從xx1167運行Video_Library_Windows.bat但現在我收到以下錯誤:我還更改

2020-03-26 07:59:19

案例的使用說明,適用開發環境: Windows 7/10 64bit、Xilinx Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4

2023-01-01 23:52:54

案例的使用說明,適用開發環境: Windows 7/10 64bit、Xilinx Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4

2023-08-24 14:40:42

7/10 64bit、Xilinx Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4。Xilinx Vivado HLS

2023-01-01 23:46:20

7/10 64bit、Xilinx Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4。Xilinx Vivado HLS

2023-08-24 14:54:01

前 言本文主要介紹HLS案例的使用說明,適用開發環境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx Vivado HLS 2017.4、Xilinx

2021-11-11 09:38:32

的經驗幾乎為0,因此我想就如何解決這個問題提出建議。這就是我的想法:1 - 首先,用Vivado HLS轉換VHDL中的C代碼(我現在有一些經驗)2 - 在Vivado HLS中生成IP核(如果我

2020-03-24 08:37:03

你好我正在嘗試在vivado HLS中創建一個IP,然后在vivado中使用它每次我運行Export RTL我收到了這個警告警告:[Common 17-204]您的XILINX環境變量未定義。您將

2020-04-03 08:48:23

尊敬的先生,由于突然斷電我的桌面電腦在vivado HLS正在進行我的代碼的C-Synthesis時關閉了,電源恢復后我啟動計算機并嘗試啟動HLS,然后小方形HLS符號來了(我把屏幕截圖放在了注冊

2020-04-09 06:00:49

同樣輸出AXI-Stream,再連到DMA.但是新手不知道那個HLS生成的IP怎么連?HLS的IP多了很多接口,這個IP有AXI control BUS,好像分辨率不一致,這個HLS的IP處理

2017-01-16 09:22:25

您好我有一個關于vivado hls的問題。RTL是否來自xivix FPGA的vivado hls onyl?我們可以在Design Compiler上使用它進行綜合嗎?謝謝

2020-04-13 09:12:32

您好Xilinx的用戶和員工,我們正在考慮購買Zynq 7000用于機器視覺任務。我們沒有編程FPGA的經驗,并希望使用Vivado HLS來指導和加速我們的工作。關于這種方法的一些問題:您對

2020-03-25 09:04:39

的設計代碼類似于傳統軟件編譯器生成的處理器匯編代碼。用戶可在匯編代碼級進行調試,但這一步并不是必需的。 雖然Vivado HLS能處理幾乎所有針對其它軟件編譯器的C/C++代碼,但代碼有一個限制。在用

2014-04-21 15:49:33

你好,我有一個與switch語句的合成有關的問題。我開始使用Vivado HLS并且我已經創建了一個小的file.cpp,僅用于學習,但是當Vivado HLS合成文件時,我沒有得到任何開關語句

2019-11-05 08:21:53

請問Vivado HLS出現這種情況是什么原因呢

2021-06-23 06:13:13

您好,我目前正在嘗試使用Vivado HLS在FPGA上合成加密算法。我根據需要拆分了C ++代碼并包含了一個測試平臺,但是當我嘗試模擬代碼時,我得到一個錯誤,說找不到測試平臺。我附上了錯誤圖片和項目檔案,希望有人能幫我找到解決方案。謝謝!LBlock_fpga.zip 48 KB

2020-05-15 09:26:33

Vivado HLS設計流程是怎樣的?

2021-06-17 10:33:59

這是我從Vivado HLS獲得的。如您所見,一旦完成合成,Vivado HLS就會提供延遲信息。當我使用VHDL代碼運行vivado時,如何獲得這種延遲?我運行了testbench和模擬,但我仍然沒有獲得延遲信息。請幫忙!謝謝!!

2020-05-01 15:20:12

嗨伙計,在我的PC Vivado設計套件2015.2和SDK 2015.2工作,但只有vivado HLS 2015.2沒有打開,這就是為什么我想重新安裝Vivado HLS 2015.2。如何下載

2018-12-27 10:57:49

Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高層次綜合 (HLS) 進行 FPGA 設計的簡介

2016-01-06 11:32:55 65

65 testbench來驗證設計。 Integrate帶有Xilinx IP Block的 HLS IP 這里展示了在IP Integrator中,如何將兩個HLS IP blocks跟Xilinx IP FFT結合在一起 ,并且在Vivado中驗證設計。

2017-02-07 17:59:29 4179

4179

Vivado hls既支持結構體,也支持枚舉類型,這兩種類型都可以作為接口出現在頂層函數。如果結構體出現在頂層函數,可以通過field_level 和struct_level進行封裝,如果枚舉類型作為接口出現在頂層函數,它實際上是整數,vivado會自動推斷相應mode的數據位寬。

2017-02-07 18:05:11 1817

1817

應用Vivado HLS IP 這里集成了HLS IP和由HLS創建的軟件驅動,目的是控制在Zynq器件上實現的IP設計。

2017-02-07 18:08:11 3207

3207

很多軟件工程師習慣于在Microsoft Visual Studio(MVS)開發環境中編程,這就帶來了一個問題,如何讓MVS支持Vivado HLS的任意精度數據類型,譬如 ap_int

2017-02-08 05:43:37 497

497

大,我是否能夠利用Vivado HLS完成這項要求較高的運算呢? 我開始從軟件方面考慮這個轉換,我開始關注軟件界面。畢竟,HLS創建專用于處理硬件接口的硬件。幸好Vivado HLS支持創建AXI slave的想法,同時工作量較少。 我發現Vivado HLS編碼限制相當合理。它支持大多數C + +語言

2017-02-09 02:15:11 310

310 本實驗練習使用的設計是實驗1并對它進行優化。 步驟1:創建新項目 1.打開Vivado HLS 命令提示符 a.在windows系統中,采用Start>All Programs>Xilinx

2017-02-09 05:07:11 411

411

在使用高層次綜合,創造高質量的RTL設計時,一個重要部分就是對C代碼進行優化。Vivado Hls總是試圖最小化loop和function的latency,為了實現這一點,它在loop

2017-11-16 14:44:58 3362

3362 隨著無線網絡的數據流量和密集度不斷增加,所有運營商都面臨著非常大的挑戰。一套好的數據壓縮算法能夠幫助運營商節省不少的網絡基礎設備的開支。使用Xilinx Vivado HLS工具評估開放式無線電設備

2017-11-17 02:25:41 1267

1267

使用Xilinx Vivado HLS(Vivado 高層次綜合)工具實現浮點復數QRD矩陣分解并提升開發效率。使用VivadoHLS可以快速、高效地基于FPGA實現各種矩陣分解算法,降低開發者

2017-11-17 17:47:43 3293

3293

目前的應用軟件通常包含有復雜的內存訪問機制,尤其是在科學計算和數字信號處理領域,內存的管理將十分復雜。我們利用Vivado HLS設計了一個簡單的例子,可以使你在一些棘手的情況下,用它來建造有效處理

2017-11-17 18:22:02 787

787 1 Vivado HLS簡介 2創建一個Vivado-HLS工程 2.1打開Vivado HLS GUI 2.2創建新工程 在 Welcome Page, 選擇Create New Project

2017-12-04 10:07:17 0

0 在實際工程中,如何利用好這一工具仍值得考究。本文將介紹使用Vivado HLS時的幾個誤區。

2018-01-10 14:33:02 19813

19813

本文內容介紹了基于用Vivado-HLS為軟件提速,供參考

2018-03-26 16:09:10 7

7 Vivado HLS 是 Xilinx 提供的一個工具,是 Vivado Design Suite 的一部分,能把基于 C 的設計 (C、C++ 或 SystemC)轉換成在 Xilinx 全可編程芯片上實現用的 RTL 設計文件 (VHDL/Verilog 或 SystemC)。

2018-06-05 10:31:00 6326

6326

在集成電路行業飛速發展的今天,縮短產品開發的周期而又不犧牲驗證過程,這不可避免地成為了商業市場的一個關鍵因素。Xilinx Vivado High Level Synthesis (即Vivado

2018-06-04 01:43:00 7171

7171

OPENCV(Open Source Computer Vision)被廣泛的使用在計算機視覺開發上。使用Vivado HLS視頻庫在zynq-7000全可編程soc上加速OPENCV 應用的開發,將大大提升我們的計算機視覺開發。

2018-11-10 10:47:49 1323

1323 了解如何使用GUI界面創建Vivado HLS項目,編譯和執行C,C ++或SystemC算法,將C設計合成到RTL實現,查看報告并了解輸出文件。

2018-11-20 06:09:00 3651

3651 了解如何生成Vivado HLS IP模塊,以便在System Generator For DSP中使用。

2018-11-20 06:08:00 2940

2940 了解如何使用Tcl命令語言以批處理模式運行Vivado HLS并提高工作效率。

該視頻演示了如何從現有的Vivado HLS設計輕松創建新的Tcl批處理腳本。

2018-11-20 06:06:00 2887

2887 Vivado HLS有助于降低整體系統功耗,降低材料成本,提高系統性能并加快設計生產率。

我們將向您展示如何使用C,C ++或SystemC創建更高效??的規范。

2018-11-27 06:43:00 3392

3392 盡管 Vivado HLS支持C、C++和System C,但支持力度是不一樣的。在v2017.4版本ug871 第56頁有如下描述。可見,當設計中如果使用到任意精度的數據類型時,采用C++ 和System C 是可以使用Vivado HLS的調試環境的,但是C 描述的算法卻是不可以的。

2019-07-29 11:07:16 5072

5072

介紹了如何利用Vivado HLS生成FIR濾波算法的HDL代碼,并將代碼添加到ISE工程中,經過綜合實現布局布線等操作后生成FPGA配置文件,下載到FPGA開發板中,Darren采用的目標板卡是Spartan-3 FPGA。

2019-07-30 17:04:24 4554

4554 接著開始正文。據觀察,HLS的發展呈現愈演愈烈的趨勢,隨著Xilinx Vivado HLS的推出,intel也快馬加鞭的推出了其HLS工具。HLS可以在一定程度上降低FPGA的入門門檻(不用編寫

2019-07-31 09:45:17 6232

6232

對于Vivado Hls來說,輸入包括Tesbench,C/C++源代碼和Directives,相應的輸出為IP Catalog,DSP和SysGen,特別的,一個工程只能有一個頂層函數用于

2021-01-02 09:45:00 4398

4398 Vivado HLS中常見的接口類型有: 1. ap_none ???????? 默認類型,該類型不適用任何I/O轉換協議,它用于表示只讀的輸入信號,對應于HDL中的wire類型。 2.

2020-12-26 11:44:10 6759

6759

Vivado HLS 2020.1將是Vivado HLS的最后一個版本,取而代之的是VitisHLS。那么兩者之間有什么區別呢? Default User Control Settings

2020-11-05 17:43:16 37066

37066 本文介紹如何一步一步將設計從SDSoC/Vivado HLS遷移到Vitis平臺。

2022-07-25 17:45:48 3057

3057

本文介紹如何一步一步將設計從SDSoC/Vivado HLS遷移到Vitis平臺。

2021-01-31 08:12:02 8

8 1.實驗目的通過例程探索Vivado HLS設計流用圖形用戶界面和TCL腳本兩種方式創建Vivado HLS項目用各種HLS指令綜合接口優化Vivado HLS設計來滿足各種約束用不用的指令來探索

2021-11-06 09:20:58 6

6 Vitis HLS 是一種高層次綜合工具,支持將 C、C++ 和 OpenCL 函數硬連線到器件邏輯互連結構和 RAM/DSP 塊上。Vitis HLS 可在Vitis 應用加速開發流程中實現硬件

2022-05-25 09:43:36 1930

1930 HLS的FPGA開發方法是只抽象出可以在C/C++環境中輕松表達的應用部分。通過使用Vivado(Xilinx)或Intel(Quartus)工具,HLS工具流程基本上可用于任何BittWare板。

2022-08-02 09:18:32 1340

1340

對于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統一將HLS集成到Vitis里了,集成之后增加了一些功能,同時將這部分開源出來了。Vitis HLS是Vitis AI重要組成部分,所以我們將重點介紹Vitis HLS。

2022-09-02 09:06:23 2857

2857 vivado本身集成了opencv庫以及hls視頻庫了,opencv不能被綜合導出為RTL電路,hls視頻庫的功能有所欠缺,因此引入xfopencv作為既可以被綜合導出為RTL電路,也能夠實現opencv豐富的功能。

2022-09-09 15:07:05 997

997 對于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統一將HLS集成到Vitis里了,集成之后增加了一些功能,同時將這部分開源出來了。Vitis HLS是Vitis AI重要組成部分,所以我們將重點介紹Vitis HLS。

2023-01-15 11:27:49 1317

1317 是Vitis HLS。在Vivado 2020版本中替代原先的Vivado HLS, 功能略有差異。 HLS 的機理 ? ?簡單地講,HLS采樣類似C語言來設計FPGA 邏輯。但是要實現這個目標,還是不容易

2023-01-15 12:10:04 2968

2968 AMD Vitis HLS 工具允許用戶通過將 C/C++ 函數綜合成 RTL,輕松創建復雜的 FPGA 算法。Vitis HLS 工具與 Vivado Design Suite(用于綜合、布置和布線)及 Vitis 統一軟件平臺(用于所有異構系統設計和應用)高度集成。

2023-04-23 10:41:01 652

652

Xilinx平臺的Vivado HLS 和 Vitis HLS 使用的 export_ip 命令會無法導出 IP

2023-07-07 14:14:57 338

338

)hls_fft.h。實際上,在HLS中調用該庫實現FFT,其實是Vivado中的那個FFT核實現的,但是HLS中的配置和給定輸入輸出數據比較方便,并且對其外部封裝其他類型的總線接口非常容易。

2023-07-11 10:05:35 580

580

電子發燒友網站提供《UltraFast Vivado HLS方法指南.pdf》資料免費下載

2023-09-13 11:23:19 0

0 電子發燒友網站提供《將VIVADO HLS設計移植到CATAPULT HLS平臺.pdf》資料免費下載

2023-09-13 09:12:46 2

2 電子發燒友網站提供《使用Vivado高層次綜合(HLS)進行FPGA設計的簡介.pdf》資料免費下載

2023-11-16 09:33:36 0

0

電子發燒友App

電子發燒友App

評論