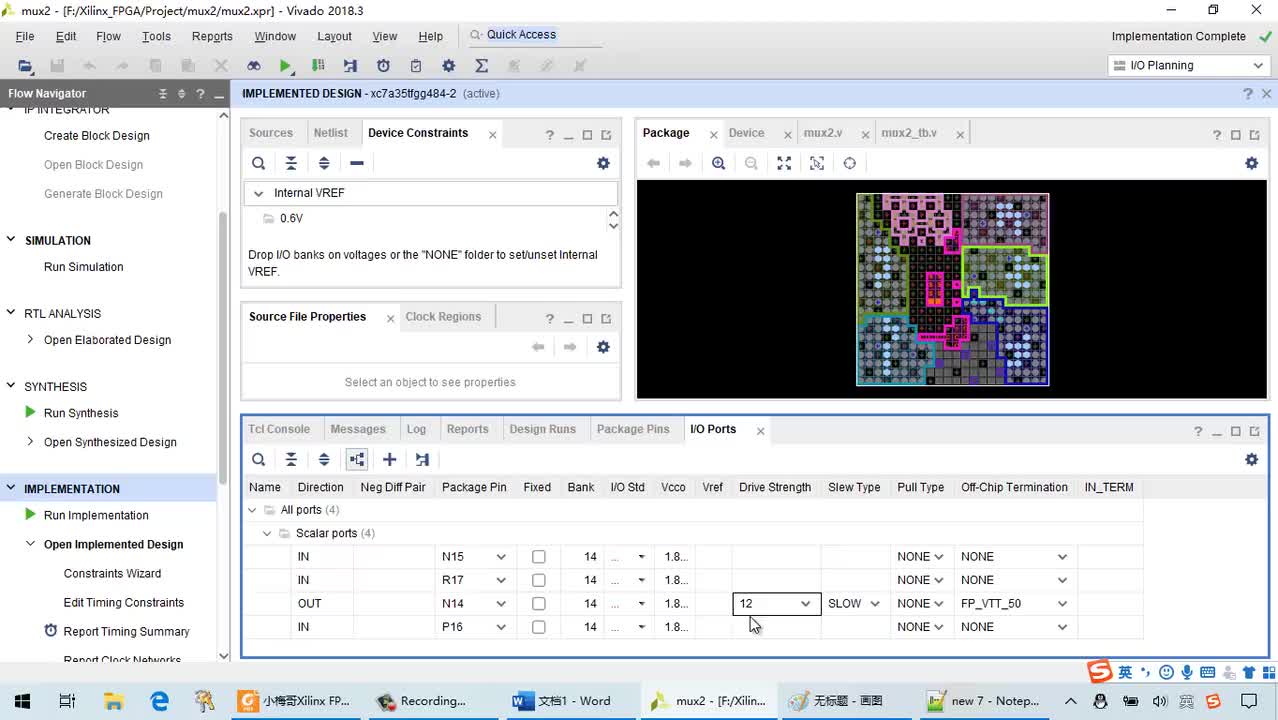

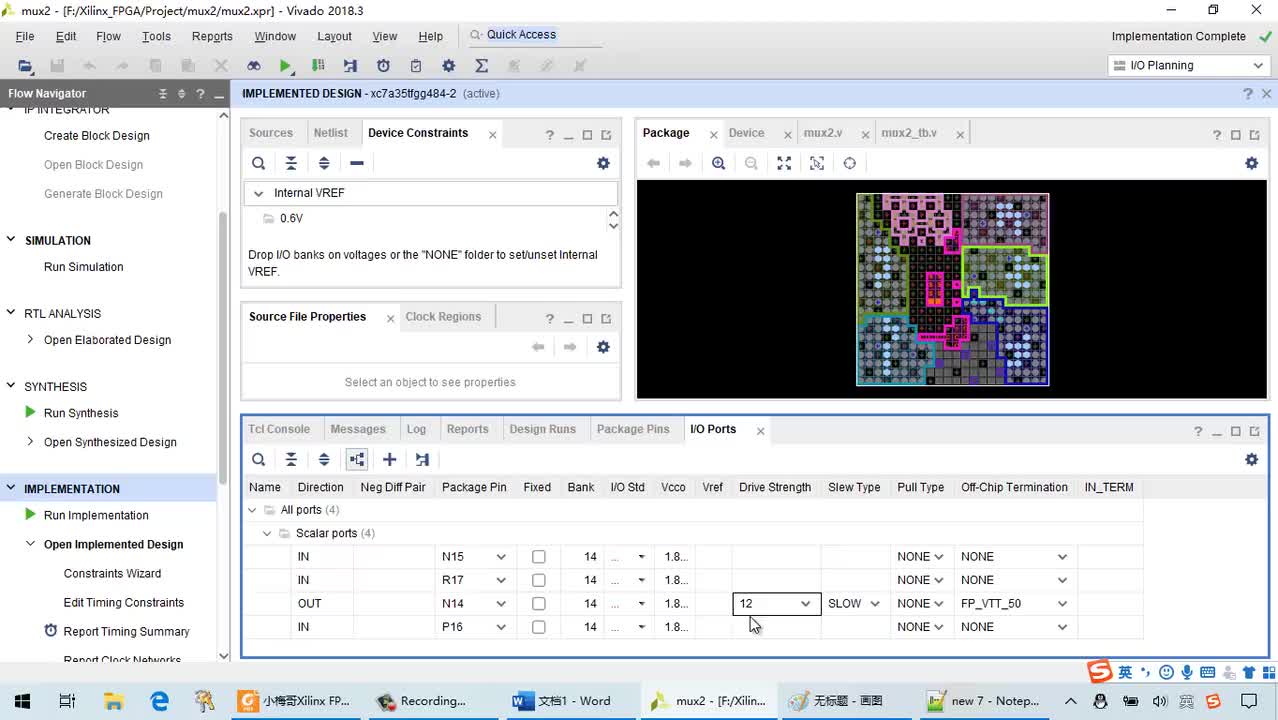

以Xilinx公司最新的Vivado FPGA集成開發(fā)環(huán)境為基礎(chǔ),將數(shù)字邏輯設(shè)計(jì)與硬件描述語言Verilog HDL相結(jié)合,循序漸進(jìn)地介紹了基于Xilinx Vivado的數(shù)字邏輯實(shí)驗(yàn)的基本過程和方法。書中包含了大量的設(shè)計(jì)實(shí)例,內(nèi)容翔實(shí)、系統(tǒng)、全面。

2017-12-27 06:47:00 13971

13971 基于FPGA vivado 17.2 的數(shù)字鐘設(shè)計(jì)

2018-06-08 09:41:47 10186

10186

Xilinx的新一代設(shè)計(jì)套件Vivado相比上一代產(chǎn)品ISE,在運(yùn)行速度、算法優(yōu)化和功能整合等很多方面都有了顯著地改進(jìn)。但是對(duì)初學(xué)者來說,新的約束語言XDC以及腳本語言Tcl的引入則成為了快速掌握Vivado使用技巧的最大障礙,以至于兩年多后的今天,仍有很多用戶缺乏升級(jí)到Vivado的信心。

2022-09-14 09:09:56 1526

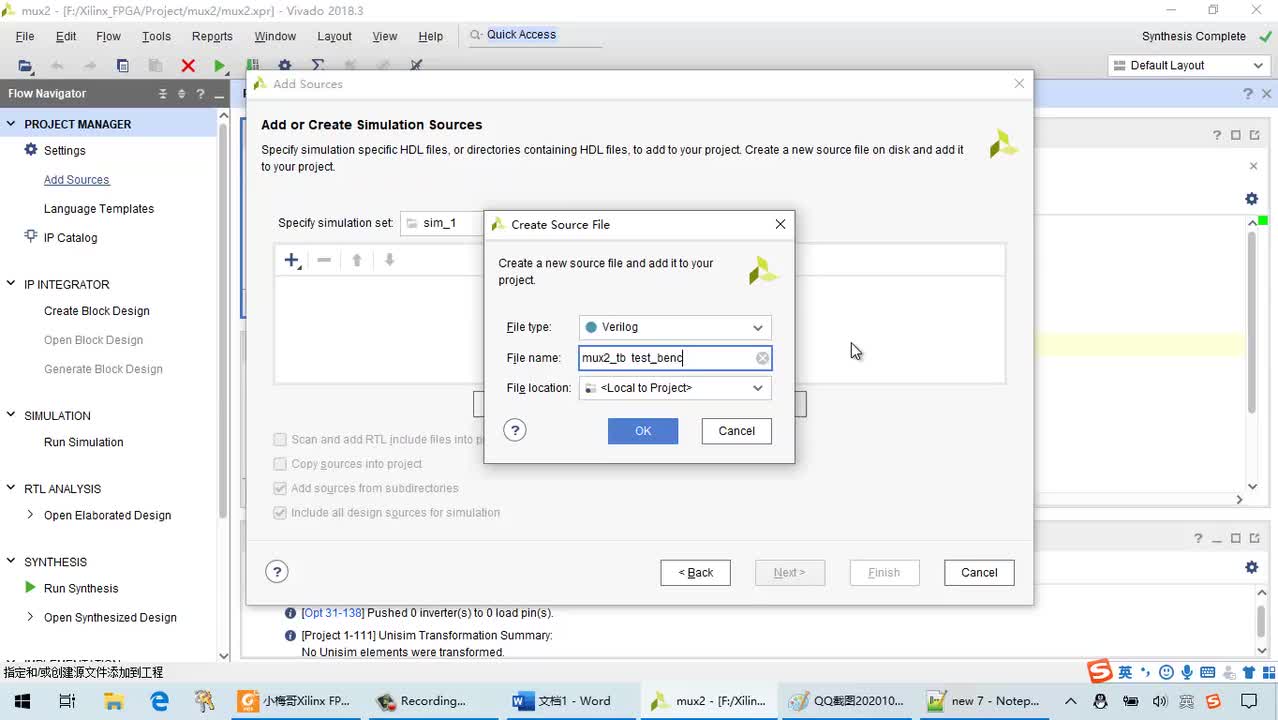

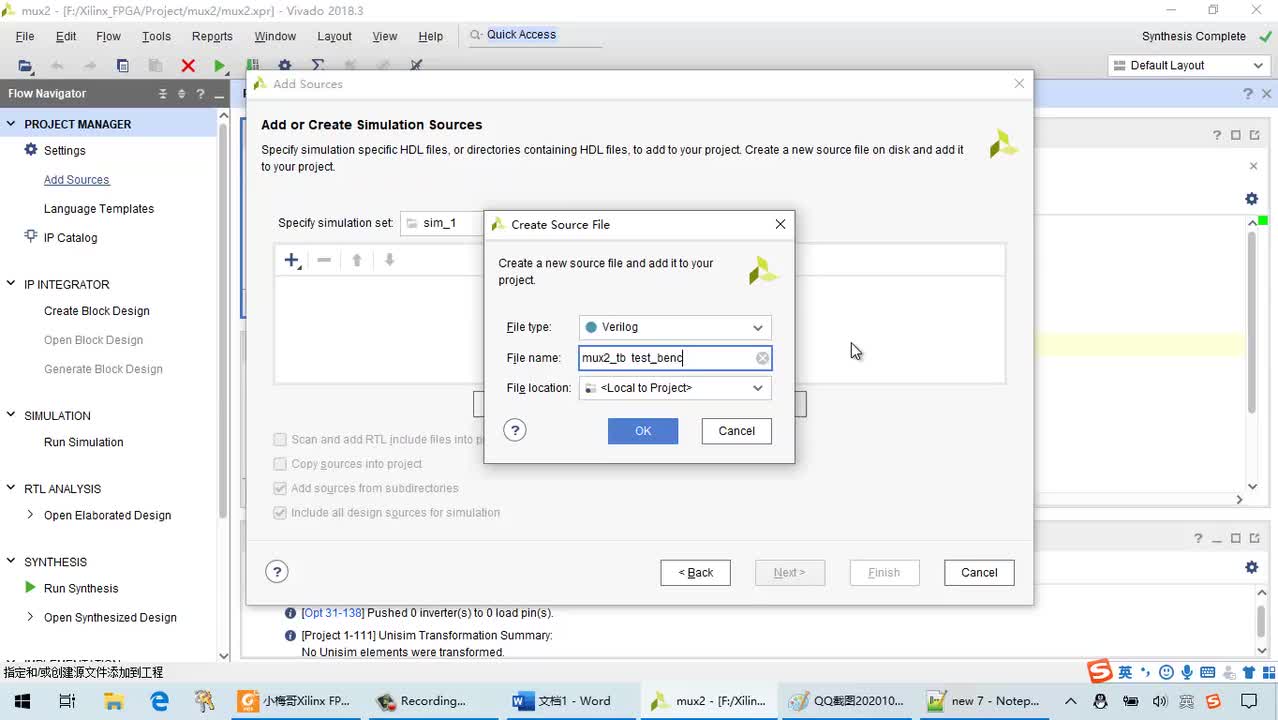

1526 雙擊桌面圖標(biāo)打開Vivado 2017.2,或者選擇開始>所有程序>Xilinx Design Tools> Vivado 2017.2>Vivado 2017.2;

2023-07-30 09:39:11 403

403

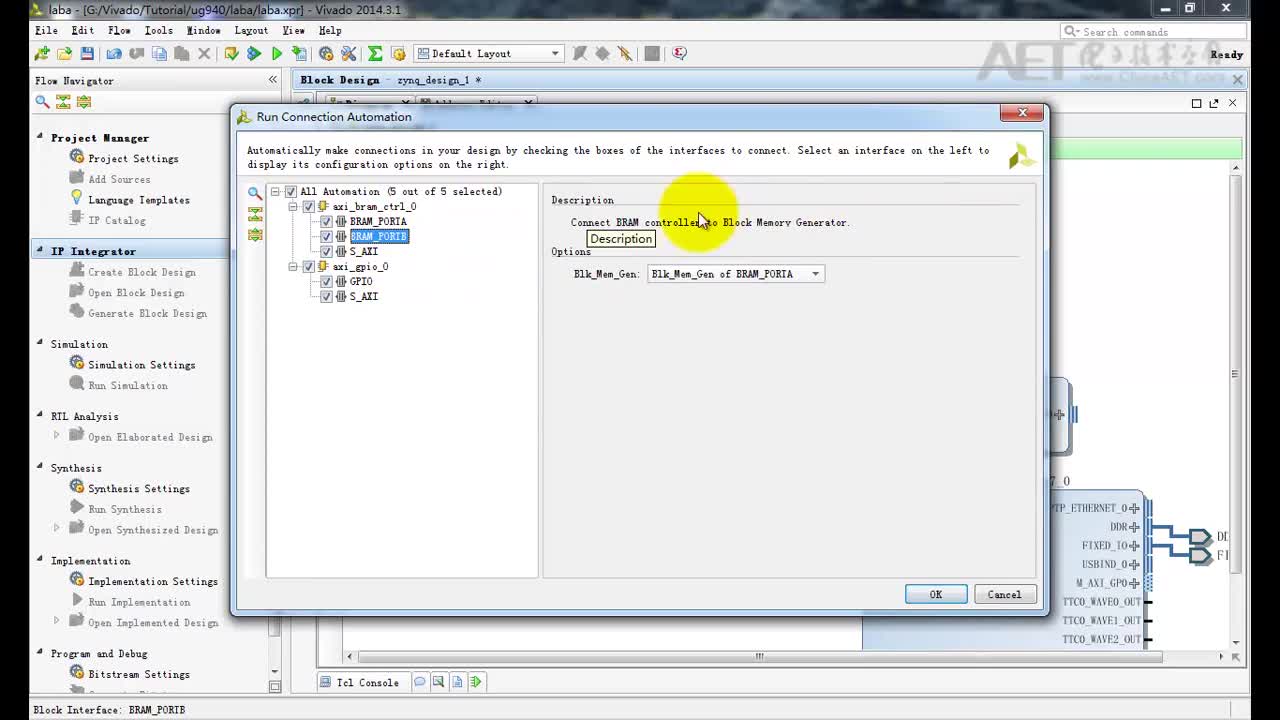

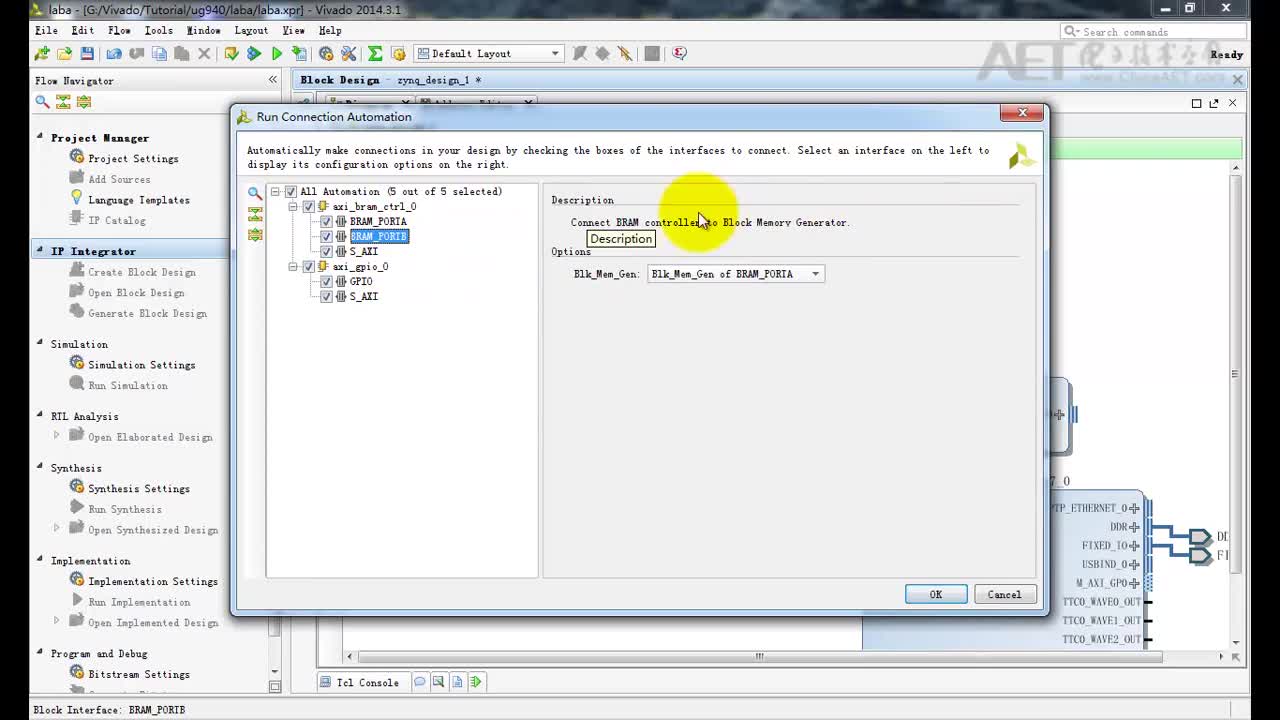

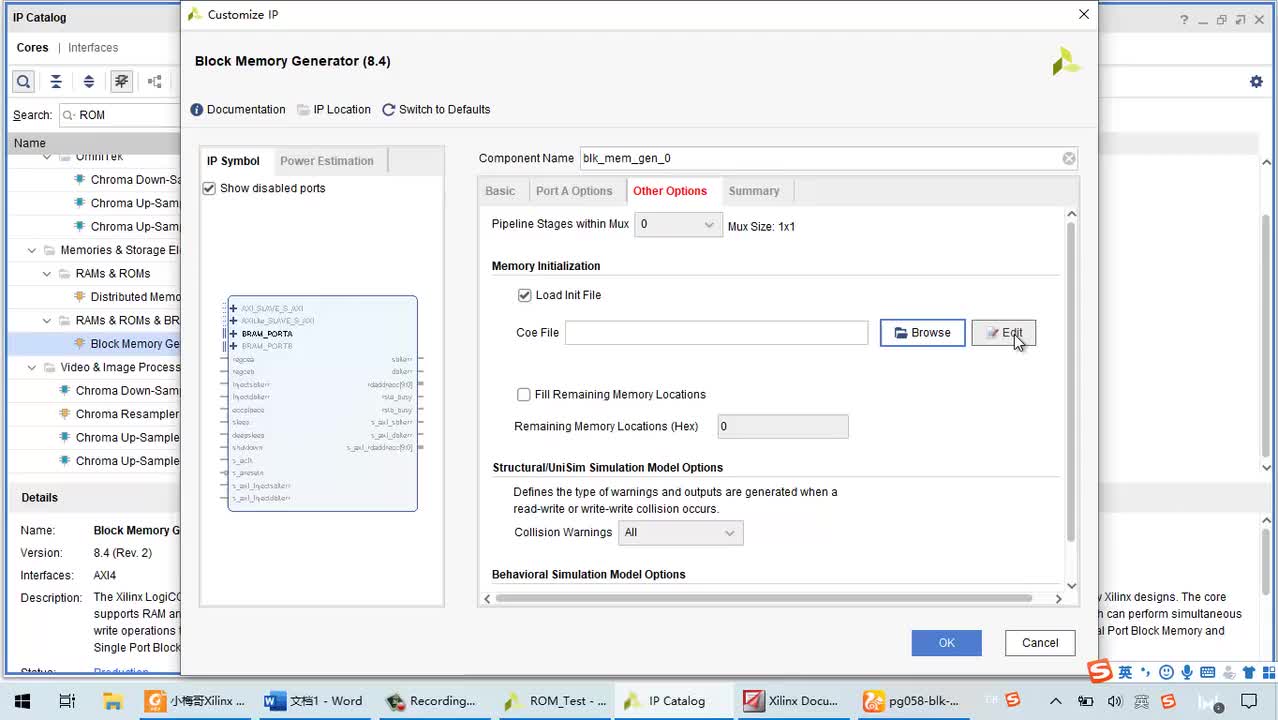

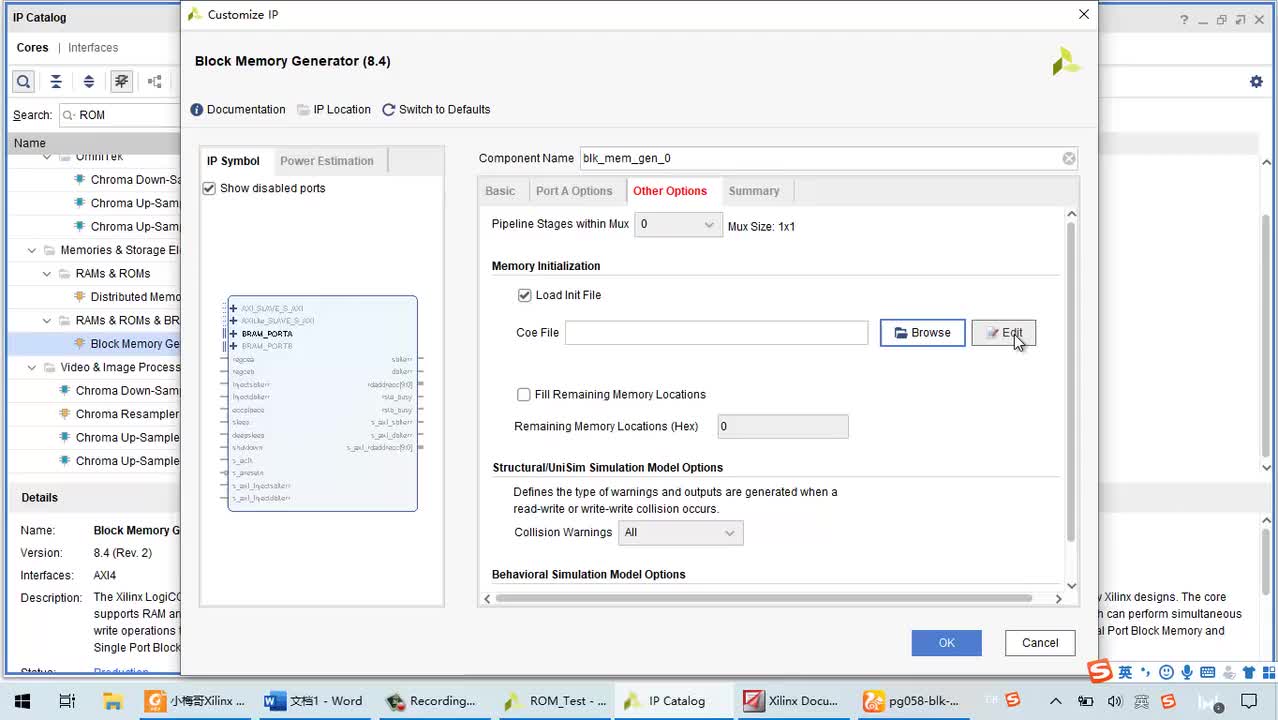

Xilinx Block Memory Generator(BMG)是一個(gè)先進(jìn)的內(nèi)存構(gòu)造器,它使用Xilinx fpga中的嵌入式塊RAM資源生成面積和 性能優(yōu)化的內(nèi)存。

2023-11-14 17:49:43 736

736

{simulate.log}”INFO:[USF-XSim -8]加載模擬器功能Vivado Simulator 2014.3ERROR:[Simtcl 6-50]模擬引擎無法啟動(dòng):未找到模擬的有效許可證。請(qǐng)運(yùn)行Vivado

2018-12-12 10:55:17

您好,我在vivado 2014.3設(shè)計(jì)套件安裝時(shí)遇到了問題。我嘗試了Windows 64的Web安裝和完整的產(chǎn)品安裝,在我下載它們并單擊安裝文件后沒有任何反應(yīng)。我正在使用Windows 7 64位

2018-12-12 10:44:53

大家好我無法在我的lapton上設(shè)置Vivado 2014.4和2014.3和2014.2。當(dāng)設(shè)置為10%時(shí),會(huì)彈出錯(cuò)誤窗口,安裝文件時(shí)遇到以下致命錯(cuò)誤:C:\ Xilinx \ Vivado

2018-12-11 11:27:15

我一直在跟隨一個(gè)程序,讓我們的老師加載新的Vivado以支持新的FPGA芯片。其他人都取得了成功。我已經(jīng)在我的Windows 10 64位計(jì)算機(jī)上加載了Vivado 2017.4,它在我的桌面上有一

2019-01-04 11:14:26

大家好,這對(duì)我來說是新的,它只在OOC合成設(shè)計(jì)的地點(diǎn)/路線運(yùn)行期間發(fā)生,并且僅在新的Vivado 2014.3上發(fā)生。它總是必須像這樣嗎? 2014.3中的開關(guān)/設(shè)置是否有變化?[選項(xiàng)31-38

2018-10-25 15:18:39

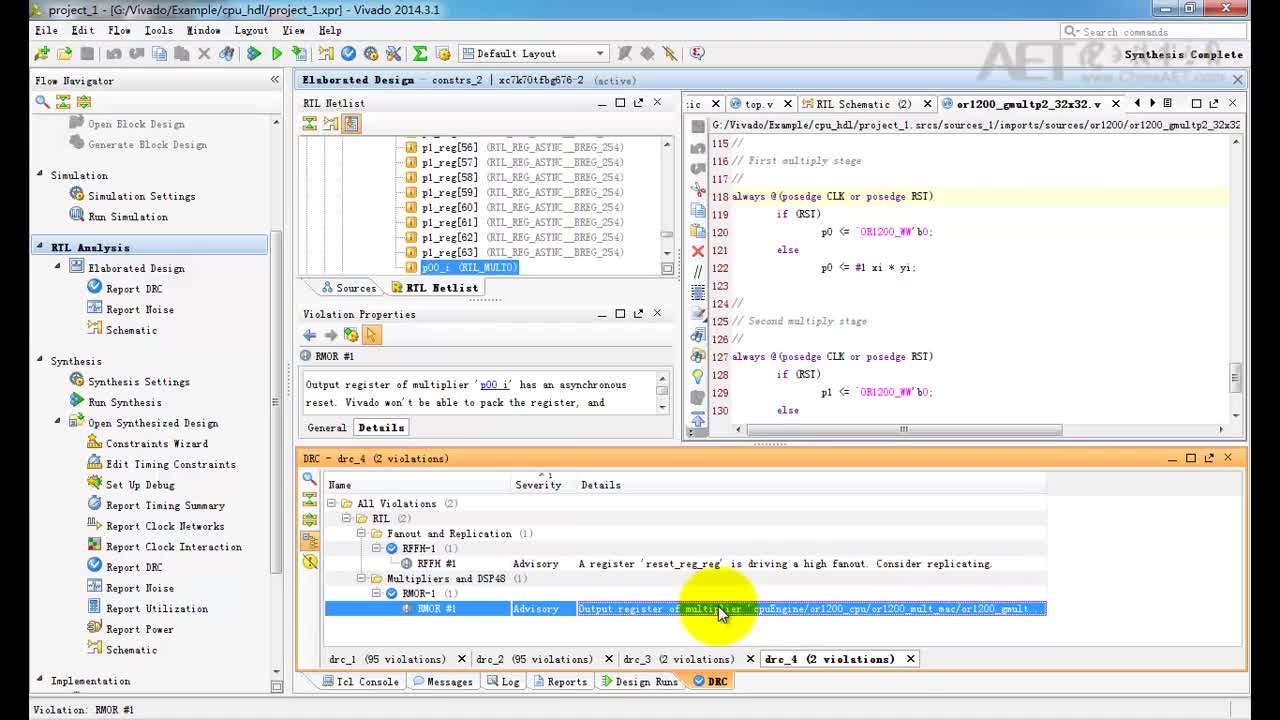

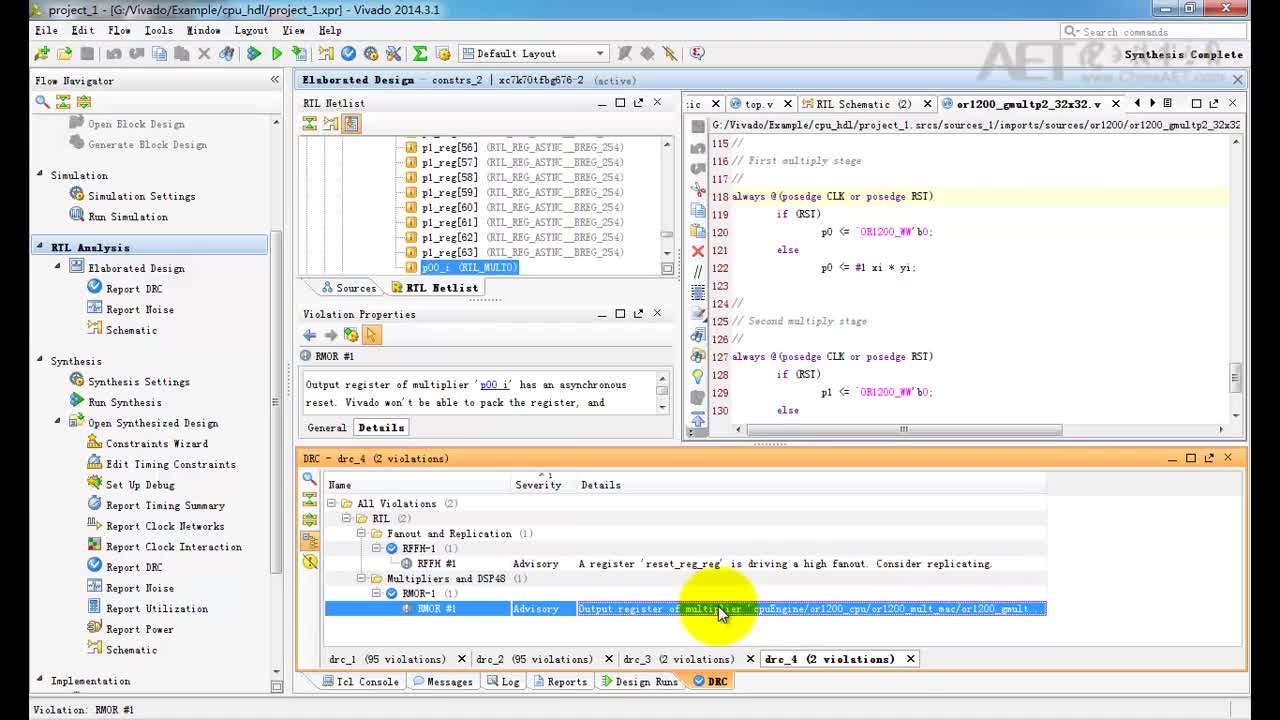

你好,自從我更新到新版本的Vivado 2014.3后,我無法寫入以前工作項(xiàng)目的比特流。我現(xiàn)在收到以下錯(cuò)誤消息:[DRC 23-20]規(guī)則違反(REQP-1584)GTxE2

2020-07-25 09:48:53

嗨,我下載Vivado2014.3并嘗試申請(qǐng)30天的評(píng)估許可證!當(dāng)我通過vivado許可管理器工具連接到xilinx許可證網(wǎng)站時(shí),我將網(wǎng)站顯示為附件。1)基于證書的許可證只有3個(gè):ISE

2018-12-06 11:31:19

大家好,我最近將我的設(shè)計(jì)從2014.2遷移到了2014.3。它在2014.2上很容易合成和實(shí)現(xiàn),但升級(jí)到2014.3后我再也無法實(shí)現(xiàn)了。由于網(wǎng)站無法使用,無法放置IO會(huì)產(chǎn)生一個(gè)奇怪的錯(cuò)誤!雖然只分配

2020-04-17 07:00:58

Vivado中xilinx_courdic IP核(求exp指數(shù)函數(shù))使用

2021-03-03 07:35:03

嗨,我試過安裝Vivado(2014.2或2014.3,同樣的問題),我只是我電腦的用戶。安裝程序需要管理員權(quán)限。我知道密碼并且它沒問題但是在安裝之后用戶沒有任何快捷方式或圖標(biāo)來運(yùn)行Vivado。我

2019-03-20 11:54:56

如上圖所示用的是Vivado2014.4,最后生成完bit文件后,顯示了這個(gè)。結(jié)溫過高?仔細(xì)看report里面電流竟然30+A。。。我想問一下大概是什么原因?qū)е铝诉@種狀況的出現(xiàn)呢,然后解決這個(gè)問題那些地方的代碼可以優(yōu)化呢?剛學(xué)FPGA不久,望各位大蝦指教

2015-03-23 17:01:15

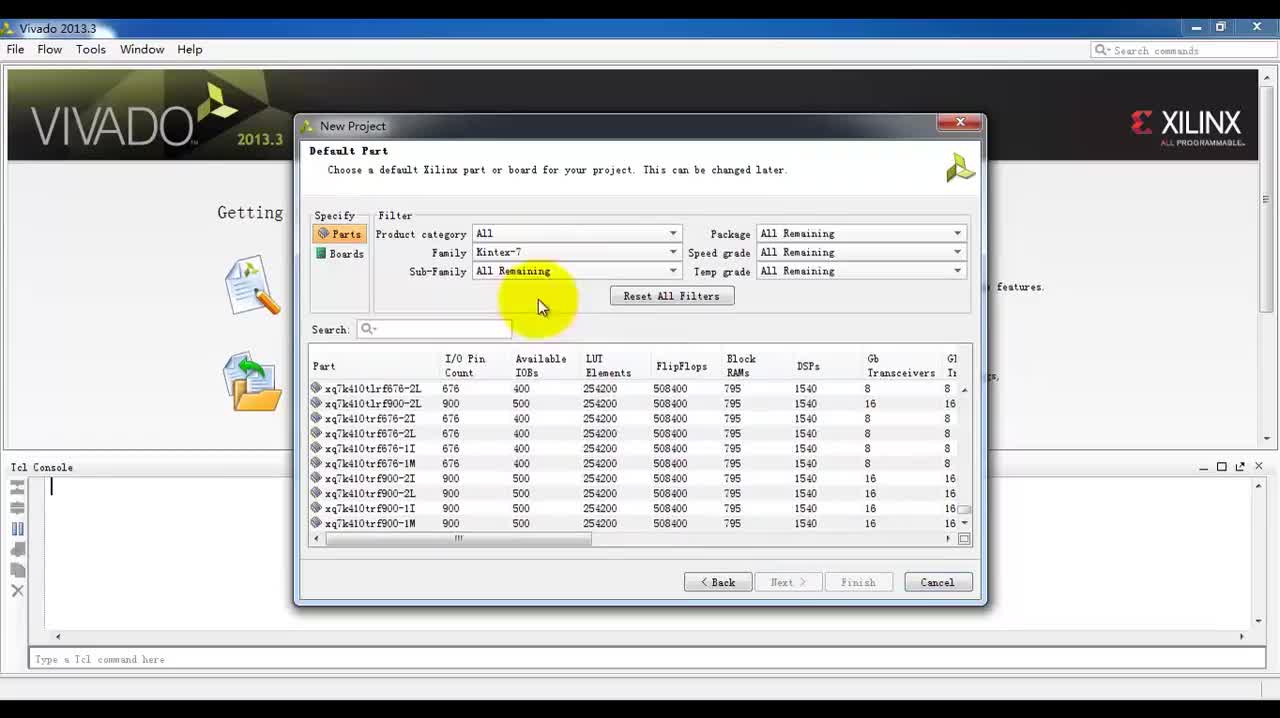

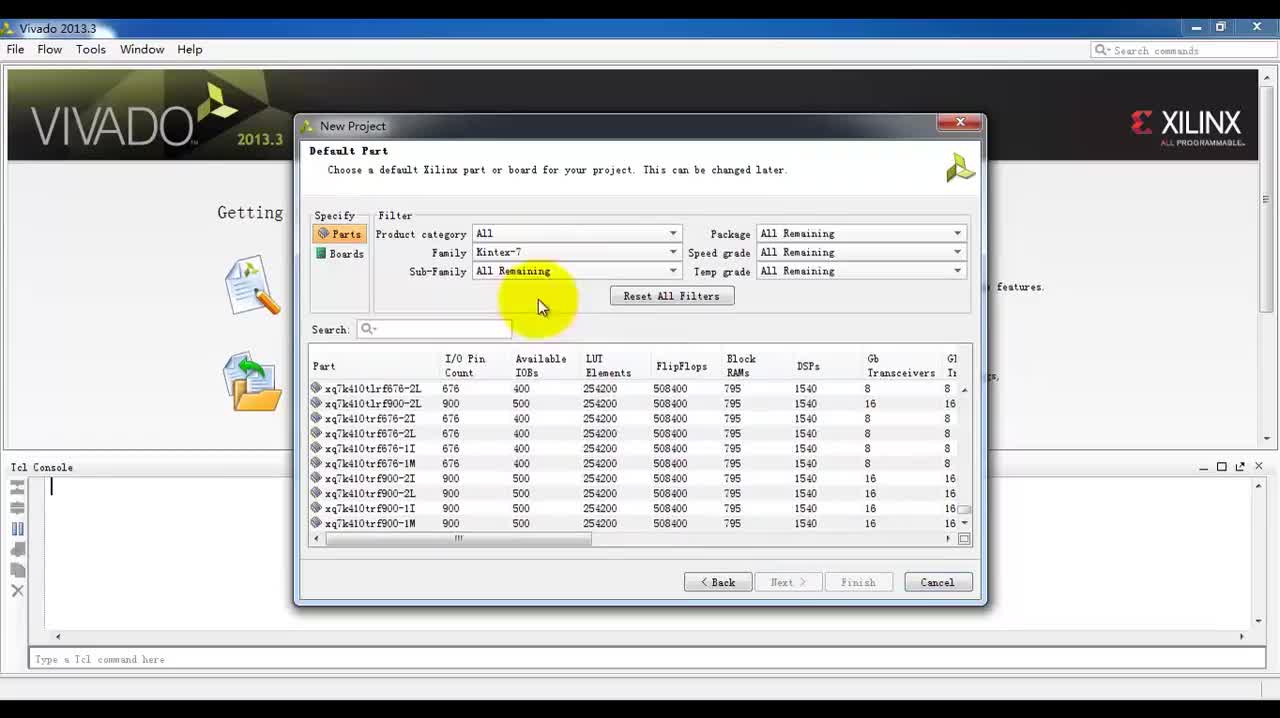

開發(fā)設(shè)計(jì)流程。話不多說,上貨。Xilinx FPGA Vivado 開發(fā)流程在做任何設(shè)計(jì)之前,我們都少不了一個(gè)工作,那就是新建工程,我們?cè)O(shè)計(jì)的一些操作,必須在工程下完成,那么接下來就向大家介紹一下新建工程的步驟

2023-04-13 15:18:52

開發(fā)過程中的一個(gè)重要特點(diǎn),這就要求設(shè)計(jì)者從一開始就要非常認(rèn)真細(xì)致,否則后續(xù)的很多工作量可能就是不斷的返工。圖1.32 FPGA開發(fā)流程 基于Xilinx的Vivado開發(fā)工具,我們對(duì)以上開發(fā)流程所涉

2019-04-01 17:50:52

轉(zhuǎn)自:VIVADO時(shí)序分析練習(xí)時(shí)序分析在FPGA設(shè)計(jì)中是分析工程很重要的手段,時(shí)序分析的原理和相關(guān)的公式小編在這里不再介紹,這篇文章是小編在練習(xí)VIVADO軟件時(shí)序分析的筆記,小編這里

2018-08-22 11:45:54

分享一點(diǎn),xilinx FPGA的資料,回饋原子的論壇Vivado-Design-Suite入門介紹.pdf (764.48 KB )Verilog_HDL_那些事兒_時(shí)序篇.pdf (9.46 MB )verilog HDL基礎(chǔ)開發(fā)指南.pdf (1.84 MB )

2019-04-23 04:04:00

哪位大神能夠分享一下關(guān)于xilinx vivado 2013.4 的教程啊,小弟感激不敬!!!

2014-03-26 21:38:02

大家好,今天我將Vivado升級(jí)到2017年的Update 1,以便訪問XC7S25,XC7A12和XC7A25設(shè)備。據(jù)我所知,更新成功完成; 2017.4是我唯一的Vivado版本,安裝程序在重新

2018-12-29 11:14:43

Cortex-M1 DesignStart?現(xiàn)場(chǎng)可編程門陣列-Xilinx版本包提供了一種在Xilinx Vivado設(shè)計(jì)環(huán)境中使用Cortex-M1處理器的簡(jiǎn)單方法。

Cortex-M1處理器

2023-08-16 06:10:25

Cortex-M3 DesignStart?現(xiàn)場(chǎng)可編程門陣列-Xilinx版封裝提供了一種在Xilinx Vivado設(shè)計(jì)環(huán)境中使用Cortex-M3處理器的簡(jiǎn)單方法。

Cortex-M3處理器專為

2023-08-12 07:02:46

申請(qǐng)理由:項(xiàng)目描述:本人之前一直從事Altera FPGA的學(xué)習(xí)套件的教程資料研發(fā),如今轉(zhuǎn)向Xilinx,考慮Xilinx現(xiàn)在主推的工具是vivado,而S6系列芯片無法使用,為了使自己的教程資料

2016-10-11 18:15:20

您好,我想下載Xilinx Vivado 2017.1但是,每次我收到以下錯(cuò)誤:“由于您的帳戶導(dǎo)出合規(guī)性驗(yàn)證失敗,我們無法滿足您的要求。”誰能幫我?提前致謝以上來自于谷歌翻譯以下為原文Hello

2018-12-27 10:41:52

請(qǐng)問一下Xilinx公司發(fā)布的vivado具體的作用是什么,剛剛接觸到,以前一直用quartus ii,沒有使用過ise,后來今天聽說了vivado,不知道是做什么用的,希望大家都能參與討論中,謝謝。

2015-04-15 16:51:00

,但現(xiàn)在有了Vivado,我沒有看到這樣的應(yīng)用程序我希望Xilinx不要像許多其他應(yīng)用程序那樣放棄這個(gè)應(yīng)用程序以上來自于谷歌翻譯以下為原文Hello everyone Can I Install

2018-12-27 10:57:02

。在Ubuntu上,我嘗試了許多版本的Vivado(2014.3,2015.1)并且沒有任何改變。我每次都有同樣的錯(cuò)誤。也許有人有同樣的問題,可以幫助我嗎?提前致謝馬丁以上來自于谷歌翻譯以下為原文HiI

2018-12-20 11:10:41

Digilent USB-JTAG電纜在同一臺(tái)PC上運(yùn)行正常。多個(gè)* Xilinx *品牌USB電纜在VIvado和ISE下運(yùn)行良好。我正在使用Windows 7 64位和Vivado 2014.3有沒有

2020-06-01 06:06:09

偏移0x100開始編程FPGA二進(jìn)制。Spansion Flash的編程緩沖區(qū)大小為512字節(jié)。我生成了MCS,偏移量為0x100。但是,當(dāng)嘗試使用Xilinx Vivado工具對(duì)Flash進(jìn)行編程

2020-06-09 10:28:14

com.xilinx.sdk.targetmanager.TMException:與Board失敗的連接 未知錯(cuò)誤Occured Cable未連接到主機(jī)at com.xilinx.sdk.targetmanager.internal.TM.isFPGA

2018-12-25 11:11:02

我正在嘗試做一個(gè)需要在七段顯示器上顯示“數(shù)字時(shí)鐘”的項(xiàng)目。我正在通過vivado 2014.3進(jìn)行編碼并使用nexys4 FPGA。問題是當(dāng)我嘗試根據(jù)每秒,分鐘,小時(shí)的狀態(tài)從我的ROM中將一個(gè)值放入

2020-03-26 09:50:23

是否可以下載更新?或者我是否需要重新下載整個(gè)2014.3才能升級(jí)?以上來自于谷歌翻譯以下為原文Is it possible to download just an update?Or do I need to re-download the entire 2014.3 to upgrade?

2018-12-12 10:53:04

用于Xilinx FPGA的Keysight E5910A串行鏈路優(yōu)化工具

2019-10-16 10:49:30

大家好,我已經(jīng)進(jìn)入論壇同樣的問題,但找不到解決方案。我開始在我的Windows7 64位主機(jī)上安裝Vivado 2014.3 / WebPack許可證(我們使用的是Zedboard HW目標(biāo)

2018-12-13 10:26:13

你好,我安裝了

Xilinx vivado 2015.2,我將開始為USRP x310編寫計(jì)算引擎。為此,我需要一個(gè)完整的

Xilinx設(shè)計(jì)許可證。首先,我想澄清一下本網(wǎng)站末尾發(fā)布的許可是否合適,因?yàn)槲?/div>

2020-05-06 07:58:17

賽靈思(Xilinx)公司宣布推出全新的Vivado設(shè)計(jì)套件。Xilinx全球高級(jí)副總裁湯立人表示,Vivado不是已有15年歷史的ISE設(shè)計(jì)套件的再升級(jí)(ISE采用的是當(dāng)時(shí)極富創(chuàng)新性的基于時(shí)序的布局布線引

2012-06-19 17:50:14 824

824 本書系統(tǒng)地論述了Xilinx FPGA開發(fā)方法、開發(fā)工具、實(shí)際案例及開發(fā)技巧,內(nèi)容涵蓋Xilinx器件概述、Verilog HDL開發(fā)基礎(chǔ)與進(jìn)階、Xilinx FPGA電路原理與系統(tǒng)設(shè)計(jì)

2012-07-31 16:20:42 11268

11268

Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高層次綜合 (HLS) 進(jìn)行 FPGA 設(shè)計(jì)的簡(jiǎn)介

2016-01-06 11:32:55 65

65 及 Xilinx 技術(shù)專家共聚一堂。 在這為期一天的活動(dòng)中,您可以學(xué)習(xí)各種有關(guān) Vivado 的高級(jí)功能、使用技巧及設(shè)計(jì)竅門,以提升您的 FPGA/SoC 設(shè)計(jì)生產(chǎn)力: 主題演講將涵蓋行業(yè)趨勢(shì)和 Xilinx

2017-02-08 06:04:03 204

204 美國(guó)賽靈思官方授權(quán)培訓(xùn)伙伴依元素科技,以賽靈思最新的客戶培訓(xùn)課程,通過Webex在線舉辦免費(fèi)培訓(xùn)。近期推出的在線免費(fèi)培訓(xùn)是 “Vivado設(shè)計(jì)套件工具流程”。 Xilinx采用先進(jìn)的 EDA 技術(shù)

2017-02-08 11:58:12 423

423 如果你想要更快的運(yùn)行時(shí)間,你會(huì)發(fā)現(xiàn)在Vivado 2014.3中多核CPU的支持和物理優(yōu)化可以多線程進(jìn)行 如果你想要更簡(jiǎn)單的AXI4集成,你會(huì)找到全自動(dòng)

2017-02-09 09:03:11 197

197 隨著xilinx公司進(jìn)入20nm工藝,以堆疊的方式在可編程領(lǐng)域一路高歌猛進(jìn),與其配套的EDA工具——新一代高端FPGA設(shè)計(jì)軟件VIVADO也備受關(guān)注和飽受爭(zhēng)議。

2017-02-11 19:08:00 4986

4986 Xilinx FPGA的Maxim參考設(shè)計(jì)

2017-10-31 09:59:24 23

23 使用Xilinx Vivado HLS(Vivado 高層次綜合)工具實(shí)現(xiàn)浮點(diǎn)復(fù)數(shù)QRD矩陣分解并提升開發(fā)效率。使用VivadoHLS可以快速、高效地基于FPGA實(shí)現(xiàn)各種矩陣分解算法,降低開發(fā)者

2017-11-17 17:47:43 3293

3293

兩種方式可顯示該頁面: 右鍵單擊項(xiàng)目瀏覽器窗口中FPGA終端下的程序生成規(guī)范,從快捷菜單中選擇新建?編譯,打開編譯屬性對(duì)話框。在類別列表中選擇Xilinx選項(xiàng),可顯示該頁。 如FPGA程序生成

2017-11-17 19:07:06 2047

2047 資源、速度和功耗是FPGA設(shè)計(jì)中的三大關(guān)鍵因素。隨著工藝水平的發(fā)展和系統(tǒng)性能的提升,低功耗成為一些產(chǎn)品的目標(biāo)之一。功耗也隨之受到越來越多的系統(tǒng)工程師和FPGA工程師的關(guān)注。Xilinx新一代開發(fā)工具Vivado針對(duì)功耗方面有一套完備的方法和策略,本文將介紹如何利用Vivado進(jìn)行功耗分析和優(yōu)化。

2017-11-18 03:11:50 4873

4873 Xilinx的新一代設(shè)計(jì)套件Vivado相比上一代產(chǎn)品ISE,在運(yùn)行速度、算法優(yōu)化和功能整合等很多方面都有了顯著地改進(jìn)。但是對(duì)初學(xué)者來說,新的約束語言XDC以及腳本語言Tcl的引入則成為了快速掌握

2017-11-18 03:52:01 4675

4675

賽靈思公司(Xilinx)今天宣布推出可編程行業(yè)唯一 SoC 增強(qiáng)型設(shè)計(jì)套件Vivado設(shè)計(jì)套件 的2014.3版本、SDK 和最新 UltraFast 嵌入式設(shè)計(jì)方法指南,為 Zynq-7000

2018-09-06 16:07:00 1466

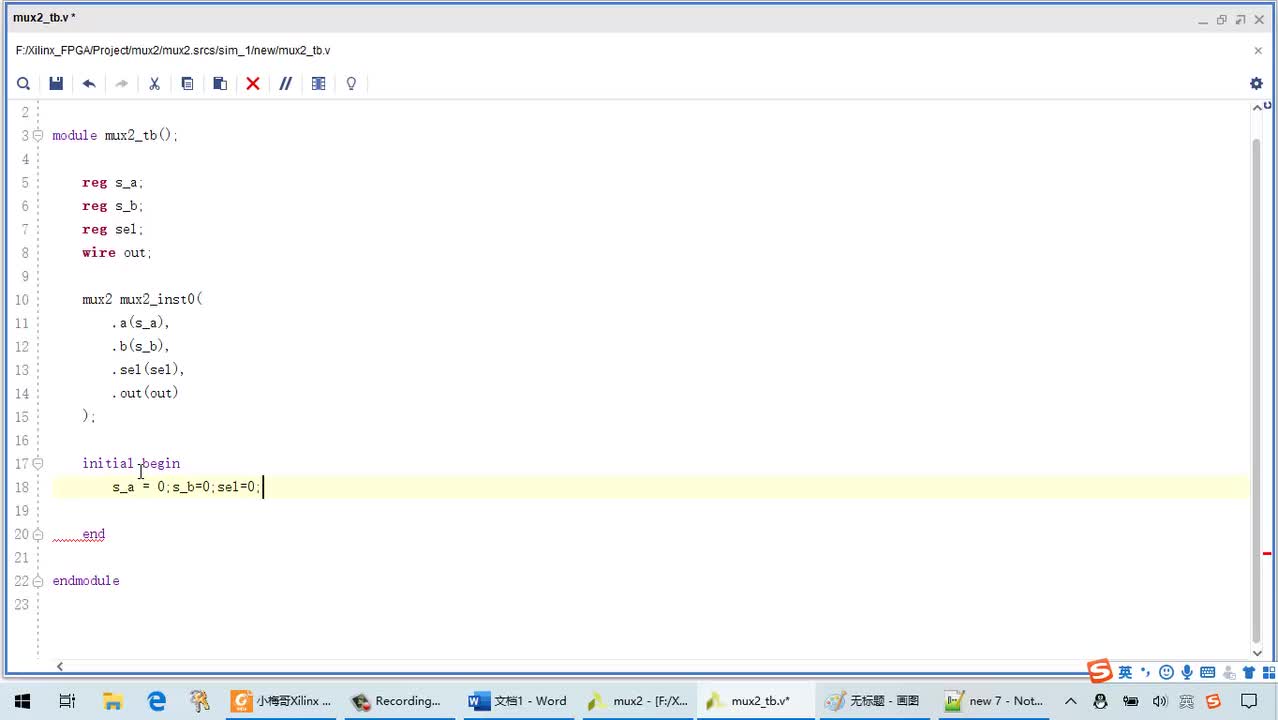

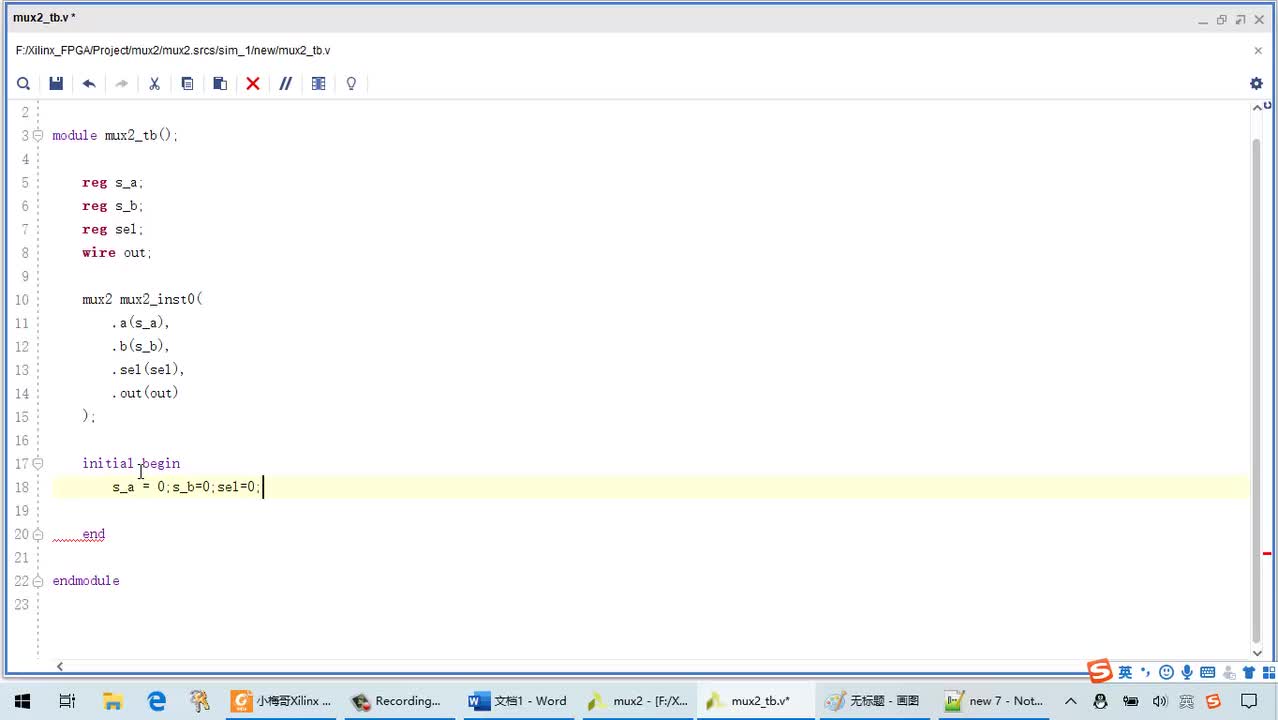

1466 Vivado不僅是xlinx公司的FPGA設(shè)計(jì)工具,用它還可以學(xué)習(xí)Verilog描述,你造嗎?

2018-09-20 09:29:22 9427

9427 了解如何利用Xilinx成本優(yōu)化的FPGA和SoC產(chǎn)品組合的最新增強(qiáng)功能。

2018-11-28 06:20:00 2086

2086 了解如何使用Vivado設(shè)計(jì)套件的電路板感知功能快速配置和實(shí)施針對(duì)Xilinx評(píng)估板的設(shè)計(jì)。

2018-11-26 06:03:00 3062

3062 中國(guó)大學(xué)MOOC

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用。

2019-08-06 06:12:00 3450

3450

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用。

2019-12-05 07:06:00 2166

2166

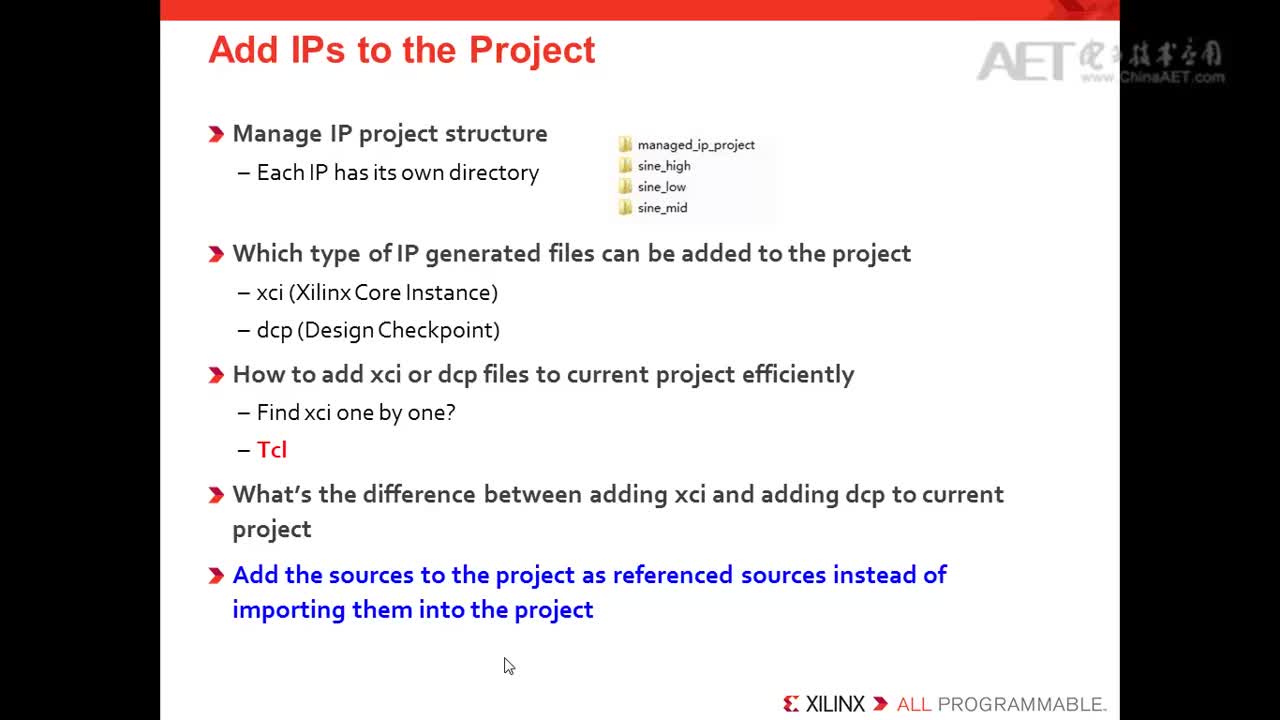

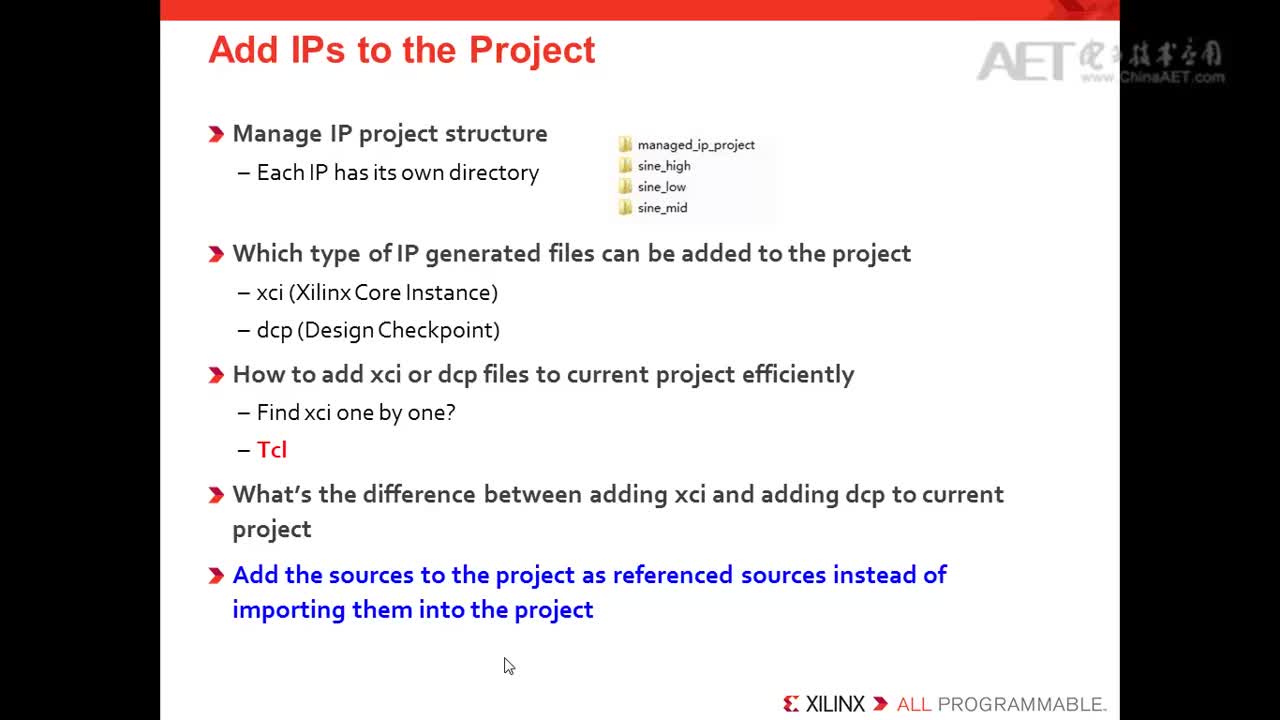

Tcl介紹 Vivado是Xilinx最新的FPGA設(shè)計(jì)工具,支持7系列以后的FPGA及Zynq 7000的開發(fā)。與之前的ISE設(shè)計(jì)套件相比,Vivado可以說是全新設(shè)計(jì)的。無論從界面、設(shè)置、算法

2020-11-17 17:32:26 2112

2112 ? Xilinx公司的FPGA中有著很多的有用且對(duì)整個(gè)工程很有益處的IP核,比如數(shù)學(xué)類的IP核,數(shù)字信號(hào)處理使用的IP核,以及存儲(chǔ)類的IP核,本篇文章主要介紹BRAM ?IP

2020-12-29 15:59:39 9496

9496 Xilinx7系列FPGA包括四個(gè)FPGA系列,它們都是為最低功耗而設(shè)計(jì)的,以使一個(gè)通用設(shè)計(jì)能夠跨系列擴(kuò)展以獲得最佳的功率、性能和成本。斯巴達(dá)?-7系列是7系列產(chǎn)品中密度最低、成本最低的入門級(jí)產(chǎn)品

2020-12-09 14:49:00 24

24 Xilinx7系列FPGA包括四個(gè)FPGA系列,它們都是為最低功耗而設(shè)計(jì)的,以使一個(gè)通用設(shè)計(jì)能夠跨系列擴(kuò)展以獲得最佳的功率、性能和成本。斯巴達(dá)?-7系列是7系列產(chǎn)品中密度最低、成本最低的入門級(jí)產(chǎn)品

2020-12-09 15:31:13 9

9 Xilinx7系列FPGA包括四個(gè)FPGA系列,它們都是為最低功耗而設(shè)計(jì)的,以使一個(gè)通用設(shè)計(jì)能夠跨系列擴(kuò)展以獲得最佳的功率、性能和成本。斯巴達(dá)-7系列是7系列產(chǎn)品中密度最低、成本最低的入門級(jí)產(chǎn)品

2020-12-10 14:20:00 18

18 本文檔的主要內(nèi)容詳細(xì)介紹的是如何使用Xilinx的FPGA對(duì)高速PCB信號(hào)實(shí)現(xiàn)優(yōu)化設(shè)計(jì)。

2021-01-13 17:00:59 25

25 Xilinx_Vivado_zynq7000入門筆記說明。

2021-04-08 11:48:02 70

70 賽靈思近日宣布推出 Vivado ML 版,這是業(yè)內(nèi)首個(gè)基于機(jī)器學(xué)習(xí)(ML )優(yōu)化算法以及先進(jìn)的面向團(tuán)隊(duì)協(xié)作的設(shè)計(jì)流程打造的 FPGA EDA 工具套件,可以顯著節(jié)省設(shè)計(jì)時(shí)間與成本,與目前

2021-07-02 16:40:13 2403

2403

【流水燈樣例】基于 FPGA Vivado 的數(shù)字鐘設(shè)計(jì)前言模擬前言Vivado 設(shè)計(jì)流程指導(dǎo)手冊(cè)——2013.4密碼:5txi模擬

2021-12-04 13:21:08 26

26 Vivado可以導(dǎo)出腳本,保存創(chuàng)建工程的相關(guān)命令和配置,并可以在需要的時(shí)候使用腳本重建Vivado工程。腳本通常只有KB級(jí)別大小,遠(yuǎn)遠(yuǎn)小于工程打包文件的大小,因此便于備份和版本管理。下面把前述腳本升級(jí)到Vivado 2020.2為例,討論如何升級(jí)Vivado工程腳本。

2022-08-02 10:10:17 1542

1542 Xilinx的新一代設(shè)計(jì)套件Vivado相比上一代產(chǎn)品ISE,在運(yùn)行速度、算法優(yōu)化和功能整合等很多方面都有了顯著地改進(jìn)。但是對(duì)初學(xué)者來說,新的約束語言XDC以及腳本語言Tcl的引入則成為了快速掌握Vivado使用技巧的最大障礙,以至于兩年多后的今天,仍有很多用戶缺乏升級(jí)到Vivado的信心。

2022-09-19 16:20:51 1309

1309 LOCK_PINS 是 Xilinx Vivado 做物理約束的屬性之一。用來將LUT的邏輯輸入(I0,,I1,I2...)綁定到其物理輸入pin上(A6,A5,A4...)。

2023-01-11 10:52:24 768

768 系統(tǒng)性的掌握技術(shù)開發(fā)以及相關(guān)要求,對(duì)個(gè)人就業(yè)以及職業(yè)發(fā)展都有著潛在的幫助,希望對(duì)大家有所幫助。本次帶來Vivado系列,Vivado開發(fā)軟件開發(fā)設(shè)計(jì)流程。話不多說,上貨。

2023-02-21 09:16:44 2831

2831 Xilinx LabTools工具是Xilinx FPGA單獨(dú)的編程和調(diào)試工具,是從ISE或Vivado中獨(dú)立出來的實(shí)驗(yàn)室工具,只能用來下載FPGA程序和進(jìn)行ILA調(diào)試,支持所有的FPGA系列,無需

2023-03-28 10:46:56 4755

4755 Xilinx的新一代設(shè)計(jì)套件Vivado相比上一代產(chǎn)品 ISE,在運(yùn)行速度、算法優(yōu)化和功能整合等很多方面都有了顯著地改進(jìn)。但是對(duì)初學(xué)者來說,新的約束語言 XDC 以及腳本語言 Tcl 的引入則成為

2023-04-15 09:43:09 958

958 Xilinx FPGA pcb設(shè)計(jì)

2023-05-29 09:11:36 0

0 電子發(fā)燒友網(wǎng)站提供《為EBAZ4205創(chuàng)建Xilinx Vivado板文件.zip》資料免費(fèi)下載

2023-06-16 11:41:02 1

1 Xilinx公司的FPGA中有著很多的有用且對(duì)整個(gè)工程很有益處的IP核,比如數(shù)學(xué)類的IP核,數(shù)字信號(hào)處理使用的IP核,以及存儲(chǔ)類的IP核,本篇文章主要介紹BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 317

317 已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

硬聲App

硬聲App

13971

13971 10186

10186

1526

1526 403

403

736

736

824

824 11268

11268

65

65 204

204 423

423 197

197 4986

4986 3293

3293

2047

2047 4873

4873 4675

4675

1466

1466 9427

9427 2086

2086 3062

3062 3450

3450

2166

2166

2112

2112 9496

9496 24

24 9

9 18

18 25

25 2403

2403

26

26 1542

1542 1309

1309 768

768 2831

2831 4755

4755 958

958 1

1 317

317

評(píng)論