,2GB的DDR3。 6、標準JTAG接口。 7、支持BPI模式快速加載。 基于賽靈思的V7 的FPGA開發的PCIe DMA IP支持8.0Gbps(Gen3)at x8,x4,x2和x1的硬核,包括

2016-03-11 10:57:58

目 錄OVF402,OVF404,OVF406驅動器故障代碼2OTIS電梯GECB板故障代碼7奧的斯GEN2電梯故障代碼說明10奧的斯TOEC-2000.300VF.3200 清除故障方法

2021-09-06 08:45:31

此參考系統在PCIe Gen2 x4 下實測雙向收發速率 >1600MByte/s。 包含所有FPGA端源文件, PC端驅動和 C++/matlab/python 等參考代碼。 歡迎

2015-12-21 23:50:35

PCIe Gen3 插槽中。此參考設計為用戶提供了有用的指導準則,方便他們將 DS80PCI810 中繼器整合到 PCIe Root Complex ASIC 和他們自己的插卡設計中。特性提供與主板

2022-09-21 07:43:27

你好!我在ZYNQ 7015里(或者7035)調用XDMA PCIE IP 從上位機HOST PC通過PCIE接口給ZYNQ的PS DDR發送數據(XDMA PCIE IP接到了PS的AXI HP

2019-11-21 10:35:01

嗨,我試圖在Zynq 7015中使用GTX來制作一個簡單的傳輸僅使用8B10B編碼的serdes。我有Vivado 2014.4,我在PicoZed SOM上測試。我有一個200Mhz LVDS信號

2020-07-31 09:10:30

ZYNQ7045的PCIE電路設計,板卡使用插針式連接器,引出了PCIE信號,未使用金手指。為了插入機箱設計了擴展版,插座與插針對應,帶有PCIE金手指。目前遇到的問題是,當板卡連接擴展板使用金手指

2023-05-16 11:07:40

目前,我在設計中想使用ZYNQ 7015系列的FPGA,利用JESD204 IP核接收A/D轉換器AD9683轉換完成后的數據。但是JESD204 IP核的端口很多,我不知道應該如何將AD9683

2023-12-15 07:14:52

Xilinx很多開發板上的高速收發器都用到了SEMTEC公司的BullsEye連接器,我想知道這個連接器可以實現GTY收發器的25Gbps線速率嗎?另外這個線纜在哪里可以買到?

2020-10-29 12:43:33

最快的收發器——總共36個收發器,其中24個工作在11.3 Gbps最低的系統功耗——0.95-V低內核電壓同類最佳的信號完整性——具有管芯噪聲濾除以及封裝去耦合功能最快的存儲器接口——1,067

2021-05-19 06:11:28

FMC154-基于FMC 八路SFP+萬兆光纖子卡 一、板卡概述 本卡是一個FPGA夾層卡(FMC)模塊,可提供高達8個SFP / SFP +模塊接口,直接插入千兆位級收發器(MGT)的賽靈思

2021-12-29 17:29:51

高速收發器(SERDES)的運用范圍十分廣泛,包括通訊、計算機、工業和儲存,以及必須在芯片與芯片/模塊之間、或在背板/電纜上傳輸大量數據的系統。但普通高速收發器的并行總線設計已無法滿足現在的要求。將收發器整合在FPGA中,成為解決這一問題的選擇辦法。FPGA高速收發器設計時,我們需要注意哪些事項呢?

2019-08-07 06:26:42

描述OnSpeed Gen2 v2

2022-09-09 07:18:10

本帖最后由 qq2355239039 于 2020-6-6 15:11 編輯

PAN1020是一款集成了射頻收發器和藍牙低功耗基帶處理器的BLE SoC收發器,可以用作應用程序處理器以及完全

2020-06-06 15:08:58

HI,我想知道PHY(Tx和Rx)和Gen2 2通道延遲的延遲。我在哪里可以找到它?謝謝,巧兒

2020-07-21 08:06:11

生態系統中的第一款寬帶收發器,結合了射頻前端和混合信號基帶部分,還集成了頻率合成器,并給處理器提供可配置的數字接口。通過數字接口可以靈活配置各通道的參數,包括頻點、帶寬、增益等參數,基于這些特性

2018-08-16 00:37:12

×2捷變收發器AD9363AD9363 RF收發器是針對各種低功耗無線應用而設計,比如毫微微蜂窩、DAS、無線視頻傳輸。該無線電SoC覆蓋325 MHz至3.8 GHz頻率范圍,具有200 kHz以下

2019-09-17 01:18:57

基礎上對USB 3.1進行補充,保留USB 3.1(Gen2)物理層和編碼技術,利用雙通道技術,在使用經過SuperSpeed+認證的USB type-c數據線后可實現最高20Gbps的傳輸速率,而且

2019-06-24 05:00:54

USB3.1 Gen2的Tx測試相比于Gen1,測試內容和項目有哪些變化?

2015-06-03 15:00:10

USB3.1 Gen2相比于Gen1,Tx測試碼型有什么變化?

2015-06-03 09:03:35

清楚。 USB 3.1(10Gbps)誕生之后,取了個新名字叫USB 3.1 Gen2,而原來的USB 3.0(Gbps)被改名為USB 3.1 Gen1。 USB 3.2(20Gbps)發布之后就徹底亂套

2020-09-03 17:24:39

BC1.2的話,可以通過Flash固件升級完成。Flash固件分為,高功耗固件與低功耗固件兩種。VL822-QFN76:性能上和VL817-QFN76一樣,但傳輸數據是(10Gbps)GEN2速率的一分四

2022-09-13 14:17:05

激活64位系統下vivado2015.4 srio gen2 v4.0,穩定可靠,不開放給學生及個人做學習研究,有意向獲取的單位、公司或者項目產品人員,聯系sell_ip@163.com

2017-09-16 20:52:02

SI53159-EVB,用于PoE無線接入點的100至210MHz時鐘發生器評估板。 Si53159是一款九端口PCIe時鐘緩沖器,符合PCIe Gen1,Gen2和Gen3標準

2020-08-27 12:20:38

管理系統;高密度片上UltraRAM靜態存儲器;單通道速率高達32Gbps的高速收發器;集成100GbE、PCIe Gen4、150Gbps Interlaken等I/O控制器;高性能UltraScale可編程邏輯。和Zynq-7000系列器件相比,加密、安全和電源管理都得到了顯著增強。

2019-10-09 06:07:09

親愛的社區,我開始設計和使用在使用ISE 14.5實現ip-core時提供的GTX收發器示例。我使用帶有FM-S14適配器的Kintex Evalboard KC705(為我提供了4個額外的SFP

2020-07-15 09:10:15

嗨,我正在使用ISE。我想通過連接到IpSRIO gen2 v1.6的微型發送器來發送和接收數據包。我有一個AXI流接口(AXIS_M0& AXIS_S0)我的ublaze和壓縮I / O在

2020-07-13 15:52:29

嘗試使用 ST25RU3993 閱讀器讀取 gen2 標簽時。讀取 EPC 存儲區中的地址 0x02 似乎有效,但用戶區中超過 0x7F 的字地址給我一個錯誤(ERR_RXCOUNT)。我知道我

2022-12-06 06:35:51

我正在嘗試使用Xaui協議的4.25Gbps和使用Zynq zc706板的PCIE。我遵循以下步驟1)生成7系列收發器向導(4.25Gbps,XAUI協議,8b / 10b編碼器和解碼器以及PCIe

2020-05-22 15:27:40

功能豐富的(PL)UltraScale架構在單個設備中。還包括片上存儲器,多端口外部存儲器接口和豐富的外圍連接接口集,尤其是GTH 16.3 Gbps收發器,它具有支持PCIExpress?Gen

2020-09-03 16:07:35

1和gen2,因此它可以在gen1和gen2之間切換。要在gen1和gen2之間切換,我通過TXRATE和RXRATE端口配置了時鐘分頻器值。并通過DRP端口對TDCC值進行編程。切換完成后,我發出

2020-06-19 13:34:36

器件,已經被列在PCI-SIG集成商列表中。UltraScale系列器件通過16Gbps GTH SerDes收發器來支持PCIe Gen3,每個器件中集成了2到6個PCIe模塊)`

2017-02-10 17:19:24

求助!各位大神,我想比較清楚的了解一下基于Type C接口的USB3.1 Gen2 U盤設計原理,如比較清晰的Block Diagram。求大神們支持 !!

2017-08-27 09:43:37

,支持PCI Express Gen2(5Gbps/lane); ?支持64bit DDR3-1600,容量1GByte; ?該FPGA內嵌16個高速串行收發器RocketIO GTX; ?4個

2014-11-24 15:31:02

如何去設計SoC中的低功耗RF收發器?

2021-05-25 07:04:51

協商的速度重置事物。例如,如果設備支持GEN2,如果設備支持GEN2,則在GEN1完成的GEN2 phyob將在GEN 2成功進行協商,如果設備僅支持GEN1,則應在GEN1成功進行速度協商。在

2019-07-24 09:31:51

驗證以下時鐘策略的人是否可以對XC7A15T-2CPG236C有效?我是一名PCB設計師,尚未完全熟悉Xilinx工具套件。我正在提供一個帶有相應ref時鐘輸入的5GHz收發器。在收發器模塊之外

2020-05-11 09:06:46

我的設計需要一個帶有 2 個 CAN 收發器和 2 個 EMAC 接口的 MCU。我發現SPC58系列也一樣。但是網站上沒有完整的零件號。請幫我找出正確的部件號,用于使用 2 個 CAN 收發器和 2 個 EMAC 進行設計。

2023-01-05 08:25:24

B連接器引出千兆網口、PCIe、HyperLink、EMIF16、USB、CAN、UART、GTX等通信接口。??本文主要介紹DSP + ZYNQ基于SRIO的通信案例。案例源碼、產品資料(用戶手冊

2021-03-16 17:53:53

求助FPGA高速串行收發器,輸出12.5Gbps的信號要用什么電平輸出28.5Gbps的信號要用什么電平?

2014-11-10 09:12:51

PCIE x4 Gen2 高速數據傳輸, 包括所有源代碼,驅動和PC端程序

2021-06-23 09:38:33

PCIe Gen3 插槽中。此參考設計為用戶提供了有用的指導準則,方便他們將 DS80PCI810 中繼器整合到 PCIe Root Complex ASIC 和他們自己的插卡設計中。特性提供與主板

2015-05-08 11:31:58

SI52147-EVB,用于PoE無線接入點的時鐘發生器評估板。 Si52147是一款符合PCIe Gen1,Gen2和Gen3標準的9端口PCIe時鐘發生器

2020-08-27 14:27:11

賽靈思 Artix-7 FPGA 是業界唯一的在低端器件上整合了高速收發器的方案,該方案提供了自適應均衡、2D 眼圖以及IBIS-AMI仿真模型來簡化針對成本敏感型應用的高速串行設計,觀看視頻,4分鐘教您搞定高速SerDes端口設計。

2016-07-27 17:29:59

本帖最后由 一只耳朵怪 于 2018-6-19 15:19 編輯

1.我在文檔里看到GEN1 PCIE最高可配置2.5Gbps,GEN2 PCIE最高可配置為5.0Gbps,請問這里說的最高

2018-06-19 04:36:26

嗨,我已經實現了K7-410T的所有16個GTX收發器,實現了一組線速率為2.97Gbps的SMPTE SDI接口。在調試時,我發現RX15的接收質量很差。其BER太高,無法完成下游處理。有人可以給我一些指導來改善GTX收發器的RX功能嗎?我應該調整一些關鍵參數嗎?謝謝。

2020-08-12 06:01:35

HI,我的名字是Dasarath。我使用Spartan 6收發器作為我的SATA主機。該系列為XC6SLX75T FGG484,速度等級為-3。我使用coregen工具生成了Gen1和Gen2

2019-07-18 07:42:19

你好,這是背景。我使用的是Spartan 6,第一個主GTP收發器配置為PCIe端口。我想將另一半的磁貼用于完全獨立的自定義SERDES(盡可能簡單)到另一個Spartan 6.我有一個從GTP設置

2019-08-02 06:59:30

為6.25Gbps,MGTREFCLK1上的125MHz時鐘,我正在查看近端環回結果:請注意,在這兩個測試之間唯一的選項是環回模式,我在兩種情況下都重置了發送器和接收器。從UG482第2章環回部

2019-05-05 14:30:48

內存終端和適用于 CAN 收發器的 5V 電源。LM3880 實現加電和斷電排序。此設計經過針對汽車應用的測試和優化。主要特色為基于 Xilinx? Zynq? 7010 的 ADAS 系統提供所有電源

2018-11-19 15:00:01

:156MHzQSGMII參考serdes1的PLL1,將S1的PLL1寫為0:100MHz SerDes2模塊選擇RCW為5559:(PCIEGen3不可用,Gen2速度為5Gbps)。PCIe.1,PCIe.2

2020-10-28 17:15:14

:156MHzQSGMII參考serdes1的PLL1,將S1的PLL1寫為0:100MHz?SerDes2模塊選擇RCW為5559:(PCIEGen3不可用,Gen2速度為5Gbps)。?PCIe

2020-11-01 20:21:02

;支持PIO和DMA方式;? 多媒體接口:支持1個HDMI顯示輸出接口;最高支持1920x1080分辨率;支持熱插拔;? PCIe主機接口:支持x8 PCIe gen2,線速率達到5Gbps;? SMA

2016-04-18 14:12:57

MAX3785 6.25Gbps, 1.8V PC Board Equalizer

MAX3785 Description

The MAX3785 6.25Gbps equalizer

2008-10-24 09:37:38 766

766

IDT宣布推出PCI Express Gen2 系統互連交換解決方案

IDT® 公司宣布推出PCI Express® (PCIe®)Gen2 系統互連交換解決方案系列。該系列具有業界最先進的交換架構,支持

2010-02-11 09:44:27 750

750 IDT推出Serial RapidIO Gen2系統建模工具

IDT公司(Integrated Device Technology, Inc.)宣布推出新的 Serial RapidIO® Gen2 系統建模工具。現在,無線基礎設施、軍

2010-03-23 12:05:23 1069

1069 收發器的接口類型

收發器典型的接口類型有以太網接口,E1接口、串行接口(RS232)、SC/ST接

2010-01-08 14:15:11 1498

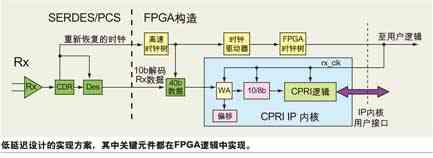

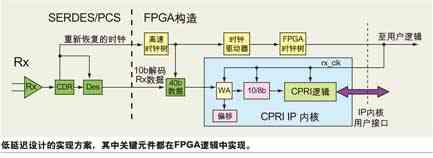

1498 本文討論利用帶嵌入式SERDES收發器和CPRI鏈路IP內核的低成本FPGA,來實現電信

2010-10-09 16:48:05 1166

1166

28nm FPGA實現的28Gbps串行收發器(Serdes)競爭格局今天出現了戲劇性的變化,一直落在后頭的賽靈思公司(Xilinx)突然高調宣布推出具有16個28G

2010-11-19 09:08:11 1035

1035 易飛揚即日宣布40G QSFP GEN2光模塊導入批量生產。與市場流行的40G QSFP通用光模塊的主要差異是:GEN2光模塊帶有多通道光功率的DDM 實時監測功能。

2016-03-11 15:48:06 1343

1343 端口,能夠將 Zynq SoC 的很多可編程 I/O 引腳(包括所有 8 個 12.5 Gbps GTX 收發器端口)連接到 HPC FMC I/O 站點,以實現最大的接口靈活性。

2017-02-08 12:15:34 109

109 使用這些收發器的常用的高速串行接口標準: ?PCIe總線,版本1.1/2.0/3.0 ?SFP+ (SFF-8431)電光信號轉換接口 ?10GBASE-R/KR接口 ?Interlaken串行接口協議

2017-02-09 02:15:10 296

296 還集成了 ?ARM? 雙核處理器和兩個獨立的 ?DDR3L 內存(適用于 ?PL? 和 ?PS )。?具有功能強大的 ?PCIe Gen2 ×8? 接口、千兆位及雙路快速以太網 PHY 、實時時鐘以及大量的 ?I/O ,因此幾乎沒有什么該模塊不能處理的。 了解更多 ??

2017-02-09 08:07:11 236

236 賽靈思Virtex UltraScale架構全可編程器件的很多特色中的一個是它具有20到60個可用的并且可配置的32.75Gbps GTY雙向串行收發器。下面是一些能夠匹配使用這些收發器的常用的高速串行接口標準:

2017-02-11 10:07:50 2793

2793

本文介紹一種使用Zynq SoC和賽靈思IP 核簡化高速光學收發器模塊熱測試的方法。 隨著數據中心內部光學收發器模塊的傳輸速度提高到前所未有的高度,數據中心內每個機架的溫度也在不斷大幅上升。機架中有

2017-11-17 18:11:01 1482

1482 Altera現在是Intel公司旗下的可編程解決方案事業部(PSG),今天發布能夠讓Stratix 10 FPGA和SoC支持高達56 Gbps數據速率的收發器技術。Altera今天演示了FPGA

2018-08-19 09:31:00 1194

1194 Xilinx推出全球首款28nm FPGA,展示10Gbps SERDES功能

Xilinx在Kintex-7 K325T FPGA上展示了10Gbps收發器,這是有史以來第一款28nm FPGA。

2018-11-28 06:30:00 3785

3785 了解設計人員在使用Zynq-7000 All Programmable SoC器件時可用的不同I / O,從標準I / O到串行收發器以及模擬輸入。

2018-11-26 06:36:00 2547

2547 ,支持 16 Gbps 高帶寬,可用于下一代 Intel 和 AMD 平臺。TE 新型 PCIe Gen 4 卡邊緣連接器采用 1.00mm 間距,兼容各代 PCI Express 信號設計,同時支持

2019-11-20 16:12:10 1584

1584 和AFCT-701SDZ 10 Gbs以太網SFP +收發器產品與具有自適應DFE的XilinxVirtex?-6FPGA 11.18 Gbps收發器的高速互操作性。 Xilinx產品:Virtex-6 HXT

2021-04-14 11:53:31 4122

4122

DRIVE SSD 1TB 內置了一個 PCIe Gen3 x4 固態硬盤,可提供 2000 MB/s 的讀 / 寫速度。這款移動的 SSD 的接口為 USB 3.2 Gen2 x2 ,理論帶寬

2020-12-18 14:09:07 2953

2953 奧德斯Gen2 Core電梯調試手冊下載

2021-04-02 09:47:35 0

0 設計的帶嵌入式收發器的Gen1×1硬核IP的 PCI Express IP編譯器(基于嵌入式開發游戲項目)-在Cyclone IV GX收發器入門套件上,設計帶嵌入式收發器的Gen1×1硬核IP的 PCI Express IP編譯器。.rar

2021-07-30 16:48:41 9

9 USB-C 3.1 Gen2 10Gbps 速率的HUB芯片,創惟的GL3590可以做到2C2A 1C4A 等等。希望你如果用到這方面的資料,我能提供給你一點幫助。

2022-05-05 14:49:09 37

37 VL822是USB 3.1 Gen2集線器控制器,它具有高度集成的、特定應用的設計。VL822具有1個上行端口和4個/2個下行端口,所有端口均支持10Gbps USB 3.1 Gen2操作。下行端口

2022-06-23 14:44:50 2900

2900

在PCIe模式中,PCLK是FPGA邏輯接口,用來同步并行接口數據傳輸。在Gen1應用中推薦的PCLK時鐘為125MHz,在Gen2和Gen3中推薦的PCLK為250MHz。通常一個MMCME2_ADV通過參考輸入時鐘產生125MHz和250MHz時鐘。

2022-07-05 10:08:17 2311

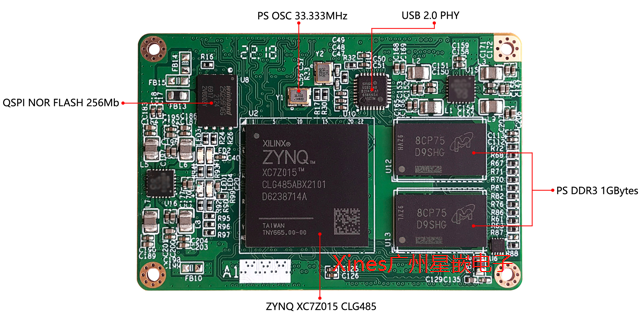

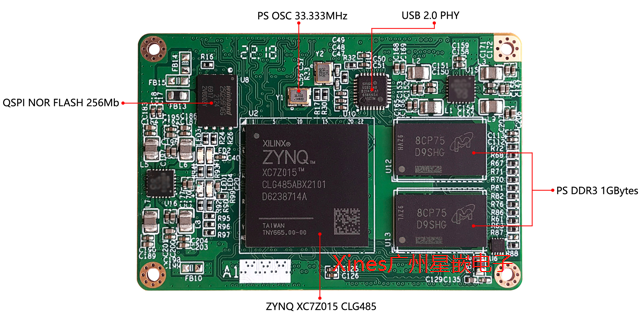

2311 Cortex-A9 + PL端Artix-7架構28nm可編程邏輯資源、最大頻率766MHz,支持6.25G的高速SerDes,可支持PCIe、SATA、SFP等。

2022-08-17 15:41:47 2594

2594

當地時間11月15-17日,美國夏威夷,高通將舉辦一年一度的驍龍技術峰會。按照慣例,驍龍8 Gen2將會正式登場。 這幾年,驍龍旗艦平臺的升級力度有些疲軟,加之功耗發熱問題,被很多網友斥為“擠牙膏

2022-10-10 18:23:40 5619

5619 USB接口將統一以傳輸帶寬命名,USB4 v2.0對應USB 80Gbps,USB4對應USB 40Gbps,USB 3.2 Gen2x2對應20Gbps,USB 3.2 Gen2對應USB 10Gbps,USB 3.2 Gen1對應USB 5Gbps……

2022-10-20 11:54:15 1172

1172 架構28nm可編程邏輯資源,最大頻率866MHz、Logic Cells 74K、DSP Slices 160、PCI Express? Gen2 x4、支持6.25G的高速SerDes。?

2023-01-04 17:40:13 1

1 同時介紹一種采用光電集成技術的,即采用光SerDes而非電SerDes的高速收發器。

2023-04-01 09:28:58 1078

1078 89EBP0604SB SATA 6.25Gbps Eval Board 手冊

2023-04-17 19:29:41 0

0 89EBP0602Q SATA 6.25Gbps 評估板 手冊

2023-04-17 20:07:25 0

0

電子發燒友App

電子發燒友App

評論