表。 這4類路徑中,我們最為關心是②的同步時序路徑,也就是FPGA內部的時序邏輯。 時序模型 典型的時序模型如下圖所示,一個完整的時序路徑包括源時鐘路徑、數據路徑和目的時鐘路徑,也可以表示為觸發器+組合邏輯+觸發器的模型。 該

2020-11-17 16:41:52 2768

2768

在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束和時序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是一個重點。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 1382

1382 FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間。

2023-06-06 17:53:07 860

860

在FPGA設計中,時序約束對于電路性能和可靠性非常重要。在上一篇的文章中,已經詳細介紹了FPGA時序約束的主時鐘約束。

2023-06-12 17:29:21 1230

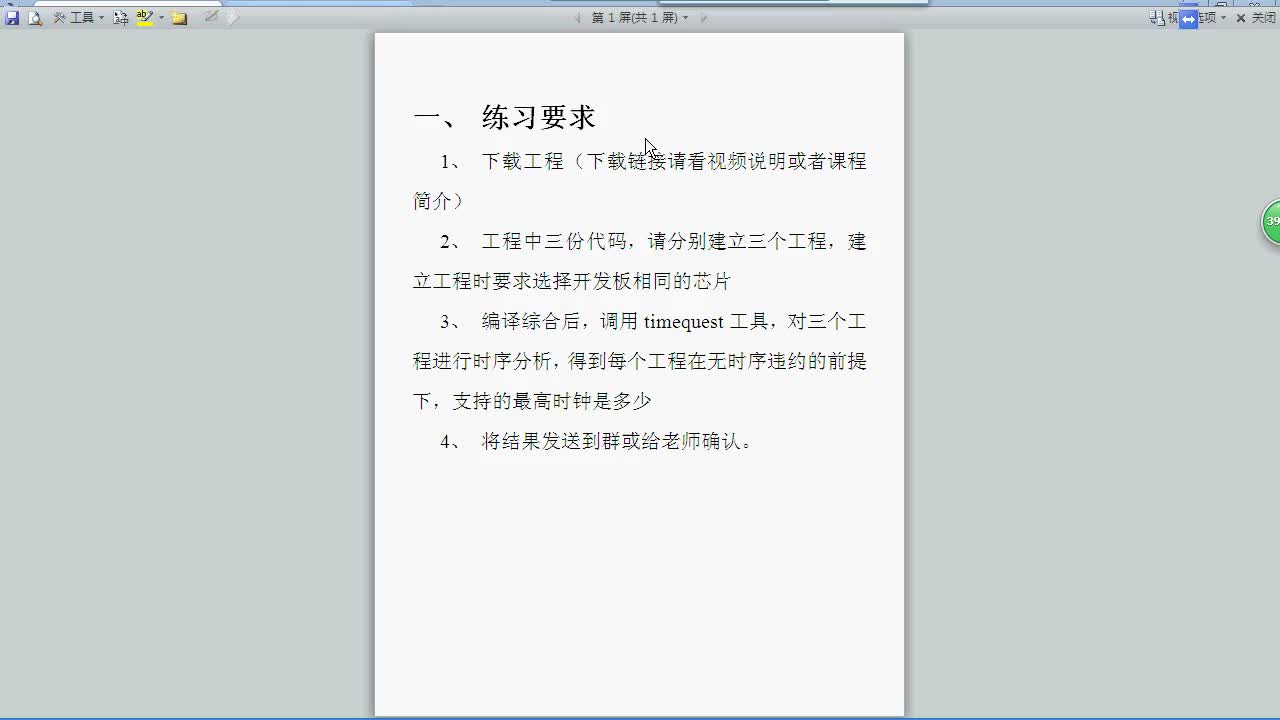

1230 前面講解了時序約束的理論知識FPGA時序約束理論篇,本章講解時序約束實際使用。

2023-08-14 18:22:14 842

842

FPGA系統設計實質上是一個同步時序系統的設計,理解時序概念,掌握代碼優化與綜合技術,正確完整地進行時序約束和分析是實現高性能系統的重要保證。很多同學在設計中都會碰到時序方面的問題,如何解決時序難題

2018-06-07 15:52:07

包括兩個方面:

a)時鐘的時序分析

這里面一般也包括三個方面:

i.輸入時鐘的約束

ii.通過PLL向FPGA內部輸出的時鐘

iii.通過PLL向FPGA外部輸出的時鐘(一般稱為

2011-09-23 10:26:01

FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間

2023-11-15 17:41:10

+時序例外約束+I/O約束+Post-fit Netlist 引入Post-fit Netlist的過程是從一次成功的時序收斂結果開始,把特定的一組邏輯(Design Partition)在FPGA上

2016-06-02 15:54:04

的過程是從一次成功的時序收斂結果開始,把特定的一組邏輯(Design Partition)在FPGA上實現的布局位置和布線結果(Netlist)固定下來,保證這一布局布線結果可以在新的編譯中重現,相應

2017-12-27 09:15:17

FPGA時序相關的資料。都看完看懂時序就沒問題了。分了三個附件:第一個是通過一些例子教你如何搞定時序分析。第二個附件是網上各種大神們對時序的理解,主要是他們的博客鏈接以及網站鏈接。第三個是其他的一些零散的關于時序的資料。

2012-11-12 17:45:28

FPGA時鐘時序資料

2014-06-03 20:13:27

Hold Time、Clock-to-Output Delay 等眾多時序特征量密切相關。面積和速度這兩個指標貫穿 FPGA/CPLD 設計的時鐘,是設計質量的評價的終極標準 —— 面積和速度是一對對

2020-09-25 11:45:18

FPGA的時序優化高級研修班通知通過設立四大專題,幫助工程師更加深入理解FPGA時序,并掌握時序約束和優化的方法。1.FPGA靜態時序分析2.FPGA異步電路處理方法3.FPGA時序約束方法4.FPGA時序優化方法

2013-03-27 15:20:27

在進行FPGA的設計時,經常會需要在綜合、實現的階段添加約束,以便能夠控制綜合、實現過程,使設計滿足我們需要的運行速度、引腳位置等要求。通常的做法是設計編寫約束文件并導入到綜合實現工具,在進行

2023-09-21 07:45:57

`為保證設計的成功,設計人員必須確保設計能在特定時限內完成指定任務。要實現這個目的,我們可將時序約束應用于連線中——從某 FPGA 元件到 FPGA 內部或 FPGA 所在 PCB 上后續元件輸入

2012-03-01 15:08:40

隨著FPGA器件體積和復雜性的不斷增加,設計工程師越來越需要有效的驗證方。時序仿真可以是一種能發現最多問題的驗證方法,但對許多設計來說,它常常是最困難和費時的方法之一。過去,采用標準臺式計算機的時序

2019-07-16 08:10:25

FPGA設計驗證關鍵要點不同于ASIC設計,FPGA設計中的標準元件或客制化實作,一般欠缺大量的資源及準備措施可用于設計驗證。由于可以重新程式化元件,更多時候驗證只是事后的想法。本文將探討在FPGA

2010-05-21 20:32:24

在學習fpga的過程中的疑問:1、在功能仿真和板級驗真后沒問題,還需要進行時序分析嗎2、怎么知道自己寫的代碼有時序問題?

2017-01-08 17:50:35

三菱伺服電機故障修理的要點有哪些?是什么原因造成三菱伺服電機故障的?

2021-09-26 06:06:22

先前 Microsoft 只提出 Azure Sphere 的三大要素,包含 MCU 芯片、MCU 內的操作系統,以及其對應搭配的 Azure 物聯網云端服務。不過,有時卻會看到有些 MCU 芯片上

2021-11-11 07:51:52

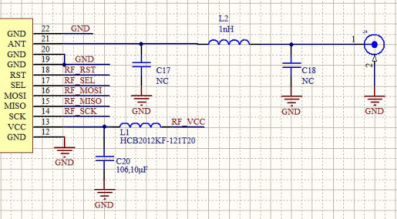

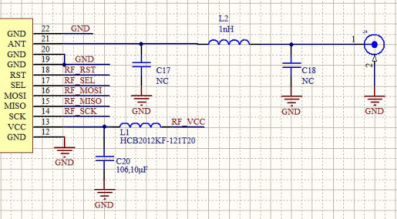

參考LoRa天線電路設計四大要點SX1278芯片LoRa通信官方驅動源碼詳細講解LoRa芯片SX1278官方驅動移植SX1268驅動程序設計LORAWAN在嵌入式系統中的實現–節點端(三

2021-12-07 06:23:44

《FPGA設計時序收斂》,很好的PPT!推薦給大家[hide][/hide]

2011-07-26 11:24:49

當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現工具來優化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。設計者現在有一些

2019-08-11 08:30:00

什么是時序分析?時序約束的作用是什么?FPGA組成的三要素分別是哪些?

2021-09-18 06:05:51

各位好,初次使用pt對fpga進行靜態時序分析,想請教下需要哪些文件。是不是需要:1、在ise或qutartus生成的網表2、SDC文件3、.db文件.db文件必須且只能從dc生成嗎,要是從.lib轉化而來,這個lib文件在fpga設計時又從哪里得到問題貌似比較多,謝謝回答

2014-12-18 16:15:12

利用高速FPGA設計PCB的要點及相關指導原則有哪些?

2021-04-25 08:17:55

嗨,我們正在嘗試使用Vivado工具鏈手動路由FPGA,并想知道應該使用什么工具來手動路由Virtex 7 FPGA。還可以在Vivado時序分析器工具中指定溫度和電壓值來估算設計時序嗎?我們將如

2018-10-25 15:20:50

FPGA的最小單元往往是由LUT(等效為組合邏輯)和觸發器構成。 在進行FPGA設計時,應該采用組合邏輯設計還是時序邏輯?這個問題是很多初學者不可避免的一個問題。 設計兩個無符號的8bit數據相加的電路

2023-03-06 16:31:59

當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現工具來優化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。設計者現在有一些

2021-05-18 15:55:00

基于FPGA的音樂倒數計時器,設計FPGA的時序,當倒計時為0時,通過輸入電平的不同頻率和高低電平的占空比控制蜂鳴器,播放音樂。

2017-05-05 15:23:38

時序分析是FPGA設計的必備技能之一,特別是對于高速邏輯設計更需要時序分析,經過基礎的FPGA是基于時序的邏輯器件,每一個時鐘周期對于FPGA內部的寄存器都有特殊的意義,不同的時鐘周期執行不同的操作

2017-02-26 09:42:48

如何使用基于圖形的物理綜合加快FPGA設計時序收斂?

2021-05-06 09:19:08

大家好,我想知道如何實現硬件(FPGA)中的時序報告給出的時序。我的意思是,如何測量FPGA和FPGA中輸入信號的建立或保持時間與靜態時間報告給出的值進行比較。FPGA怪胎以上來自于谷歌翻譯以下

2019-01-15 11:07:15

如何有效的管理FPGA設計中的時序問題當FPGA設計面臨到高級接口的設計問題時,EMA的TimingDesigner可以簡化這些設計問題,并提供對幾乎所有接口的預先精確控制。從簡單SRAM接口到高速

2009-04-14 17:03:52

大要點? 嵌入式開發工程師需要掌握的7大要點: 1、至少要對印刷電路板中電源的走線有基本理解,了解糟糕的布局布線會對電源質量造成什么樣的后果,即使你從來沒親手設計過一塊電路板的布線,也要能夠對混亂

2017-06-28 14:05:27

為什么需要safe mode?嵌入式系統設計時需要注意的技術要點和實現細節有哪些?

2021-04-25 08:49:22

工作,原因是該電源的PCB布線存在著許多問題。那么有什么好的辦法可以解決嗎?本文為大家總結了開關電源PCB快速布線的八大要點。開關電源產生的電磁干擾,時常會影響到電子產品的正常工作,正確的開關電源PCB

2016-07-15 11:41:38

本文主要探討了DDR型存儲器接口設計中必要的時鐘偏移及數據采集的時序空余。

2021-04-30 06:46:13

等離子電視選購三大要點 有關部門發布表明等離子電視對人眼睛的健康更有利。于是很多人希望更具體地了解應該如何選擇等離子電視。 國家廣播電視產品質量監督檢驗中心高級工程師安永成

2009-12-22 09:44:25

總結時序收斂的目的是讓FPGA design 按預設的邏輯正常的工作。為了使其正常工作,需要考慮至少三處:FPGA內部的寄存器-寄存器時序要求,FPGA輸入數據的時序要求,FPGA輸出信號的要求。

2019-07-09 09:14:48

集成功放應用要點是什么?

2021-06-02 06:25:58

如何有效的管理FPGA設計中的時序問題

當FPGA設計面臨到高級接口的設計問題時,EMA的TimingDesigner可以簡化這些設計問題,并提供對幾乎所有接口的預先精確控制。從簡單

2009-04-15 14:19:31 659

659

音頻功放失真的四大要點及改善方法

失真是輸入信號與輸出信號在幅度比例關系、相位關系及波形形狀產生變化的現象。音頻功

2010-01-14 16:10:57 5054

5054 買電腦與JS(奸商)較量之六大要點

一般用戶在購機與JS面對面打交道的時候,一定要牢記一條真理:JS的目的就是賺錢,不會平

2010-01-19 17:21:28 448

448 延長筆記本電腦光驅壽命十大要點

筆記本電腦的光驅是一個非常嬌貴的部件,

2010-01-21 09:02:14 594

594 VPN選購幾大要點

隨著網絡,尤其是網絡經濟的發展,企業規模日益擴大,客戶分布日益廣泛,合作伙伴日益增多,傳統企業網基于固

2010-04-01 11:11:26 917

917 汽車電池保養需要牢記的七大要點注意事項

前 言

2010-04-19 13:41:29 396

396 介紹了采用STA (靜態時序分析)對FPGA (現場可編程門陣列)設計進行時序驗證的基本原理,并介紹了幾種與STA相關聯的時序約束。針對時序不滿足的情況,提出了幾種常用的促進 時序收斂的方

2011-05-27 08:58:50 70

70 當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現工具來優化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。

2014-08-15 14:22:10 1169

1169 FPGA時序約束方法很好地資料,兩大主流的時序約束都講了!

2015-12-14 14:21:25 19

19 賽靈思FPGA設計時序約束指南,下來看看

2016-05-11 11:30:19 48

48 電路教程相關知識的資料,關于硬件工程師電路設計十大要點

2016-10-10 14:34:31 0

0 基于時序路徑的FPGA時序分析技術研究_周珊

2017-01-03 17:41:58 2

2 如何有效地管理FPGA設計中的時序問題

2017-01-14 12:49:02 14

14 當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現工具來優化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。設計者現在有一些

2017-02-09 01:59:11 264

264 fpga時序收斂

2017-03-01 13:13:34 23

23 隨著LoRa技術在業內的持續發熱,加上其獨特優越的傳輸性能,運用LoRa技術的群體正在爆發式的增長,由于很大部分群體對LoRa等射頻技術均是初次接觸,在做產品的過程中,通常會遇到棘手的射頻電路設計問題,其實只要掌握幾大要點,就基本可以發揮LoRa的最佳性能。

2017-03-23 10:44:38 18695

18695

現場可編程門陣列(FPGA)被發現在眾多的原型和低到中等批量產品的心臟。 FPGA的主要優點是在開發過程中的靈活性,簡單的升級路徑,更快地將產品推向市場,并且成本相對較低。一個主要缺點是復雜

2017-11-15 16:33:28 539

539

一個好的FPGA設計一定是包含兩個層面:良好的代碼風格和合理的約束。時序約束作為FPGA設計中不可或缺的一部分,已發揮著越來越重要的作用。毋庸置疑,時序約束的最終目的是實現時序收斂。時序收斂作為

2017-11-17 07:54:36 2326

2326

現有的工具和技術可幫助您有效地實現時序性能目標。當您的FPGA 設計無法滿足時序性能目標時,其原因可能并不明顯。解決方案不僅取決于FPGA 實現工具為滿足時序要求而優化設計的能力,還取決于設計人員指定前方目標,診斷并隔離下游時序問題的能力。

2017-11-18 04:32:34 2951

2951 FPGA 設計的最優結果。 何為時序約束? 為保證設計的成功,設計人員必須確保設計能在特定時限內完成指定任務。

2017-11-24 19:37:55 4903

4903

的數量,可以用消耗的觸發器和查找表的個數或者是等效邏輯門數來衡量;速度是指一個設計在FPGA上穩定運行時所能 達到的最高頻率,由設計時序狀態決定。 關于面積和速度的折衷,應在滿足設計時序和工作頻率要求的前提下,占用最小的芯片面積;或者在所規定

2017-11-25 03:57:01 802

802

FPGA時序收斂讓你的產品達到最佳性能!

2018-04-10 11:38:48 18

18 FPGA設計一個很重要的設計是時序設計,而時序設計的實質就是滿足每一個觸發器的建立(Setup)/保持(Hold)時間的要求。

2018-06-05 01:43:00 4150

4150

同步時序電路的延遲最常用的設計方法是用分頻或者倍頻的時鐘或者同步計數器完成所需的延遲。

2018-07-13 17:59:30 4176

4176 FPGA的用處比我們平時想象的用處更廣泛,原因在于其中集成的模塊種類更多,而不僅僅是原來的簡單邏輯單元(LE)。

2018-09-23 10:17:00 2600

2600 FPGA設計中,層次結構設計和復位策略影響著FPGA的時序。在高速設計時,合理的層次結構設計與正確的復位策略可以優化時序,提高運行頻率。

2019-02-15 15:15:53 849

849 本文檔的主要內容詳細介紹的是FPGA視頻教程之FPGA設計中時序邏輯設計要點的詳細資料說明免費下載。

2019-03-27 10:56:04 20

20 Agilex是Agile(敏捷)和Flexible(靈活)兩個詞語的結合體,而這兩個特點也正是現代FPGA技術最為核心的兩大要點。

2019-07-11 15:02:54 390

390 Agilex是Agile(敏捷)和Flexible(靈活)兩個詞語的結合體,而這兩個特點也正是現代FPGA技術最為核心的兩大要點。

2019-10-12 17:41:50 463

463 Agilex是Agile(敏捷)和Flexible(靈活)兩個詞語的結合體,而這兩個特點也正是現代FPGA技術最為核心的兩大要點。

2019-11-18 15:25:27 1183

1183 時序分析結果,并根據設計者的修復使設計完全滿足時序約束的要求。本章包括以下幾個部分: 1.1 靜態時序分析簡介 1.2 FPGA 設計流程 1.3 TimeQuest 的使用 1.4 常用時序約束 1.5 時序分析的基本概念

2020-11-11 08:00:00 58

58 在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束利序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是重點。只有約東正確才能在高速情況下保證FPGA和外部器件通信正確

2021-01-13 17:13:00 11

11 電動汽車電池的六大要點問題分析。

2021-06-03 16:32:42 10

10 電磁閥選擇要注意四大要點“適用性、可靠性、安全性、經濟性”

2021-06-13 17:30:00 2699

2699 本文章探討一下FPGA的時序約束步驟,本文章內容,來源于配置的明德揚時序約束專題課視頻。

2022-03-16 09:17:19 3255

3255

上一篇《FPGA時序約束分享01_約束四大步驟》一文中,介紹了時序約束的四大步驟。

2022-03-18 10:29:28 1323

1323

時序分析時FPGA設計中永恒的話題,也是FPGA開發人員設計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2022-03-18 11:07:13 2096

2096 本文章探討一下FPGA的時序input delay約束,本文章內容,來源于配置的明德揚時序約束專題課視頻。

2022-05-11 10:07:56 3462

3462

明德揚有完整的時序約束課程與理論,接下來我們會一章一章以圖文結合的形式與大家分享時序約束的知識。要掌握FPGA時序約束,了解D觸發器以及FPGA運行原理是必備的前提。今天第一章,我們就從D觸發器開始講起。

2022-07-11 11:33:10 2922

2922

本文章探討一下FPGA的時序input delay約束,本文章內容,來源于明德揚時序約束專題課視頻。

2022-07-25 15:37:07 2379

2379

電子發燒友網站提供《Gowin設計時序約束用戶指南.pdf》資料免費下載

2022-09-15 16:04:17 2

2 電子發燒友網站提供《使用FPGA的數字時鐘(計時表).zip》資料免費下載

2022-11-23 10:38:36 5

5 在進行FPGA的設計時,經常會需要在綜合、實現的階段添加約束,以便能夠控制綜合、實現過程,使設計滿足我們需要的運行速度、引腳位置等要求。通常的做法是設計編寫約束文件并導入到綜合實現工具,在進行

2023-04-27 10:08:22 768

768 早期的FPGA相對比較簡單,所有的功能單元僅僅由管腳、內部buffer、LE、RAM構建而成,LE由LUT(查找表)和D觸發器構成,RAM也往往容量非常小。

2023-05-09 11:22:58 175

175 STA(Static Timing Analysis,即靜態時序分析)在實際FPGA設計過程中的重要性是不言而喻的

2023-06-26 09:01:53 362

362

FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間。

2023-06-26 14:42:10 344

344

FPGA時序不收斂,會出現很多隨機性問題,上板測試大概率各種跑飛,而且不好調試定位原因,所以在上板測試前,先優化時序,再上板。

2023-06-26 15:41:31 1112

1112

FPGA高級時序綜合教程

2023-08-07 16:07:55 3

3 對于電子設備,在運行過程中會產生一定量的熱量,這些熱量會迅速提高設備的內部溫度。如果不及時釋放熱量,設備將繼續加熱,設備會因過熱而發生故障,并且電子設備的可靠性能會下降。因此,在PCB設計時進行良好的散熱處理非常重要。接下來我給大家介紹一下PCB散熱設計四大要點,PCB設計工程師必備技能。

2023-10-15 12:01:11 456

456 電子發燒友網站提供《LED驅動電源設計五大要點.doc》資料免費下載

2023-11-15 09:53:39 0

0

電子發燒友App

電子發燒友App

評論