電阻,因為物質對電流產生的阻礙作用,所以稱其該作用下的電阻物質。電阻將會導致電子流通量的變化,電阻越小,電子流通量越大,反之亦然。沒有電阻或電阻很小的物質稱其為電

2012-03-12 16:46:08 11967

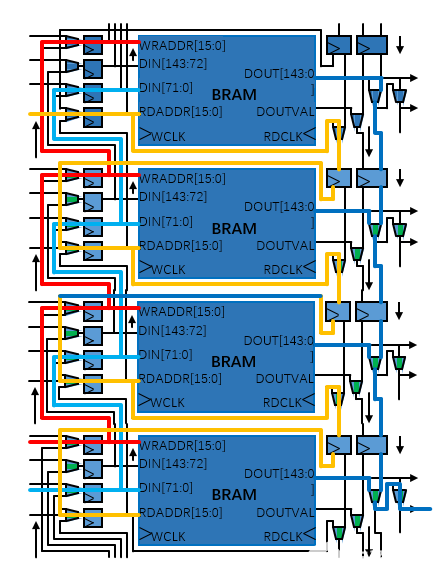

11967 利用FPGA實現雙口RAM的設計及應用

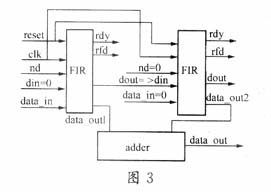

概述:為了在高速采集時不丟失數據,在數據采集系統和

2010-04-16 14:08:36 11323

11323

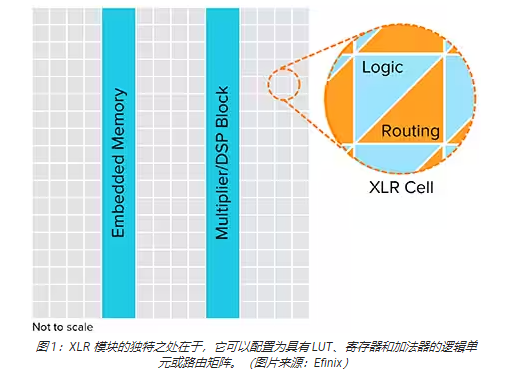

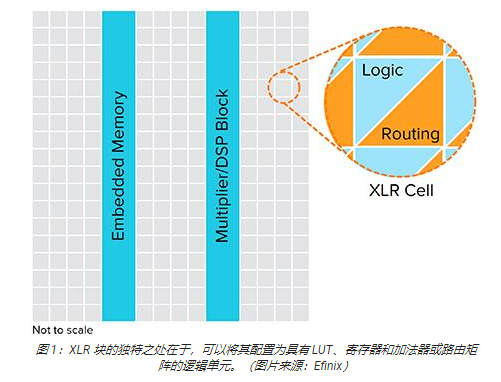

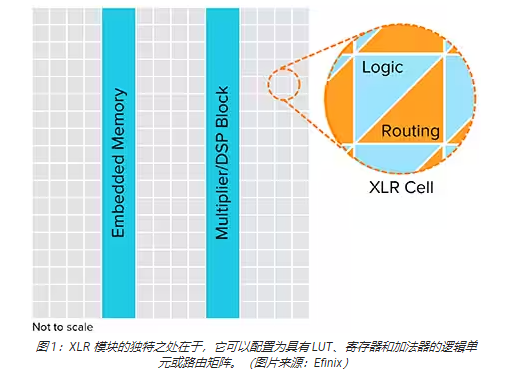

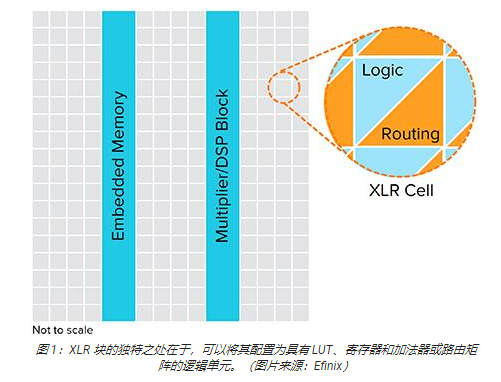

編者按:FPGA 架構的新方法帶來了更細粒度的控制和更大的靈活性,以滿足機器學習 (ML) 和人工智能 (AI) 的需求。這個由兩部分組成的系列的第 1 部分介紹了 Efinix 的一個這樣的架構

2023-04-24 14:49:11 8577

8577

作者:Adam Taylor 編者按:全新的 FPGA 架構方法帶來了更精細的控制和更大的靈活性,以滿足機器學習 (ML) 和人工智能 (AI) 的需求。本系列文章包括兩部分,第 1部分介紹

2023-10-03 14:45:00 318

318

作者:Adam Taylor 編者按:全新的 FPGA 架構方法帶來了更精細的控制和更大的靈活性,以滿足機器學習 (ML) 和人工智能 (AI) 的需求。本系列文章包括兩部分,第 1部分介紹

2023-10-03 14:45:00 430

430

Xilinx Block Memory Generator(BMG)是一個先進的內存構造器,它使用Xilinx fpga中的嵌入式塊RAM資源生成面積和 性能優化的內存。

2023-11-14 17:49:43 736

736

在選擇FPGA時,關注LUT(Look-Up Table)和BRAM(Block RAM)是非常重要的,因為它們是FPGA架構中的兩個核心資源,對于設計的性能和資源利用至關重要。

2023-11-21 15:03:06 548

548

【導讀】為了滿足人工智能、機器學習、無人駕駛、ADAS等應用提出的越來越高的特殊計算需求,Achronix宣布為其eFPGA IP解決方案推出Speedcore定制單元塊,這是一種可以將功耗和面積降至最低、同時將數據流通量最大化的解決方案。

2017-10-19 11:28:32 988

988 大打折扣,那么如何突破呢? ? 與指令集架構不同,數據流架構的顯著特點就是依托數據流的流動次序控制計算執行次序,而非指令執行次序,因此把它用在AI上可以讓芯片利用率大幅提升,芯片利用率直至逼近?100%。 ? 數據流架構如何提升芯片利

2021-11-26 07:27:00 3965

3965 大家好。我設計并模擬了簡單的RTL with Block RAMin Kintex 7。在合成和實現之后,vivado用于功率估計。當我使用分布式RAM時,會正確報告每個RAM的功耗。但是

2019-03-13 14:21:13

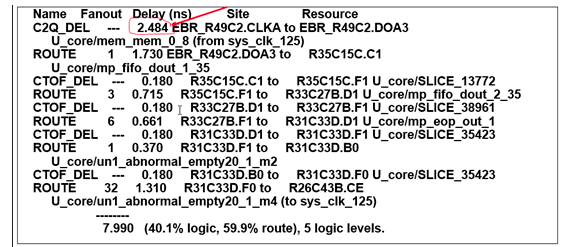

互連線資源(Interconnect)4.嵌入式塊 RAM(BRAM)(Block RAM)5.底層內嵌功能單元6.內嵌專用硬核7.致謝FPGA 芯片整體架構FPGA 芯片整體架構如下所示,大體按照...

2021-07-30 08:10:06

各位大神,我最近在做FPGA項目遇到一個問題,我想實現這樣的功能:向RAM里寫一次數據,再多次讀出來,可是我發現IP核里的RAM讀第二次的時候RAM數據就清零了,根本讀不我寫的數據,請問有什么好的解決辦法嗎?謝謝啦!

2015-06-07 20:31:57

這個接口。核心板電路架構框圖如圖3.10所示。(特權同學,版權所有)圖3.10 核心板電路架構框圖另外,有兩顆存儲器,SPIFLASH用于FPGA器件的上電配置數據存儲,我們都知道FPGA是基于RAM

2015-04-20 11:25:47

操作的處理流程為:輸入數據流通過“輸入數據選擇單元”將數據流等時分配到兩個數據緩沖區,數據緩沖模塊可以為任何存儲模塊,比較常用的存儲單元為雙口RAM(DPRAM)、單口RAM(SPRAM)、FIFO等

2010-11-01 13:17:36

橋接器和一些簡單的UART VHDL代碼通過HyperTerm從FPGA到PC獲取數據?我在ML605上看到,Xilinx表示需要實現UART IP,例如XPS UART Lite或UART16550

2019-09-09 06:23:26

的6個原型中運行良好。當我連接到FPGA上的參考電壓IO時,其中2個變為不同的電阻值,因此RAM數據流不起作用。我手動手動測試參考電壓引腳以排除出售的問題。在我的工作板上,我在參考電壓電阻12k上測量

2019-06-20 15:21:24

。無需CPU直接控制,通過硬件為RAM和IO設備開辟一條直接數據傳輸通道,將數據直接從一個地址空間復制到另一個地址空間,傳輸動作本身由DMA控制器實現。作用:為CPU減負,提升CPU效率STM32F4/F7: 2個DMA控制器,16個數據流。每個DMA控制器都用于管理一個或者多個外設

2021-11-03 06:32:58

我今天正在實現FIFO,我想知道FIFOPrimitive和Block RAM實現之間的區別是什么。根據我的理解,它們使用相同的底層RAM原語,但FIFOPrimitive不能有不同的R / W方面

2019-02-27 14:16:45

實現超高效率的傳質及傳熱,安全穩定地實現研發及小試的化工工藝過程。 技術參數:尺寸:70×70×20mm接頭尺寸:MUNF 1/4”-28螺絲尺寸:M3溫度:-25-230℃壓力:0-100bar建議流通量:50-500mL/min用途:用于工業化小試及中試生產中的兩相混合,可配合減壓閥一起使用。

2018-06-29 10:45:50

NanoEdge? AI Studio(NanoEdgeAIStudio)是一種新的機器學習(ML)技術,可輕松為最終用戶帶來真正的創新。只需幾個步驟,開發人員就可以基于最少量的數據為其項目創建最佳的 ML 庫。

2022-11-29 07:37:53

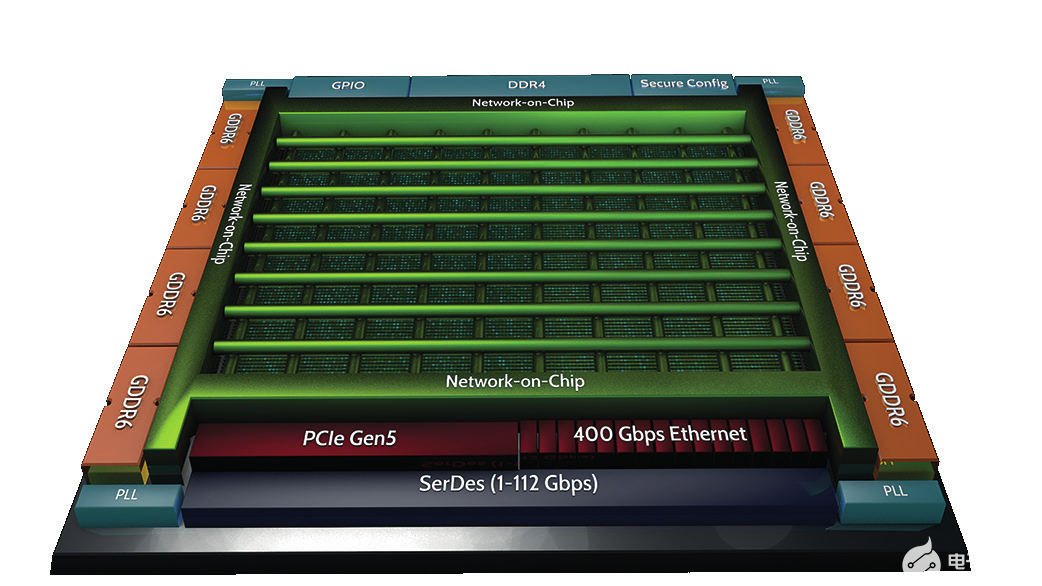

NoC在高端FPGA的應用是什么?NoC給Speedster 7t FPGA帶來的優勢有哪些?

2021-06-17 11:12:26

嗨,為了調試系統,我需要在系統運行時動態讀取Block-RAM內容....我只有JTAG線,我不能在FPGA中制作一個特定的塊用于讀取內容并通過JTAG等發送它們。我可以使用ISMP 13.2作為

2019-06-11 07:36:08

為“YES”時,我在位源摘要中得到以下信息:信息:Bitgen:341- 此設計使用一個或多個9K Block RAM(RAMB8BWER)。用戶定義和默認的9K Block RAM初始化數據需要特殊

2018-10-26 15:06:01

我想知道 X-CUBE-AI 和 NanoEdge AI Studio 在 ML 和 AI 開發環境中的區別。我可以在任何一個開發環境中做同樣的事情嗎?使用的設備有什么限制嗎?

2022-12-05 06:03:15

RAMB16_S18_S18。我使用一個端口進行讀取和寫入(使用寫入啟用),第二個端口僅用于讀取(通過將WEB設置為0)。兩個端口共享相同的時鐘。 Block RAM設置為18位寬,但我忽略了奇偶校驗數據(即,不使用其輸出值

2019-04-24 07:35:02

首先感謝電子發燒友論壇提供的書籍和閱讀評測的機會。

拿到書,先看一下封面介紹。這本書的中文名是《AI加速器架構設計與實現》,英文名是Accelerator Based on CNN Design

2023-09-17 16:39:45

CC3200AI實驗教程——瘋殼·開發板系列AI語音系統架構AI語音識別系統的系統架構如圖1.0.1所示。圖1.0.1 AI語音系統結構 用戶通過語音采集板卡采集到在駐極體端的語音,通過I2S接口

2022-08-30 14:54:38

CC3200AI實驗教程——瘋殼·開發板系列AI人臉系統架構AI人臉識別系統由7大塊組成,分別是攝像頭、CC3200、串口調試助手、路由器、公網、服務器、數據庫以及百度AI組成。AI人臉識別系統

2022-08-31 16:35:59

本文和設計代碼由FPGA愛好者小梅哥編寫,未經作者許可,本文僅允許網絡論壇復制轉載,且轉載時請標明原作者。OV5640提供了一個DVP接口用來輸出采集到的圖像數據流,本文提供了一個將DVP接口的圖像

2020-02-18 19:56:10

充分利用了微軟遍布全球數據中心的FPGA基礎架構,使用FPGA解決了AI應用中“低延時”和“高帶寬”兩大痛點,并成功構建了基于軟核NPU和自定義指令集的實時AI系統。腦波項目的成功實踐,再一次為業界

2019-08-11 04:00:00

設計)。如果不考慮維護性和可測性,調試成本和壓力就非常之大。通常,FPGA的大部分架構設計可以采用數據流驅動的方式來實現,例子1,假設一個實現視頻解壓縮FPGA的設計,輸入是無線接口,輸出為顯示屏。那么輸入輸出

2019-08-02 08:30:00

我正在運行Spartan 6 block ram的模擬。時鐘速度為100Mhz。塊ram的寫作運作良好。我可以在內存中看到數據。但是當我讀取數據時,輸出有2個時鐘的延遲。在塊ram用戶guidt中

2019-07-25 08:15:27

上面的基本邏輯單元還不夠,多個基本邏輯怎么級聯?級聯的連接部分怎么可編程?下圖是FPGA內邏輯塊之間互聯的結構圖。邏輯塊的輸入輸出通過連接塊Connection Block CB和交換塊結合級聯到其他

2018-08-21 09:50:44

的CDMA加載權重,輸入到PL區的Block Ram。原理框圖首先,我們創建了整個系統的示意圖。有兩個 Block RAW 分別用于存儲輸入特征和權重數據。每個Block RAM 都連接到一個 CDMA

2023-02-21 15:01:58

您好!分布式RAM和Block RAM之間究竟有什么區別?兩者都只是芯片內存,對吧?但我不知道兩者之間的區別。和..下一個問題.. isaboutMUX ..根據7系列概述,7系列FPGA支持全范圍

2020-07-19 06:37:51

在我的一個FPGA類中,我被要求使用coregen創建一個blcok ram(8dx16w),單端口ram IP。我在Windows XP,Service Pack 3上使用Xilinx ISE

2019-06-05 13:39:14

系統結構與功能: lpc3131外接8k*8雙口ram與8G Flash,從雙口ram讀取數據(來自FPGA),并存至Flash中。問題: 丟數據,系統速度遠低于ram的讀速與Flash的寫速度。雙

2011-08-04 11:05:31

一、查找表LUT就是查找表,對于4輸入的LUT而言,實際上就是4位地址位,一位數據位的存儲器,能夠存儲16位數據,所以我們在FPGA設計中可以用LUT組建分布式的RAM。這樣也可以解釋我們在設計中

2021-07-28 08:42:17

問題沒有解決。由于是第一次使用雙口RAM還不是很了解,其中左側的數據和地址線以及控制接口全部接到FPGA的I/O口,如果右側的所有信號線也全部接到USB控制芯片的話會出現管腳不夠用的情況。希望各位大神給只只招,謝謝!

2014-04-16 21:14:56

基于FPGA的超高速FFT硬件實現介紹了頻域抽取基二快速傅里葉運算的基本原理;討論了基于FPGA達4 096點的大點數超高速FFT硬件系統設計與實現方法,當多組大點數進行FFT運算時,利用FPGA

2009-06-14 00:19:55

的注意,如果能有意識地利用這些原則指導日后的設計工作,將取得事半功倍的效果乒乓操作“乒乓操作”是一個常常應用于數據流控制的處理技巧.乒乓操作的處理流程為:輸入數據流通過“輸入數據選擇單元”將數據流等時分

2020-05-01 07:00:00

RAM是FPGA中常用的基礎模塊,可廣泛用于緩存數據的情況,同樣它也是ROM,FIFO的基礎。本實驗將為大家介紹如何使用FPGA內部的RAM以及程序對該RAM的數據讀寫操作。1.實驗原理Xilinx

2021-01-07 16:05:28

我們如何使用Virtex-4 FPGA的Block-RAM來存儲矩陣/ Vector的內容。例如,如何在BRAM中存儲矢量A = [1 2 4 5 6 7 9 3]?OR矩陣B = 1 2 3 45 6 7 8 9 1 4 5

2020-05-27 06:43:47

我們如何使用Virtex-4 FPGA的Block-RAM來存儲矩陣/ Vector的內容。例如,如何在BRAM中存儲矢量A = [1 2 4 5 6 7 9 3]?OR矩陣B = 1 2 3 45 6 7 8 9 1 4 5

2020-05-29 09:16:36

我們如何使用Virtex-4 FPGA的Block-RAM來存儲矩陣/ Vector的內容。例如,如何在BRAM中存儲矢量A = [1 2 4 5 6 7 9 3]?OR矩陣B = [1 2 3 45 6 7 8 9 1 4 5 232 1]

2020-05-29 14:41:56

我對在 STM32 上使用 ML 和 AI 很感興趣,在花了一些時間查看 ST 文檔后,我認為使用 NanoEdge AI Studio + ST 板是幫助我理解事物的最快方法。據我所知,ST

2022-12-06 07:35:35

大家好,我有FPGA virtext -5 ML510板,我想將圖像存儲在DD RAM中,我聲明一個數組,并希望存儲在DD RAM的基地址中,如果有人可以幫助我,那么使用Xilinx SDK 11從RAM寫入和讀取圖像數據的過程是什么。

2020-06-03 12:03:38

是否可以通過USB將數據從我的Spartan 3E FPGA Block RAM發送到我的計算機?我試圖通過串行RS232發送數據,但那不起作用,所以想找到一個發送數據的備用路徑。如果可能的話,那是什么鍛煉?

2019-08-09 09:23:59

,sensAITM提供了供開發人員評估、開發和部署基于FPGA的機器學習/人工智能解決方案所需的全部資源,包括模塊化硬件平臺、演示示例、參考設計、神經網絡IP核、軟件開發工具和定制化設計服務。圖1:sensAI架構

2020-10-23 11:43:04

我正在嘗試使用virtex 5上的Block RAM來實現延遲線。延遲線需要將數據延遲一個時鐘周期。這可能使用Block RAM嗎?我嘗試使用簡單的雙端口RAM,“先讀”作為操作模式。我正在寫一個

2020-06-18 15:40:33

AI芯片產品的設計和開發;技巧提升:課程剖析AI芯片開發流程及技巧,學員可熟悉AI芯片架構設計的各種處理技巧、芯片架構在FPGA上執行的方法,掌握AI芯片的工程應用和部署;配套開發板:配備與課程配套

2019-07-19 11:54:01

使用AI解決問題提供了第1次經驗,但它導致了分散的跨組織的ML算法。不幸的是,這種分散的ML算法不能完全釋放數據中隱藏的價值,也不能充分利用組織所擁有的寶貴業務知識。此外,它們還會給公司帶來潛在風險。分散

2019-05-06 16:46:05

你好,我正在開發一個在VC709開發板上使用Virtex7 FPGA的系統。該應用程序使用32Mb的板載Block RAM作為設計中的存儲元件。 FPGA配置序列完成后,有沒有一種方法可以使用PC上的JTAG / USB接口直接寫入和讀取Block RAM的內容?謝謝,

2019-09-29 14:00:01

嗨,我正在使用“RAMB16_S36”原始實現一個512內存寬度的Block Ram。我通讀了XAPP463用戶指南,但我顯然不了解初始化屬性。INIT_00是否對應于[255:0] Block

2019-07-22 08:10:27

] .ram.r / s3a_noinit.ram / dpram.ram有一個有效信號,但沒有連接數據輸入引腳。無效數據可能會寫入BlockRAM如何更正此錯誤并在bitgen退出之前重復3次警告

2019-06-04 09:08:32

嗨,我想為我的設計使用比特流加密,我遇到了一個關于9K Block RAM的問題,在答案記錄39999中描述了r然后我決定在我的設計中刪除所有9k Block RAM并將它們更改為16k Block

2019-06-06 07:23:18

Vertex 7 FPGA的最大DSP級聯限制是多少? Vivado有沒有辦法提取這些數據?謝謝!

2020-07-19 16:26:03

嗨!我有一個關于分布式RAM和Block RAM的問題。芯片中有menexternalmemory或內存嗎?請詳細告訴我。謝謝!

2019-11-07 09:07:16

賽靈思Virtex-6 HXT FPGA ML630評估套件采用SiTime電子發燒友振具體型號為:SIT9102AI-243N25E200.0000,而目前針對這一型號sitime推出了抖動更低

2014-11-17 15:07:35

概述EasyGo FPGA Coder Block是嵌入Matlab/Simulink里面的FPGA 仿真工具包軟件。提供了一些基礎的函數庫以及常用的控制函數模塊,配合

2022-05-19 09:16:05

分析了西藏的湍流通量數據和地表溫度數據,提出了表征地表溫度變化特征的地表溫度特征量。運用時間序列分析的方法,得到地表溫度特征量和湍流通量之間的傳遞函數模型,

2009-03-02 22:00:19 22

22 為了在高速采集時不丟失數據,在數據采集系統和CPU之間設置一個數據暫存區。介紹雙口RAM的存儲原理及其在數字系統中的應用。采用FPGA技術構造雙口RAM,實現高速信號采集系

2010-02-11 11:20:27 69

69 本文提出了一種概率關聯規則算法,通過使用概率的方法估算任意數據項集在事務數據庫中出現的概率來求候選頻繁項集,并給出了相關算法描述及其算法實現。將本算法與Apriori算法

2010-02-25 14:58:44 15

15 基于Actel FPGA 的雙端口RAM 設計雙端口RAM 芯片主要應用于高速率、高可靠性、對實時性要求高的場合,如實現DSP與PCI 總線芯片之間的數據交換接口電路等。但普通雙端口RAM 最大

2010-11-15 17:44:19 82

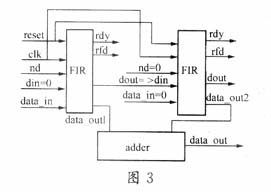

82 【摘 要】 提出了一種基于分布式算法的,采用基于RAM之移位寄存器來設計可級聯FIR濾波器的設計方法。 &

2009-05-11 19:45:52 983

983

數字級聯非壓縮視頻、數據光端機級聯

2016-12-30 14:50:56 0

0 FPGA內部的RAM M9K

2017-04-07 11:40:04 4

4 Virtex 型FPGA 芯片是Xilinx 公司芯片系列中的一種,Virtex 系列的數據流及配置邏輯與XC4000 的數據流及配置邏輯有顯著不同,但卻與Xilinx 的FPGA 家族保持了很大

2017-11-18 11:37:38 2027

2027 FPGA中RAM的使用探索。以4bitX4為例,數據位寬為4,深度為4。

2018-03-28 17:07:28 9726

9726

本文介紹了如何在FPGA 中利用Block RAM 的特殊結構實現HDTV視頻增強算法中灰度直方圖統計。

2019-07-10 08:10:00 2578

2578 了解新的Block RAM級聯功能,如何使用它,以及如何利用其功能和性能優勢。

2018-11-23 06:56:00 4470

4470 電阻(Resistance,通常用“R”表示),是一個物理量,在物理學中表示導體對電流阻礙作用的大小。導體的電阻越大,表示導體對電流的阻礙作用越大。不同的導體,電阻一般不同,電阻是導體本身的一種特性。電阻將會導致電子流通量的變化,電阻越小,電子流通量越大,反之亦然。而超導體則沒有電阻。

2019-03-28 14:36:09 4266

4266 電阻,因為物質對電流產生的阻礙作用,所以稱其該作用下的電阻物質。電阻將會導致電子流通量的變化,電阻越小,電子流通量越大,反之亦然。沒有電阻或電阻很小的物質稱其為電導體,簡稱導體。不能形成電流傳輸的物質稱為電絕緣,稱絕緣體。

2019-04-20 09:55:31 54282

54282 電阻,因為物質對電流產生的阻礙作用,所以稱其該作用下的電阻物質。電阻將會導致電子流通量的變化,電阻越小,電子流通量越大,反之亦然。沒有電阻或電阻很小的物質稱其為電導體,簡稱導體。不能形成電流傳輸的物質稱為電絕緣體,簡稱絕緣體。

2020-06-08 16:00:14 3331

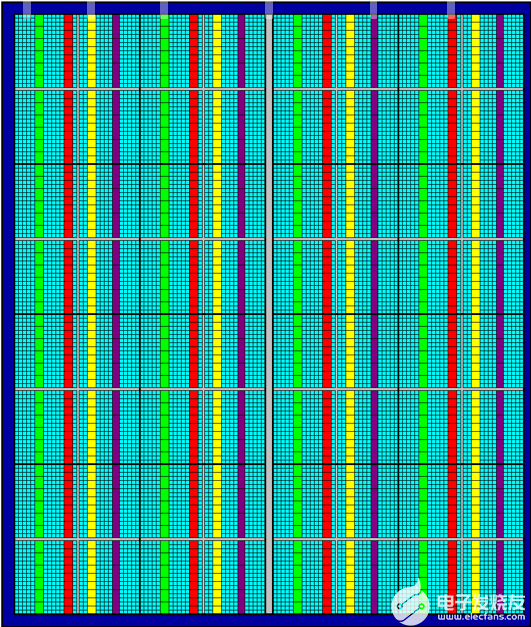

3331 些大材小用,因此xilinx公司在其FPGA內部專門集成了很多存儲器模塊,稱作Block RAM,其猶如slice海洋當中的一顆顆明珠,專門實現數據暫存功能,且每個時鐘區域都布置了若干個Block

2020-11-23 14:08:43 7379

7379

的寄存器輸出,你要同時檢查數據流的時序關系是否正確。在修改了時序關系后,可以按照我們之前的介紹,在GUI里使能Block RAM的輸出

2021-03-26 15:50:27 1570

1570

本文檔的主要內容詳細介紹的是FPGA的RAM存儲資源詳細資料說明包括了:1、 FPGA存儲資源簡介,2、 不同廠家的 Block RAM 布局,3、 塊 RAM 和分布式 RAM 資源,4、 Xilinx Block RAM 架構及應用

2020-12-09 15:31:00 10

10 在FPGA中block ram是很常見的硬核資源,合理的利用這些硬件資源一定程度上可以優化整個設計,節約資源利用率,充分開發FPGA芯片中的潛在價值,本文結合安路科技FPGA做簡單總結,說明基本原理。

2020-12-24 14:28:09 916

916 FPGA可以調用分布式RAM和塊RAM兩種RAM,當我們編寫verilog代碼的時候如果合理的編寫就可以使我們想要的RAM被綜合成BRAM(Block RAM)或者DRAM(Distributed

2020-12-30 16:27:52 9

9 RAM是FPGA中常用的基礎模塊,可廣泛用于緩存數據的情況,同樣它也是ROM,FIFO的基礎。本實驗將為大家介紹如何使用FPGA內部的RAM以及程序對該RAM的數據讀寫操作。

2022-02-08 15:50:49 12183

12183

外圍IP超高帶寬需求。本文首先談談Speedster7t FPGA的片上SRAM,也就是Block RAM針對傳統的結構所做出的一些優化。

2022-07-05 15:37:41 925

925 (人工智能)和ML(機器學習)的日益普及開辟了一個充滿可能性的新世界,PC廠商和生態系統巨頭都在尋求將這些先進的新功能添加到其產品功能集中。 在本篇博文中,萊迪思將討論PC中AI/ML功能的增長趨勢,為什么FPGA非常適合實現這些新

2022-09-08 17:19:25 931

931 在 FPGA 上實施 AI/ML 的選項

2022-12-28 09:51:08 525

525 本文主要講述了Speedster7t FPGA的片上SRAM,也就是Block RAM針對傳統的結構所做出的一些優化。

2023-07-13 17:24:15 302

302

ai芯片技術可以分為不同的體系架構。下面將對ai芯片技術架構做詳細介紹。 首先,ai芯片技術架構可以分為顯卡、TPU和FPGA三類。顯卡是目前ai應用中使用最為廣泛的一種芯片。nvidia公司推出的GTX和tesla系列顯卡擁有超高的并行運算能力,

2023-08-09 14:28:47 807

807 設計都涉及到對RAM的讀寫操作。在FPGA芯片中,RAM也叫做存儲塊(Block RAM),可以存儲大量的數據。 FPGA中的RAM可以一次讀取多個數據,這是因為RAM的結構是一個多列的數據表格,其中每一列都是一個包含多個存儲單元的塊。通過在時鐘的一次上升沿來讀取RAM中的數據,這個操作必須在一個

2023-10-18 15:28:20 598

598 二是明晰 TDN 的可信數據流通關鍵技術范疇。從保障數據隱私安全、流通過程可控可信、跨節點跨平臺跨技術互聯互通等角度歸納、分析實現數據可信流通的關鍵技術方法。

2023-11-06 16:50:24 504

504

2024年2月29日,是德科技(Keysight Technologies,Inc.)宣布,針對人工智能(AI)和機器學習(ML)基礎設施生態系統,推出了 AI數據中心測試平臺,旨在加速AI / ML網絡驗證和優化的創新。

2024-02-29 09:32:49 207

207

FPGA雙口RAM的使用主要涉及配置和使用雙端口RAM模塊。雙端口RAM的特點是有兩組獨立的端口,可以對同一存儲塊進行讀寫操作,從而實現并行訪問。

2024-03-15 13:58:14 81

81

電子發燒友App

電子發燒友App

評論