流片,到底經(jīng)歷了哪些步驟呢?本文將詳細(xì)解析SOC設(shè)計(jì)的全流程。一、定義需求與規(guī)格首先,SOC設(shè)計(jì)的第一步是明確需求與規(guī)格。這包括確定產(chǎn)品的目標(biāo)功能、性能指標(biāo)、功耗限

2023-10-21 08:28:16 1159

1159

BOARD BATTERY FOR SOC'S

2023-03-29 19:51:22

SOC一上電就進(jìn)入wfi狀態(tài)。當(dāng)從核需要繼續(xù)啟動(dòng)時(shí),該core從BL1 BL2 BL31正常流程啟動(dòng)時(shí),會(huì)在BL1、BL2 at EL3、BL31中,強(qiáng)制跳轉(zhuǎn)到mailbox的地址,跳過(guò)主核已經(jīng)初始化

2023-02-21 15:11:44

為什么verilog可以描述硬件?在SOC設(shè)計(jì)中使用verilog,和FPGA為對(duì)象使用verilog,有什么區(qū)別?SOC流程和FPGA流程的不同之處在哪里?

2021-06-21 07:02:59

SOC設(shè)計(jì)流程及其集成開(kāi)發(fā)環(huán)境.pdf(216.79 KB)

2019-09-16 08:38:19

在這篇文章中,我們將主要的焦點(diǎn)放在數(shù)字集成電路(IC)的發(fā)展上,簡(jiǎn)介數(shù)字IC設(shè)計(jì)的進(jìn)展與當(dāng)今普遍采用的設(shè)計(jì)流程;以及介紹SOC(SystemOnChip)這個(gè)今天在電子相關(guān)產(chǎn)業(yè)相當(dāng)熱門的領(lǐng)域,筆者將

2023-09-20 07:24:04

Altera公司意欲通過(guò)更先進(jìn)的制程工藝和更緊密的產(chǎn)業(yè)合作,正逐步強(qiáng)化FPGA協(xié)同處理器,大幅提升SoC FPGA的整體性能,為搶攻嵌入式系統(tǒng)市場(chǎng)版圖創(chuàng)造更大的差異化優(yōu)勢(shì)。隨著SoC FPGA在

2019-08-26 07:15:50

在設(shè)計(jì)一款面向多媒體應(yīng)用的嵌入式系統(tǒng)時(shí),實(shí)時(shí)性能非常重要。本文提出了一種基于ARM7TDMI內(nèi)核的SoC中語(yǔ)音處理系統(tǒng)的設(shè)計(jì)方案,并根據(jù)該款SoC具有eSRAM的特點(diǎn),進(jìn)行了系統(tǒng)性能的優(yōu)化。對(duì)樣機(jī)

2019-10-24 07:12:24

現(xiàn)實(shí)世界中的應(yīng)用是無(wú)限的、無(wú)價(jià)的。這些芯片經(jīng)常用于物聯(lián)網(wǎng)、嵌入式系統(tǒng)、智能手機(jī)、汽車、相機(jī)、平板電腦等相關(guān)系統(tǒng)。Soc 通過(guò)使用單個(gè)芯片來(lái)管理系統(tǒng)的各個(gè)方面,從而幫助提高性能。根據(jù)系統(tǒng)類型

2022-04-01 11:18:18

SoC是什么意思?SoC是由哪些部件封裝組成的?

2021-10-19 06:07:13

SoC測(cè)試技術(shù)傳統(tǒng)的測(cè)試方法和流程面臨的挑戰(zhàn)是什么?SoC測(cè)試技術(shù)一體化測(cè)試流程是怎樣的?基于光子探測(cè)的SoC測(cè)試技術(shù)是什么?有什么目的?

2021-04-15 06:16:53

SoC芯片的開(kāi)發(fā)流程SoC芯片開(kāi)發(fā)流程大致分為四個(gè)階段,其中大部分工作都是借助于電子設(shè)計(jì)自動(dòng)化(EDA)工具完成的。總體設(shè)計(jì)總體設(shè)計(jì)階段的任務(wù)是按照系統(tǒng)需求說(shuō)明書(shū)確定SoC的性能參數(shù),并據(jù)此進(jìn)行系統(tǒng)

2021-11-08 08:33:27

家庭娛樂(lè)市場(chǎng)上的新興標(biāo)準(zhǔn)是什么?SoC設(shè)計(jì)中杜比數(shù)字加的實(shí)現(xiàn)優(yōu)化方法是什么

2021-06-08 07:15:27

現(xiàn),盡可能降低功耗會(huì)導(dǎo)致效率降低,甚至是嚴(yán)重的故障。這些難題并不會(huì)隨時(shí)間變化而逐漸變得簡(jiǎn)單。芯片設(shè)計(jì)人員在提高能效方面嘗試了很多方法,提出了聽(tīng)起來(lái)非常激進(jìn)的想法。在今年的設(shè)計(jì)自動(dòng)化大會(huì)的一次小組討論中,TI

2014-09-02 14:51:19

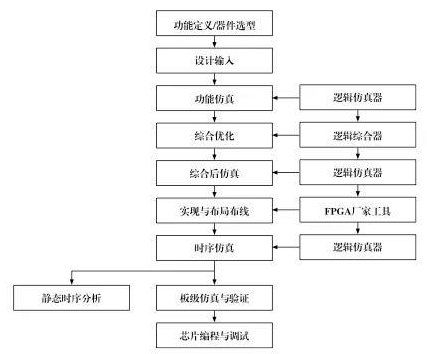

引言 隨著技術(shù)的進(jìn)一步發(fā)展,SoC設(shè)計(jì)面臨著一些諸如如何進(jìn)行軟硬件協(xié)同設(shè)計(jì),如何縮短電子產(chǎn)品開(kāi)發(fā)周期的難題。為了解決SoC設(shè)計(jì)中遇到的難題,設(shè)計(jì)方法必須進(jìn)一步優(yōu)化。因此,人們提出了基于FPGA

2019-07-12 07:25:22

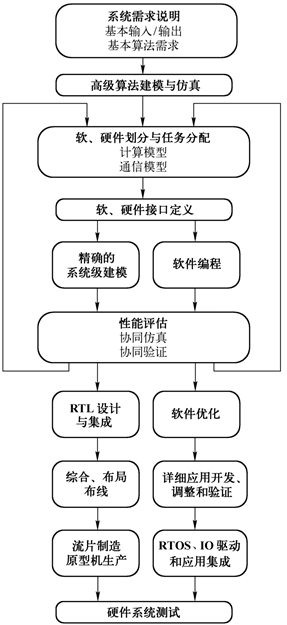

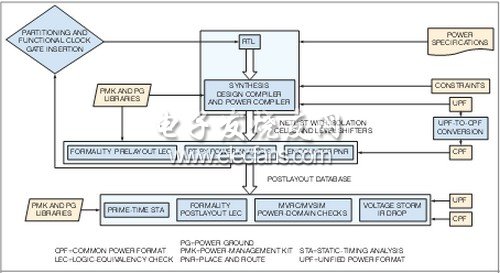

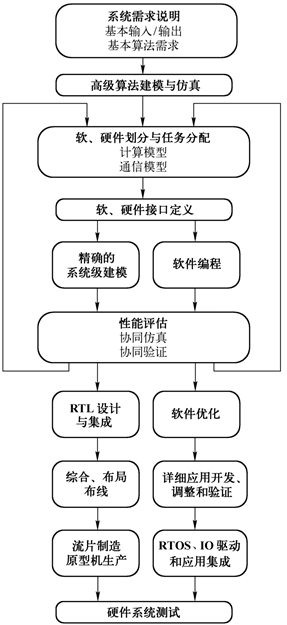

SoC設(shè)計(jì)流程一、SoC設(shè)計(jì)的特點(diǎn)二、軟硬件協(xié)同設(shè)計(jì)流程2.1 系統(tǒng)需求說(shuō)明2.2 高級(jí)算法建模與仿真2.3 軟硬件劃分過(guò)程2.4 軟硬件同步設(shè)計(jì)三、基于標(biāo)準(zhǔn)單元的SoC芯片設(shè)計(jì)流程一、SoC

2021-11-11 07:48:45

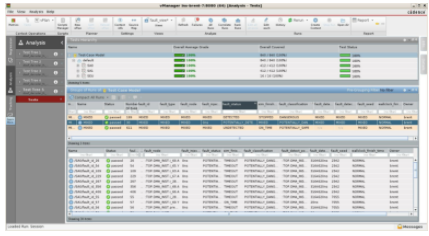

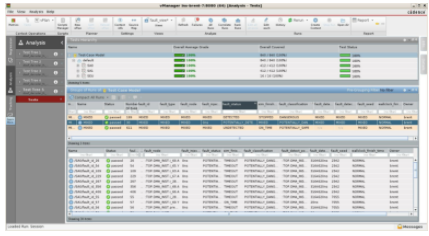

SoC芯片的規(guī)模一般遠(yuǎn)大于普通的ASIC,同時(shí)深亞微米工藝帶來(lái)的設(shè)計(jì)困難等使得SoC設(shè)計(jì)的復(fù)雜度大大提高。仿真與驗(yàn)證是SoC設(shè)計(jì)流程中最復(fù)雜、最耗時(shí)的環(huán)節(jié),約占整個(gè)芯片開(kāi)發(fā)周期的50%~80%,采用

2019-10-11 07:07:07

soc計(jì)算方法,BMS中的SOC的計(jì)算其實(shí)可以分為三大部分:1、電芯層級(jí)的SOC計(jì)算(軟件中最真實(shí)的SOC計(jì)算,不涉及任何濾波處理);2、模組或者電池包層級(jí)的SOC計(jì)算(電芯到電池包級(jí)別的SOC映射

2021-07-27 06:13:05

我配置了SOC0和SOC1作為轉(zhuǎn)換通道,但他們轉(zhuǎn)換的數(shù)據(jù)確送入了RESULT1和RESULT2,RESULT0中沒(méi)有數(shù)據(jù),請(qǐng)問(wèn)這有可能是什么原因造成的?

2021-05-22 17:25:48

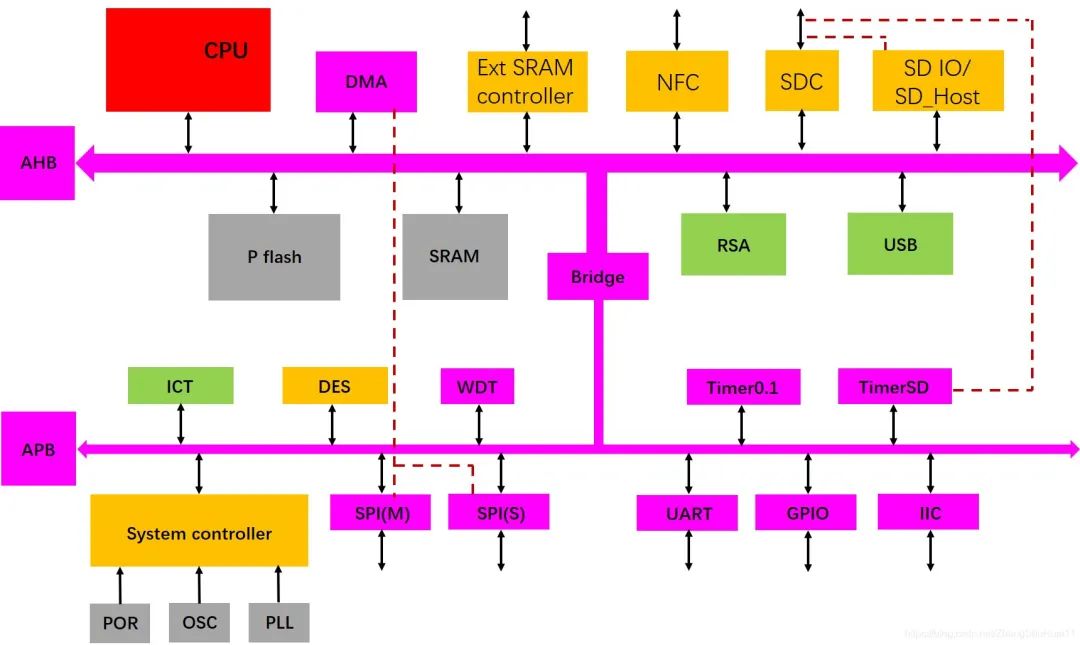

AMBA片上總線在SoC芯片設(shè)計(jì)中的應(yīng)用是什么?

2021-05-28 06:54:19

BMS中的SOC的計(jì)算有哪幾部分?怎么計(jì)算?

2021-10-09 08:59:39

CX-1SOC-0332 - CX MINIATURE CRYSTALS - EUROQUARTZ limited

2022-11-04 17:22:44

CX-1SOC-0332B - CX MINIATURE CRYSTALS - EUROQUARTZ limited

2022-11-04 17:22:44

CX-1SOC-0332C - CX MINIATURE CRYSTALS - EUROQUARTZ limited

2022-11-04 17:22:44

CX-1SOC-0332I - CX MINIATURE CRYSTALS - EUROQUARTZ limited

2022-11-04 17:22:44

CX-1SOC-0332M - CX MINIATURE CRYSTALS - EUROQUARTZ limited

2022-11-04 17:22:44

CX-1SOC-0332S - CX MINIATURE CRYSTALS - EUROQUARTZ limited

2022-11-04 17:22:44

雖然可測(cè)性設(shè)計(jì)(DFT)與內(nèi)置自檢(BIST)技術(shù)已在SoC(系統(tǒng)級(jí)芯片)設(shè)計(jì)中受到廣泛關(guān)注,但仍然只是被看作“后端”的事。實(shí)際上,這些技術(shù)在器件整個(gè)設(shè)計(jì)周期中都非常重要,可以保證產(chǎn)品測(cè)試錯(cuò)誤覆蓋率

2011-12-15 09:53:14

DK-SOC-10AS066S-A

2023-03-28 13:19:47

微電子技術(shù)已經(jīng)發(fā)展到SOC階段,即集成系統(tǒng)(Integrated System)階段,相對(duì)于集成電路(IC)的設(shè)計(jì)思想有著革命性的變化。SOC是一個(gè)復(fù)雜的系統(tǒng),它將一個(gè)完整產(chǎn)品的功能集成在一個(gè)芯片上

2017-01-10 15:50:15

FPGA能否繼續(xù)在SoC類應(yīng)用中替代ASIC?CoreConsole工具是什么,有什么功能?

2021-04-08 06:23:39

MCU與SoC都有廣闊空間 SoC更多是理論方向

2020-03-09 06:10:43

流程控制無(wú)非就是if else之類的控制語(yǔ)句,今天我們來(lái)看一下Python中的流程控制會(huì)有什么不太一樣的地方。

2021-06-28 08:54:57

。為了得到一個(gè)感覺(jué)如何最好地實(shí)時(shí)操作系統(tǒng)添加到我們的ZYNQ SoC系統(tǒng)中,我們將使用最流行的實(shí)時(shí)操作系統(tǒng)之一左右,在μC/ OS-III Micrium的。這RTOS或更早的版本中它已經(jīng)用在了一些非常

2019-10-23 07:44:24

STM32中TIM2_Init程序流程是怎樣的?

2021-11-24 06:40:39

SoC器件上快速地加速和集成您的計(jì)算機(jī)視覺(jué)應(yīng)用。本次研討會(huì)將通過(guò)對(duì)一個(gè)具體案例的流程進(jìn)行“逐層拆解(Step-by-Step)一個(gè)設(shè)計(jì)案列”的方式,向您介紹如何利用Vivado HLS(高層次綜合

2013-12-30 16:09:34

/tuya-sandwich-wifi-and-ble-soc-board-BK7231N?id=Kao72e6net3bs。首先說(shuō)一下開(kāi)發(fā)感受,雖然號(hào)稱零代碼開(kāi)發(fā),但是做為首次用戶流程還是很麻煩的,平臺(tái)多,軟件多,不花點(diǎn)時(shí)間很難理順,當(dāng)然用熟練了,肯定是很方便

2022-05-08 02:00:04

什么是SoC?SoC是由哪些部件組成的?

2021-10-19 06:29:10

什么是Python中的流程控制?

2021-10-09 07:24:01

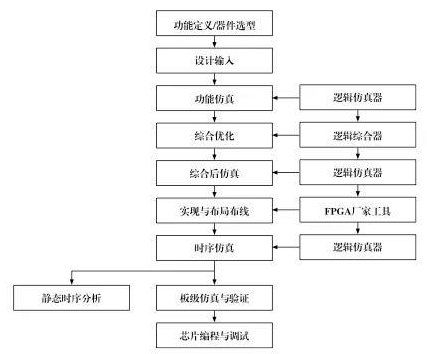

關(guān)系在搭建SoC的過(guò)程中需要使用的工具軟件有Modelsim,Vivado,Keil,實(shí)現(xiàn)流程如下圖。實(shí)現(xiàn)流程我們通過(guò)Arm DesignStart獲取的是一個(gè)Verilog語(yǔ)言描述的軟核,我們通過(guò)添加

2022-04-01 17:48:02

SoC原型的Handel-C描述及其實(shí)現(xiàn)流程是怎樣的?利用RC1000和SoC設(shè)計(jì)展示評(píng)估平臺(tái)RC200搭建一個(gè)原型驗(yàn)證系統(tǒng)的樣機(jī)?

2021-05-28 06:15:18

本文討論的是基于ARM IP的大規(guī)模SoC中的電源(時(shí)鐘,復(fù)位等)管理,適用于眾核處理器,手機(jī)SoC,汽車SoC等等。如果是小規(guī)模的設(shè)計(jì)可能就不適用了,比如MCU或者是簡(jiǎn)單應(yīng)用的IoT芯片。關(guān)于芯片

2022-04-02 10:08:51

混合信號(hào)共同仿真環(huán)境在指定的SoC中驗(yàn)證混合信號(hào)組件。 在PSC流程中,混合信號(hào)仿真是沒(méi)有必要的。對(duì)待組件內(nèi)的模擬功能像開(kāi)架式分離組件一般。就像組件廠商一樣,數(shù)據(jù)規(guī)格所提供的模擬功能電子特征的許多

2011-10-16 22:55:10

SoC設(shè)計(jì)的特點(diǎn)軟硬件協(xié)同設(shè)計(jì)流程基于標(biāo)準(zhǔn)單元的SoC芯片設(shè)計(jì)流程

2021-01-26 06:45:40

如何去設(shè)計(jì)SoC中的低功耗RF收發(fā)器?

2021-05-25 07:04:51

SoC芯片結(jié)構(gòu)及物理實(shí)現(xiàn)流程介紹SoC芯片時(shí)序約束設(shè)計(jì)的關(guān)鍵在于功耗管理控制模塊的時(shí)序約束時(shí)鐘樹(shù)設(shè)計(jì)的內(nèi)容有哪些?

2021-04-13 06:45:17

基于傳統(tǒng)六晶體管(6T)存儲(chǔ)單元的靜態(tài)RAM存儲(chǔ)器塊一直是許多嵌入式設(shè)計(jì)中使用ASIC/SoC實(shí)現(xiàn)的開(kāi)發(fā)人員所采用的利器,因?yàn)檫@種存儲(chǔ)器結(jié)構(gòu)非常適合主流的CMOS工藝流程,不需要增添任何額外的工藝步驟。那么究竟怎么樣,才能實(shí)現(xiàn)嵌入式ASIC和SoC的存儲(chǔ)器設(shè)計(jì)呢?

2019-08-02 06:49:22

這樣的項(xiàng)目具有滲透到技術(shù)中的趨勢(shì)。概括地說(shuō),當(dāng)今的競(jìng)爭(zhēng)力就是提供更高層次的抽象和選擇。客戶(無(wú)論是購(gòu)買新智能手機(jī)的青少年,還是就SoC貨比三家的工程團(tuán)隊(duì))想要更多的功能、更好的性能、更高的易用性和更低

2017-04-05 14:17:46

目錄嵌入式 Linux 啟動(dòng)

流程簡(jiǎn)介啟動(dòng)

流程Bootloader 簡(jiǎn)介市面上可見(jiàn)的 bootloader入式 Linux 啟動(dòng)

流程簡(jiǎn)介對(duì)于一個(gè)

SoC 芯片而言,bootloader 必不可少。因?yàn)?/div>

2021-11-04 09:04:18

嵌入式開(kāi)發(fā)板開(kāi)發(fā)流程有哪些呢?SOC系統(tǒng)開(kāi)發(fā)流程有哪些呢?嵌入式開(kāi)發(fā)板開(kāi)發(fā)與SOC系統(tǒng)開(kāi)發(fā)有哪些不同之處呢?

2021-12-27 07:55:18

”和“硬件編程”的概念,熟悉SoC設(shè)計(jì)的流程。軟硬件關(guān)系在搭建SoC的過(guò)程中需要使用的工具軟件有Modelsim,Vivado,Keil,實(shí)現(xiàn)流程如下圖。實(shí)現(xiàn)流程我們通過(guò)Arm DesignStart獲取

2022-07-13 15:04:56

1、搭建一個(gè)SoC下載到安路FPGA開(kāi)發(fā)板中在本實(shí)驗(yàn)中,我們將以安路的設(shè)計(jì)軟件TangDynasty(TD)為平臺(tái),利用AHBlite總線將Block RAM與Cortex-M0裸核相連接,搭建一個(gè)

2022-08-09 17:09:36

我們這個(gè)功能設(shè)計(jì)的過(guò)程中,你不斷要考量,要考慮把性能上的要求加到我們?cè)O(shè)計(jì)的過(guò)程中來(lái),這就是我們?nèi)腋O敫嬖V大家的。那么今天的30分鐘的 SoC數(shù)字全流程漫談,其實(shí)就是想給大家先有個(gè)概念,讓大家先全面了解

2020-12-07 17:39:10

本文在XILINX FPGA中采用嵌入式處理器Picoblaze進(jìn)行SOC設(shè)計(jì),以較少的硬件資源實(shí)現(xiàn)了對(duì)串口通信數(shù)據(jù)的處理,同時(shí)采用SDRAM器件對(duì)Picoblaze的存儲(chǔ)能力進(jìn)行擴(kuò)展。

2021-04-29 06:22:32

和嵌入結(jié)構(gòu),就能實(shí)現(xiàn)充分優(yōu)化的固件特性,而不必花時(shí)間熟悉定制電路的開(kāi)發(fā)技術(shù)。SOC的設(shè)計(jì)流程如下圖。基本結(jié)構(gòu)--嵌入式系統(tǒng) 在使用SOC技術(shù)設(shè)計(jì)的應(yīng)用電子系統(tǒng)中,可以十分方便地實(shí)現(xiàn)嵌入式結(jié)構(gòu)。各種嵌入

2016-08-05 09:08:31

)的發(fā)展趨勢(shì),也是21世紀(jì)集成電路技術(shù)的主流,其為集成電路產(chǎn)業(yè)和集成電路應(yīng)用技術(shù)提供了前所未有的廣闊市場(chǎng)和難得的發(fā)展機(jī)遇。SOC為微電子應(yīng)用產(chǎn)品研究、開(kāi)發(fā)和生產(chǎn)提供了新型的優(yōu)秀的技術(shù)方法和工具,也是解決電子產(chǎn)品開(kāi)發(fā)中的及時(shí)上市(TTM——Time to Market)的主要技術(shù)與方法。

2011-09-27 11:46:06

揮更大的作用。【解密專家+V信:icpojie】 芯片解密在SoC中的應(yīng)用SoC不單可以縮小體積,還可以縮小不同 IC 間的距離,提升晶片的計(jì)算速度。然而,SoC 并非只有優(yōu)點(diǎn),要設(shè)計(jì)一顆 SoC

2017-06-28 15:38:06

在介紹嵌入式 SoC IC 概念的基礎(chǔ)上,介紹基于重用(re-use)的 SoC IC 設(shè)計(jì)方法和流程, 涉及滿足時(shí)序要求、版圖設(shè)計(jì)流程和測(cè)試設(shè)計(jì)的問(wèn)題, 并給出設(shè)計(jì)計(jì)劃考慮項(xiàng)目。

2009-05-13 16:09:42 28

28 基于ASIC/SoC的UART核的設(shè)計(jì)

摘要:本文描述了通用異步收發(fā)機(jī)UART(Universal Asynchronous Receive Transmitter)核的一種優(yōu)化設(shè)計(jì)實(shí)現(xiàn)的設(shè)計(jì)流程。通過(guò)采用劃分功能模塊使結(jié)構(gòu)直觀

2010-06-19 09:55:32 26

26 全球電子設(shè)計(jì)創(chuàng)新領(lǐng)先企業(yè)Cadence設(shè)計(jì)系統(tǒng)公司,今天宣布了業(yè)界最全面的用于系統(tǒng)級(jí)芯片(SoC)驗(yàn)證的通用驗(yàn)證方法學(xué)(UVM)開(kāi)源參考流程。為了配合Cadence EDA360中SoC實(shí)現(xiàn)能力的策略,

2010-06-28 08:29:14 2240

2240 集成電路設(shè)計(jì)流程 集成電路設(shè)計(jì)方法 數(shù)字集成電路設(shè)計(jì)流程 模擬集成電路設(shè)計(jì)流程 混合信號(hào)集成電路設(shè)計(jì)流程 SoC芯片設(shè)計(jì)流程

2011-03-31 17:09:12 380

380 美高森美公司發(fā)布Libero? SoC v10.0 (第十版Libero? SoC)。這一新版Libero集成式設(shè)計(jì)環(huán)境(IDE)可為系統(tǒng)單芯片(SoC)設(shè)計(jì)人員提供多項(xiàng)新功能,包括提升易用性、增加嵌入式設(shè)計(jì)流程的集成度,以

2011-12-20 09:02:58 919

919 運(yùn)用SoC技術(shù)設(shè)計(jì)系統(tǒng)芯片,一般先要進(jìn)行軟硬件劃分,將設(shè)計(jì)基本分為兩部分:芯片硬件設(shè)計(jì)和軟件協(xié)同設(shè)計(jì)。

2012-10-12 16:54:28 2231

2231 本專題為你簡(jiǎn)述片上系統(tǒng)SoC相關(guān)知識(shí)及設(shè)計(jì)測(cè)試。包括SoC定義,SoC設(shè)計(jì)流程,SoC設(shè)計(jì)的關(guān)鍵技術(shù),SoC設(shè)計(jì)范例,SoC設(shè)計(jì)測(cè)試及驗(yàn)證方法,最新SoC芯片解決方案。

2012-10-12 17:57:20

我在論壇上寫(xiě)過(guò)一個(gè)。《如何搭建SoC項(xiàng)目的基本Testbench(我的流程)》,這里挑重要的和有改變的地方說(shuō)一下。

假設(shè)這個(gè)SoC有CPU系統(tǒng)、內(nèi)存控制器、總線拓?fù)洹AD、Clockreset和一些邏輯功能模塊。

2018-01-05 10:20:43 23289

23289

,大數(shù)據(jù)模式代表大數(shù)據(jù)源+全部方法論(傳統(tǒng)方法論+大數(shù)據(jù)方法論)的處理流程。 1基本業(yè)務(wù)環(huán)節(jié)的變化 首先我們來(lái)看一下數(shù)據(jù)業(yè)務(wù)流程在兩種模式下的變化。 從上圖可以發(fā)現(xiàn),大數(shù)據(jù)下的業(yè)務(wù)流程,

2018-02-21 09:13:00 4952

4952

SDSoC是Xilinx推出的一個(gè)基于簡(jiǎn)便易用的Eclipse集成設(shè)計(jì)環(huán)境(IDE)的工具套件,它支持Zynq-7000全可編程SoC和Zynq UltraScale+ MPSoC,以及MicroBlaze處理器,可以為開(kāi)發(fā)者提供類似嵌入式 C/C++/OpenCL 應(yīng)用的開(kāi)發(fā)體驗(yàn)。

2018-05-01 16:53:00 14997

14997 Altera公司今天宣布,使用MathWorks的業(yè)界標(biāo)準(zhǔn)工作流程,為其基于ARM的SoC提供新支持。MathWorks 2014b版包括了適用于Altera SoC的自動(dòng)、高度集成、基于模型

2018-09-08 10:04:00 681

681 小梅哥最新款FPGA_SOC

2019-08-30 06:10:00 3548

3548

目前微電子技術(shù)已經(jīng)發(fā)展到 SOC 階段,即集成系統(tǒng)(Integrated System)階段,相對(duì)于集成電路(IC)的設(shè)計(jì)思想有著革命性的變化。SOC 是一個(gè)復(fù)雜的系統(tǒng),它將一個(gè)完整產(chǎn)品的功能集成

2020-07-13 09:53:57 2618

2618

一個(gè)完整的SoC設(shè)計(jì)包括系統(tǒng)結(jié)構(gòu)設(shè)計(jì)(也稱為架構(gòu)設(shè)計(jì)),軟件結(jié)構(gòu)設(shè)計(jì)和ASIC設(shè)計(jì)(硬件設(shè)計(jì))。SoC設(shè)計(jì)更需要了解整個(gè)系統(tǒng)的應(yīng)用,定義出合理的芯片架構(gòu),使得軟硬件配合達(dá)到系統(tǒng)最佳工作狀態(tài)。因而,軟硬件協(xié)同設(shè)計(jì)被越來(lái)越多地采用。

2021-01-20 23:19:18 1005

1005

一個(gè)完整的SoC設(shè)計(jì)包括系統(tǒng)結(jié)構(gòu)設(shè)計(jì)(也稱為架構(gòu)設(shè)計(jì)),軟件結(jié)構(gòu)設(shè)計(jì)和ASIC設(shè)計(jì)(硬件設(shè)計(jì))。SoC設(shè)計(jì)更需要了解整個(gè)系統(tǒng)的應(yīng)用,定義出合理的芯片架構(gòu),使得軟硬件配合達(dá)到系統(tǒng)最佳工作狀態(tài)。因而,軟硬件協(xié)同設(shè)計(jì)被越來(lái)越多地采用。

2021-03-11 06:14:58 20

20 變化挖掘是業(yè)務(wù)流程管理的核心,從事件日志中挖掘?qū)鐦I(yè)務(wù)流程的變化尢為重要。已有對(duì)變化挖掘的分析方法大多集中在源模型或目標(biāo)模型已知的基礎(chǔ)上。文中從系統(tǒng)日志的角度提岀了一種基于成本最優(yōu)對(duì)齊的業(yè)務(wù)流程變化

2021-05-18 14:08:53 10

10 目錄嵌入式 Linux 啟動(dòng)

流程簡(jiǎn)介啟動(dòng)

流程Bootloader 簡(jiǎn)介市面上可見(jiàn)的 bootloader入式 Linux 啟動(dòng)

流程簡(jiǎn)介對(duì)于一個(gè)

SoC 芯片而言,bootloader 必不可少。因?yàn)?/div>

2021-11-01 16:32:38 11

11 SoC芯片的開(kāi)發(fā)流程SoC芯片開(kāi)發(fā)流程大致分為四個(gè)階段,其中大部分工作都是借助于電子設(shè)計(jì)自動(dòng)化(EDA)工具完成的。總體設(shè)計(jì)總體設(shè)計(jì)階段的任務(wù)是按照系統(tǒng)需求說(shuō)明書(shū)確定SoC的性能參數(shù),并據(jù)此進(jìn)行系統(tǒng)

2021-11-03 18:06:01 24

24 數(shù)字IC設(shè)計(jì)之“數(shù)字SOC全流程漫談從0到1”講師背景:閻如斌老師畢業(yè)于慕尼黑工業(yè)大學(xué)的碩士研究生,具有非常豐富的IC研發(fā)經(jīng)驗(yàn)。在集成電路的從業(yè)10多年之久,同時(shí)也是叩持電子和IC修真院的創(chuàng)始人

2021-11-05 20:51:02 15

15 SoC設(shè)計(jì)流程一、SoC設(shè)計(jì)的特點(diǎn)二、軟硬件協(xié)同設(shè)計(jì)流程2.1 系統(tǒng)需求說(shuō)明2.2 高級(jí)算法建模與仿真2.3 軟硬件劃分過(guò)程2.4 軟硬件同步設(shè)計(jì)三、基于標(biāo)準(zhǔn)單元的SoC芯片設(shè)計(jì)流程一、SoC

2021-11-06 16:21:01 37

37 確保汽車 SoC 在功能上安全還可以讓駕駛員和乘客對(duì)他們的車輛充滿信心。將安全驗(yàn)證集成到功能驗(yàn)證流程中可以是加快流程和管理符合 ISO 26262 等標(biāo)準(zhǔn)的工作的有效方法。

2022-06-13 15:17:20 1177

1177

參考目前手機(jī)SoC的市場(chǎng)格局,然后對(duì)座艙的SoC(下期)和智能駕駛的SOC(下下期)做一些展望。

2022-09-21 10:38:00 690

690 開(kāi)始SoC FPGA的學(xué)習(xí)路程還是蠻難的,不僅要熟悉整個(gè)的設(shè)計(jì)流程,而且還要掌握FPGA以及軟件方面的知識(shí),尤其大概看了一下后面的整體設(shè)計(jì)部分,操作起來(lái)還是較為繁瑣的,以至于讓人暈頭轉(zhuǎn)向。盡管如此

2023-03-30 10:13:35 6239

6239 首先,SOC設(shè)計(jì)的第一步是明確需求與規(guī)格。這包括確定產(chǎn)品的目標(biāo)功能、性能指標(biāo)、功耗限制等因素。設(shè)計(jì)師們根據(jù)這些要求,逐步細(xì)化為具體的硬件和軟件規(guī)格。

2023-10-13 11:03:51 927

927 SOC的定義多種多樣,由于其內(nèi)涵豐富、應(yīng)用范圍廣,很難給出準(zhǔn)確定義。一般說(shuō)來(lái),SOC系統(tǒng)級(jí)芯片,也有稱片上系統(tǒng),意指它是一個(gè)產(chǎn)品,是一個(gè)有專用目標(biāo)的集成電路,其中包含完整系統(tǒng)并有嵌入軟件的全部?jī)?nèi)容。同時(shí)它又是一種技術(shù),用以實(shí)現(xiàn)從確定系統(tǒng)功能開(kāi)始,到軟/硬件劃分,并完成設(shè)計(jì)的整個(gè)過(guò)程。

2023-12-22 16:40:48 1336

1336

已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論