基于IEEE1149.4的測(cè)試方法研究

根據(jù)混合信號(hào)邊界掃描測(cè)試的工作機(jī)制,提出了符合1149.4標(biāo)準(zhǔn)的測(cè)試方法,并用本研究室開發(fā)的混合信號(hào)邊界掃描測(cè)試系統(tǒng)進(jìn)行了測(cè)試驗(yàn)證。

??? 關(guān)鍵詞:混合信號(hào),邊界掃描,IEEE1149.4,測(cè)試方法

1 引 言

邊界掃描體系結(jié)構(gòu)及測(cè)試訪問端口IEEE1149.1標(biāo)準(zhǔn),對(duì)純數(shù)字電路來講,無疑是十分成功的。它雖主要是為了解決電路板互連測(cè)試(Interconnect Testing)而設(shè)計(jì)的〔1〕,亦可進(jìn)一步延伸到IC(IntegratedCircuit)級(jí)、板級(jí)和系統(tǒng)級(jí)測(cè)試。由于IEEE1149.1被廣泛地接受和使用,所以,混合信號(hào)測(cè)試總線標(biāo)準(zhǔn)IEEE1149.4〔2〕必須與1149.1標(biāo)準(zhǔn)兼容(準(zhǔn)確地說,1149.4應(yīng)當(dāng)是1149.1的超集)。它們的主要目的是支持互連測(cè)試、參數(shù)測(cè)試和功能測(cè)試。

在如圖1所示的模擬/混合信號(hào)電路板上,IC間的互連可能是簡單的連線(IEEE1149.4將其定義為簡單互連測(cè)試),也有可能是無源元件組成的阻抗網(wǎng)絡(luò)(IEEE將其定義為擴(kuò)展互連測(cè)試),甚至可能是有源網(wǎng)絡(luò)(但這種情況極少,一般都將有源元件集成到IC中了)。本文根據(jù)混合信號(hào)邊界掃描測(cè)試的工作機(jī)制,提出了符合1149.4標(biāo)準(zhǔn)的測(cè)試方法,并用本研究室開發(fā)的混合信號(hào)邊界掃描測(cè)試系統(tǒng)進(jìn)行了測(cè)試驗(yàn)證。

2 測(cè)試方法

邊界掃描技術(shù)支持多種測(cè)試操作,不同操作其測(cè)試機(jī)理有所不同,下面分別加以討論。

2.1 簡單互聯(lián)測(cè)試

互聯(lián)測(cè)試,可分為簡單互連、擴(kuò)展互連和差分互連等。簡單互連測(cè)試是指對(duì)直接通過導(dǎo)線連接的管腳進(jìn)行的互聯(lián)測(cè)試,主要用來測(cè)試器件連線間的開路、短路和網(wǎng)絡(luò)間的橋接等故障。進(jìn)行測(cè)試時(shí),先用SAMPLE/PRELOAD指令給輸出型的邊界掃描單元預(yù)置測(cè)試激勵(lì)。執(zhí)行EXTEST指令之后,捕獲該連接線上輸入型邊界掃描單元的測(cè)試響應(yīng)。然后通過比較激勵(lì)和響應(yīng)來判斷、定位故障。

對(duì)于數(shù)字引腳的簡單互連測(cè)試,首先根據(jù)PCB(Printed Circuit Board)網(wǎng)表、器件BSDL(Boundary-Scan Description Language)等相關(guān)文檔資料選擇合適的互連測(cè)試算法,如等權(quán)值抗誤判算法和極小權(quán)值-極大相異算法,WALK“0”、WALK“1”等,生成互連測(cè)試矢量,用SAMPLE/PRELOAD指令將測(cè)試激勵(lì)施加給輸出型的邊界掃描單元,然后執(zhí)行EXTEST指令進(jìn)行互連測(cè)試。這樣,互連信號(hào)就被捕獲到與之相連的另一邊界掃描器件的相應(yīng)的輸入型邊界掃描單元中。再通過掃描鏈將邊界掃描寄存器的內(nèi)容移出則可得到測(cè)試響應(yīng)。不過,必須通過一組測(cè)試矢量全集的測(cè)試,才能保證故障定位的正確。

在模擬引腳的簡單互聯(lián)測(cè)試中,為了使模擬管腳的簡單互連測(cè)試與數(shù)字管腳兼容,IEEE1149.4標(biāo)準(zhǔn) 在ABM(Analog Boundary Module)中增添了VH、VL、VTH三種不同的電平,分別代表高電平、低電平和門闕電平。在控制邏輯的控制下,將VH或VL電平施加到輸出型的模擬管腳上作為預(yù)置測(cè)試激勵(lì)(相當(dāng)于數(shù)字管腳加入高電平或低電平激勵(lì))。執(zhí)行EXTEST指令之后,通過捕獲該連接線上的輸入型模擬管腳上的電壓,并與VTH門闕電平進(jìn)行比較,將模擬量數(shù)字化為一位數(shù)字值“0”或“1”,作為輸入型模擬管腳上的測(cè)試響應(yīng),交邊界掃描鏈移出。這樣,就可將模擬電路的簡單互聯(lián)測(cè)試轉(zhuǎn)化為數(shù)字電路的互聯(lián)測(cè)試。通過對(duì)預(yù)置測(cè)試激勵(lì)和測(cè)試響應(yīng)進(jìn)行比較,就可以分析出該模擬簡單互連線是否發(fā)生了短路、斷路、橋接等故障,并且可將故障定位到管腳級(jí)。

這里有個(gè)問題值得注意,即簡單互連線發(fā)生橋接故障就相當(dāng)于線與,而線與的結(jié)果與電路的具體實(shí)現(xiàn)方式有關(guān),這在實(shí)例分析中可以看到。

2.2 差分測(cè)試

從邊界掃描技術(shù)角度來看,差分電路可分為數(shù)字差分電路和模擬差分電路。差分電路的測(cè)試有三種,即數(shù)字差分互連電路的測(cè)試、模擬差分電路的簡單互連測(cè)試和模擬差分電路的擴(kuò)展互連測(cè)試等。對(duì)于數(shù)字差分互聯(lián)測(cè)試,顯然,只需將數(shù)字差分輸入或輸出的兩個(gè)DBM(DigitalBoundary Module)看成兩單獨(dú)的DBM,采用數(shù)字管腳簡單互連的測(cè)試方法即可。

對(duì)于模擬差分邊界掃描結(jié)構(gòu),在進(jìn)行簡單互連測(cè)試時(shí),標(biāo)準(zhǔn)規(guī)定其差分輸入端至少須有五種組態(tài):即H-L(High Level-Low Level)、L-H、CD-CD(CoreDisconnect)、CD-G(Ground)和G-CD。所以,在進(jìn)行差分簡單互連測(cè)試時(shí),從差分輸出端所施加的測(cè)試激勵(lì)不能違反這些規(guī)定,除非你確知該測(cè)試對(duì)象還允許有其它組態(tài)。由于差分輸出的兩ABM具備施加VH或VL電平的能力(只是須注意,當(dāng)一個(gè)腳加VH則另一個(gè)腳須加VL,或反之),另一端又可捕獲其數(shù)字化值,所以可按非差分ABM進(jìn)行簡單的互連測(cè)試,只是激勵(lì)的施加稍有不同。

若模擬差分互連是擴(kuò)展的差分互連,可以采用完全差分測(cè)試或非完全差分測(cè)試兩種方法。若被測(cè)對(duì)象只有AT1(Analog Test)和AT2兩根模擬測(cè)試線且?guī)в胁罘蛛娐罚瑒t只能采用非完全差分測(cè)試。首先讓差分輸入的一端(如“+”端)連接AB1(Internal AnalogBus)、TBIC(Test Bus Interface Circuit)的S5,通過AT1腳輸入模擬測(cè)試激勵(lì),差分輸入的另一端(如“-”端)則通過其ABM控制邏輯連其VH、VL或VG來提供模擬測(cè)試激勵(lì)。對(duì)差分輸出響應(yīng)的獲取,先是讓差分輸出的一端經(jīng)AB2、TBIC的S6、AT2輸出,再讓差分輸出的另一端經(jīng)AB2、TBIC的S6、AT2輸出。然后再反過來,讓差分輸入“+”端接固定電平VH、VL或VG,讓差分輸入的“-”端通過AB1、TBIC的S5、AT1腳輸入原模擬測(cè)試激勵(lì),同上面一樣測(cè)量兩次。施加兩次激勵(lì)及測(cè)量四次響應(yīng)雖然麻煩一些,但I(xiàn)C器件的邊界掃描硬件電路可設(shè)計(jì)簡單些,從而節(jié)省器件成本。

進(jìn)行完全差分測(cè)試,就需要被測(cè)試對(duì)象有專門的差分測(cè)試結(jié)構(gòu),即有一對(duì)差分測(cè)試激勵(lì)輸入管腳AT1和AT1N,一對(duì)差分測(cè)試響應(yīng)捕獲管腳AT2和AT2N及相應(yīng)的TBIC和內(nèi)部總線結(jié)構(gòu)。測(cè)試時(shí),差分模擬測(cè)試激勵(lì)通過AT1和AT1N、TBIC、AB1和AB1N、差分輸入功能管腳的兩ABM的兩SB1加載到差分輸入上。其差分輸出響應(yīng)經(jīng)差分輸出功能管腳的兩ABM的兩SB2、AB2和AB2N、TBIC、AT2和AT2N輸出給外部測(cè)試響應(yīng)處理器。

2.3 參數(shù)測(cè)試

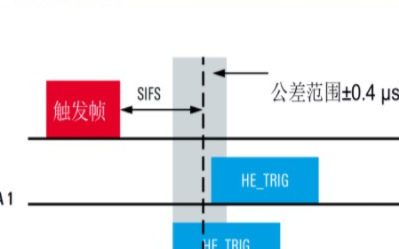

參數(shù)測(cè)試是指管腳之間不是通過簡單的導(dǎo)線連接,而是通過由電阻、電容、電感或由它們組成的網(wǎng)絡(luò)而連接的一種互聯(lián)測(cè)試,即擴(kuò)展互連測(cè)試,如圖1所示。擴(kuò)展互連測(cè)試(即參數(shù)測(cè)試),由于模擬測(cè)試總線和I/O節(jié)點(diǎn)間的開關(guān)電阻,使得屏蔽測(cè)量方法不再適用。

2.3.1 簡單網(wǎng)絡(luò)參數(shù)測(cè)試

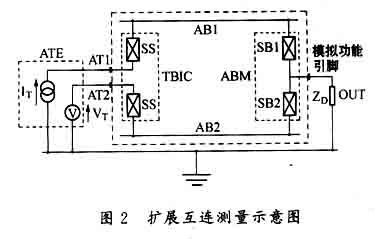

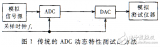

若擴(kuò)展互連網(wǎng)絡(luò)是無源的,參數(shù)測(cè)試就是要測(cè)量出該無源網(wǎng)絡(luò)中R、L、C的元件值。ATE(AutomaticTest Equipment)通過ATAP(Analog Test AccessPort)管腳AT1,經(jīng)TBIC的開關(guān)S5、ABM的SB1,就可將一個(gè)已知的模擬測(cè)試激勵(lì)電流IT施加到CUT(Circuit Under Test)上,然后可通過ABM的SB2、TBIC的開關(guān)S6、ATAP的管腳AT2,將CUT上的響應(yīng)電壓由ATE測(cè)出,記為VT,如圖2所示。

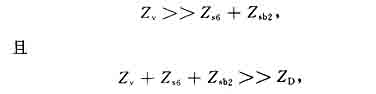

若

則VT就可近似等于CUT的端電壓。注:Zv為ATE中電壓測(cè)試系統(tǒng)的阻抗,Zs6為開關(guān)S6的阻抗,Zsb2為開關(guān)SB2的阻抗,ZD為CUT的阻抗。

若ZD是單個(gè)電阻、電感或電容,那么只需已知模擬激勵(lì)電流信號(hào)的頻率和幅度就可計(jì)算出其元件值。若ZD跨接在兩模擬功能管腳之間,它的測(cè)量分兩步進(jìn)行。首先,通過對(duì)TBIC和ABM的控制,讓激勵(lì)電流信號(hào)通過AT1施加到指定F1上,通過AT2腳獲取該F1端的電位。再改變對(duì)TBIC和ABM的控制,讓激勵(lì)電流信號(hào)通過AT1施加到指定ABM上,通過AT2腳獲取該F2端的電位。最后,計(jì)算出ZD上的電壓降,結(jié)合已知激勵(lì)電流信號(hào)的頻率和幅度值就可計(jì)算出其元件值。若ZD是由多個(gè)電阻、電感或電容組成的單端口網(wǎng)絡(luò),那么只需通過施加一組不同頻率的激勵(lì)電流,然后測(cè)試量對(duì)應(yīng)頻率ZD上的電壓降就可得到一方程組,解此方程組即可求出各元件值。

2.3.2 Delta網(wǎng)絡(luò)的參數(shù)測(cè)試

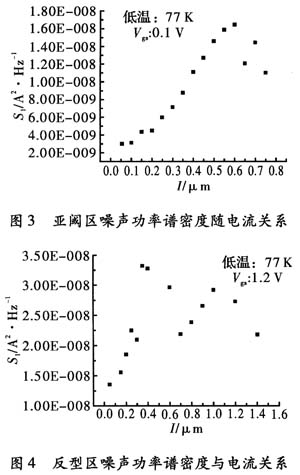

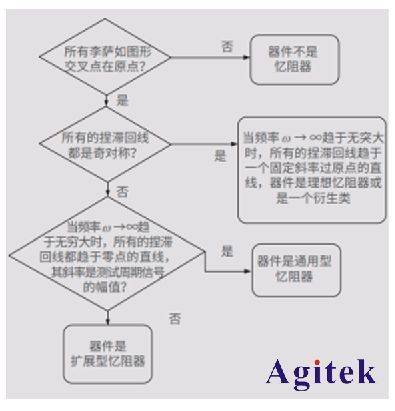

對(duì)于Delta互連網(wǎng)絡(luò),如圖3所示,可以采用下面的方法進(jìn)行測(cè)量。

(1)P4腳接VG,P3和P2腳斷開。AT1激勵(lì)I(lǐng)1施加到P1腳,通過AT2測(cè)量P1腳的電位VP11;

(2)P4腳接VG,P3腳斷開。AT1激勵(lì)I(lǐng)1施加到P1腳,通過AT2測(cè)量P2腳的電位VP21;

(3)P4腳接VG,P2腳斷開。AT1激勵(lì)I(lǐng)1施加到P1腳,通過AT2測(cè)量P3腳的電位VP31;

(4)P4腳接VG,P2腳斷開。AT1激勵(lì)I(lǐng)1施加到P3腳,通過AT2測(cè)量P1腳的電位VP12;

(5)P4腳接VG,P1腳斷開。AT1激勵(lì)I(lǐng)1施加到P3腳,通過AT2測(cè)量P2腳的電位VP22;

(6)P4腳接VG,P2和P1腳斷開。AT1激勵(lì)I(lǐng)1施加到P3腳,通過AT2測(cè)量P3腳的電位VP32。

由這些數(shù)據(jù)足夠解出Z1、Z2、Z3的值〔3〕。當(dāng)然,若Z1、Z2和Z3又是一無源RLC網(wǎng)絡(luò),通過改變I1的頻率再重復(fù)上面的六步測(cè)量,總可以計(jì)算出和RLC元件的值,對(duì)于同種性質(zhì)的元件(如同為R或L或C)的串并聯(lián),本測(cè)試?yán)碚撝荒軐⑵渥饕粋€(gè)元件來進(jìn)行測(cè)量。

2.3.3 復(fù)雜網(wǎng)絡(luò)

對(duì)于較復(fù)雜的電路,可以從電路拓?fù)涞慕嵌葋砜紤]其測(cè)試。具體來說有兩種方法。

(1)通過對(duì)ABM開關(guān)矩陣的控制,可以將其簡化成圖2或圖3的情形。然后按照相應(yīng)的測(cè)試方法分別進(jìn)行測(cè)量。

??? (2)單端口網(wǎng)絡(luò)測(cè)量法。

對(duì)于任一無源單端口網(wǎng)絡(luò)(若是多端口網(wǎng)絡(luò),可以通過對(duì)相關(guān)的ABM開關(guān)矩陣進(jìn)行控制,將其轉(zhuǎn)換成單端口網(wǎng)絡(luò)),由網(wǎng)表文件可以得其拓?fù)浣Y(jié)構(gòu)、等效支路元件的個(gè)數(shù)N(等效支路元件的定義:相同性質(zhì)的兩元件串聯(lián)或并聯(lián)將被看成一個(gè)元件,即等效支路元件),通過在兩端口間施加某一頻率的電流激勵(lì)源,再分別測(cè)量其兩端電壓,就可以得到該頻率的等效阻抗,從而得一個(gè)非線性方程。如在兩端口間施加Q(為了盡量減少測(cè)試和解非線性方程組所產(chǎn)生誤差,一般要求Q>N)個(gè)頻率不同的電流激勵(lì)源,就可以得到Q個(gè)非線性方程組。解該非線性方程組就可得這N個(gè)等效支路元件的元件值。

以上問題的實(shí)質(zhì)是,由電路網(wǎng)表得到傳輸導(dǎo)納的非線性模型,經(jīng)施加不少于Q組(不同頻率)的電流激勵(lì),分別測(cè)量其端電壓響應(yīng)。根據(jù)此數(shù)據(jù)表(即激勵(lì)響應(yīng)表)來確定模型中的各參數(shù)(即支路導(dǎo)納值),以保證傳輸導(dǎo)納的非線性模型“最佳”擬合這Q組電壓電流數(shù)據(jù)表。由此看來,這實(shí)質(zhì)是一個(gè)非線性的模型擬合問題,即非線性最小二乘問題〔4〕。

雖然計(jì)算復(fù)雜度有所提高,但這種方法可測(cè)出復(fù)雜無源網(wǎng)絡(luò)的各分立等效支路元件的參數(shù)值,且由于該系統(tǒng)使用計(jì)算機(jī),因此處理這些數(shù)據(jù)是不困難的。雖然當(dāng)互連網(wǎng)絡(luò)太大時(shí),這種方法的計(jì)算復(fù)雜度呈指數(shù)增長,但DOT4測(cè)試對(duì)象是數(shù)模混合IC及由其構(gòu)成的PCB。既然是數(shù)模混合IC,留在芯片外的就是用來完成用戶特定功能的、或是校準(zhǔn)用的、或是難于集成的。難于集成的元件隨著集成技術(shù)的提高,總可以解決,完成用戶特定功能的和校準(zhǔn)用的元器件其網(wǎng)絡(luò)拓?fù)浣Y(jié)構(gòu)一般比較簡單,這種方法完全可以勝任。

這里討論的參數(shù)測(cè)試?yán)碚摲椒ㄟ€可延伸到非線性無源元件的測(cè)量。

邊界掃描支持的測(cè)試還有CLUSTER測(cè)試、器件錯(cuò)誤裝配測(cè)試、整個(gè)掃描鏈本身結(jié)構(gòu)的基礎(chǔ)測(cè)試器件功能測(cè)試、BIST(Built-In-SelfTest)測(cè)試、INTEST測(cè)試等。限于篇幅,此處不再作具體討論。

3 實(shí)例分析

3.1 簡單互連測(cè)試結(jié)果

因目前還沒有符合DOT4的器件成品,所以使用了DOT4工作組用于混合信號(hào)邊界掃描測(cè)試的專用實(shí)驗(yàn)芯片KLIC〔5〕。KLIC實(shí)際上是個(gè)Mixed-SignalScan I/O。測(cè)試對(duì)象DEMO板設(shè)計(jì)原理是在Mixed-Signal Core電路的基礎(chǔ)上插入邊界掃描結(jié)構(gòu)即KLIC,使其構(gòu)成混合信號(hào)邊界掃描CUT。

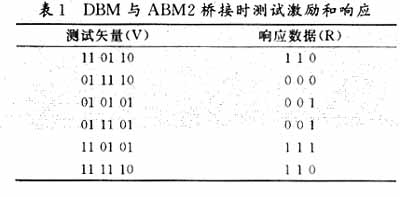

DEMO板掃描鏈中兩個(gè)邊界掃描器件之間直接的互連線有3條,分別從IC1的輸出腳DBM、ABM2、ABM3連接到IC2的輸入腳DBM、ABM2、ABM3。由KLIC的邊界掃描內(nèi)部結(jié)構(gòu)可知,其在掃描鏈上的互連測(cè)試矢量排列如下(其中,“X”為無關(guān)量,“V”對(duì)應(yīng)表1中的測(cè)試矢量欄,“R”對(duì)應(yīng)響應(yīng)數(shù)據(jù)欄):

XVV XXXXXXXXXXXX XXXX XXX XXXVVXXVVXXXXXXXXXXXXXX

與之相仿,掃描測(cè)試結(jié)果在掃描鏈上的表示為:

XXR XXXXXXXXXXXX XXXX XXX XXXXXRXXXRXXXXXXXXXXXXX

這里我們仿照WALK-1、WALK-0的全集測(cè)試矢量方法,測(cè)試時(shí),通過故障模擬開關(guān)進(jìn)行了故障設(shè)置,并且通過響應(yīng)測(cè)試碼得到了測(cè)試報(bào)告和測(cè)試分析。把DBM與ABM2橋接,本測(cè)試系統(tǒng)的測(cè)試結(jié)果如表1所示。

??? 在這里,有個(gè)問題值得注意,數(shù)字邏輯“1”與模擬VL電平進(jìn)行線與操作得到的結(jié)果是數(shù)字化值“1”,與數(shù)字邏輯“1”線與數(shù)字邏輯“0”的結(jié)果為數(shù)字邏輯“0”不同,這主要與器件的實(shí)現(xiàn)結(jié)構(gòu)以及其VH、VT和VL三種電青壯年 值及其一茁壯成長SH、SL的結(jié)構(gòu)有關(guān)。與美國Corelis公司的Scan Plus數(shù)字邊界掃描系統(tǒng)進(jìn)行了對(duì)比測(cè)試,所測(cè)結(jié)果完全一樣。

3.2 擴(kuò)展互連測(cè)試

對(duì)圖3所示的Delta網(wǎng)絡(luò),用本教研室的混合信號(hào)邊界掃描測(cè)試系統(tǒng)測(cè)得的數(shù)據(jù)如表2所示。其中,Z1為電阻,其真實(shí)值為9.734 kΩ,測(cè)量平均值為9.5367kΩ,絕對(duì)誤差為-0.1973 kΩ,相對(duì)誤差為-2.03%。Z2為電阻,其真實(shí)值為4.7 kΩ,測(cè)量平均值為4.43 kΩ,絕對(duì)誤差為-0.27 kΩ,相對(duì)誤差為5.7%。Z3為電阻,其真實(shí)值為6.85 kΩ,測(cè)量平均值為6.8888 kΩ,絕對(duì)誤差為-0.038 kΩ,相對(duì)誤差為0.56%。這里的較大誤差是由于程控信號(hào)源和數(shù)據(jù)采集板做得不完善造成的,只要將兩者加以完善,就可以達(dá)到IEEE1149.4標(biāo)準(zhǔn)規(guī)定的要求。

4 結(jié)束語

本文提出了符合1149.4標(biāo)準(zhǔn)的測(cè)試方法,并用本研究室開發(fā)的混合信號(hào)邊界掃描測(cè)試系統(tǒng)進(jìn)行了測(cè)試驗(yàn)證。測(cè)試結(jié)果表明,不但能測(cè)量互連元器件是否存在,而且還可測(cè)量其元件值(電阻、電容、電感),當(dāng)然還可擴(kuò)充到非線性元件。

混合信號(hào)測(cè)試總線是測(cè)試數(shù)字和模擬信號(hào)的起點(diǎn),但不是解決問題的全部方案。對(duì)于小電抗的分立元件,或者高頻IC,其測(cè)量就較困難。

1 IEEE std 1149.1-2001.IEEE Standard Test Access Portand Boundary-Scan Architecture.IEEE Standards Board,New York,2001

2 IEEE std 1149.4-1999.IEEE Standard for a Mixed-SignalTest Bus.IEEE Standards Board,New York,19993 K P Parker,JE Mcdermid,S Oresjo.Structure andMetrology for an Analog Testability Bus.Proc.,ITC,1993:309~322

4 謝如彪,姜培慶編著.非線性數(shù)值分析.上海:上海交通大學(xué)出版社,1984

5 http://grouper.ieee.org/1149/4/kllp.html.KLIC.JTAG Analog Extension Test Chip.IEEE P1149.4Working Group

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論