Intel Xscale PXA255嵌入式處理器與CF卡的硬件接口設計

以導航設備存儲系統應用為例,本文討論了Intel Xscale PXA255嵌入式處理器與CF卡的硬件接口設計,并以讀寫CF卡扇區的程序為例,給出了CF卡軟件編寫的技巧。該設計為基于PXA255處理器的嵌入式系統提供了擴展存儲空間的一種方法。

圖1:CF卡結構框圖

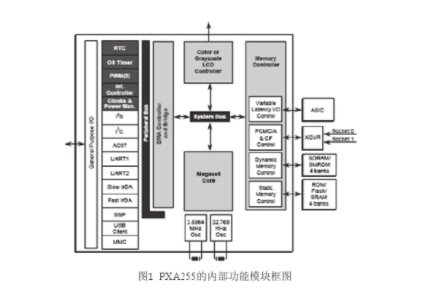

??? Intel Xscale PXA255處理器是新一代的嵌入式處理器,基于ARMv5TE體系結構的微處理器,性價比較高、功耗較低,適合于數字移動電話、個人數字助理、網絡路由器等嵌入式系統的應用。在采用PXA255處理器開發諸如車載導航系統時,電子地圖等海量地理信息數據需要一個容量大、體積小、性能優異的存儲器。“Compact Flash”卡,簡稱CF卡,具有高速度、大容量、體積小、重量輕、功耗低和高性價比等優點,十分適合嵌入式系統的應用。因此,可選擇CF卡作為地理信息數據的存儲載體。PXA255處理器提供了PCMCIA/CF卡控制器,可以方便地實現PXA255處理器與CF卡的接口設計。

CF卡結構和工作原理

??? Compact Flash技術是由CF協會(CFA)提出的一種與PC機ATA接口標準兼容的技術。如圖1,CF卡由兩個基本部分構成:內部控制器和閃存模塊。CF卡的閃存模塊基本上都使用NAND型閃存,用于存儲數據。內部控制器用來實現CF卡與主機的接口以及控制數據的傳輸。CF卡內部控制器的設計完全模擬硬盤,使用標準的ATA/IDE接口。

??? CF卡的存取方式有三種:PC Card Memory模式、PC Card I/O模式以及True IDE模式。PC Card模式與PCMCIA標準兼容。True IDE模式與ATA標準兼容。三種方式相比,在True IDE模式下,CF卡與主機通信的信號最少,硬件接口最簡單、軟件易于實現,因此本設計采用了True IDE模式。

??? CF卡扇區尋址有兩種方式:物理尋址方式(CHS)和邏輯尋址方式(LBA)。物理尋址方式使用柱面、磁頭和扇區號表示一個特定的扇區,起始扇區是0磁道、0磁頭、1扇區,接著是2扇區,一直到EOF扇區;接下來是同一柱面1頭、1扇區等。邏輯尋址方式將整個CF卡同一尋址。邏輯塊地址和物理地址的關系為:LBA地址=(柱面號×磁頭數+磁頭號)×扇區數+扇區數-1。

??? CF卡沒有機械結構,因此CF卡的扇區尋址適宜采用邏輯尋址方式。邏輯尋址方式沒有磁頭和磁道的轉換操作,因此在訪問連續扇區時,操作速度比物理尋址方式快得多。

??? 對于CF卡的操作(如:讀/寫),其實就是對CF卡控制器的寄存器進行操作。所以,必須對CF卡的寄存器十分熟悉。這些寄存器統稱為任務文件(task file)寄存器:

1.數據寄存器(讀/寫),用于CF卡的讀寫操作。主機通過該寄存器向CF卡數據緩沖寫入或從CF卡數據緩沖讀出數據。

2.錯誤寄存器(Read)和特性寄存器(Write)。讀操作時,此寄存器為錯誤寄存器,用于指明錯誤的原因;寫操作時,此寄存器為特性寄存器。

3.扇區數寄存器(讀/寫),用來記錄讀、寫扇區的數目。

4.扇區號寄存器(讀/寫),用來記錄讀、寫和校驗命令指定的起始扇區號或邏輯塊地址(LBA)的BIT7:0。

5.柱面號寄存器(讀/寫),用來記錄讀、寫、校驗和尋址命令指定的柱面號或LBA的BIT23:8。

6.驅動器/磁頭寄存器(讀/寫),記錄讀、寫、校驗和尋道命令指定的驅動器號、磁頭號或LBA的BIT27:24,其中BIT6(LBA)用來設置CF卡扇區的尋址方式(LBA=0,采用CHS模式;LBA=1,采用LBA模式)。

?????????????????? 圖2:CF卡地址空間存儲映像

7.狀態寄存器(讀)和命令寄存器(讀/寫),讀操作時,該寄存器是狀態寄存器,指示CF卡控制器執行命令后的狀態,讀狀態寄存器則返回CF卡的當前狀態;寫操作時,該寄存器是命令寄存器,接收主機發送給CF卡的控制命令。

PXA255處理器與CF卡的硬件接口設計

1. PXA255的PC Card/CF卡控制器

??? PXA255處理器PC Card/CF卡控制器可以支持一個PCMCIA卡或CF卡插槽,利用nPSKTSEL引腳可以支持第2個插槽。寄存器MECR用于向PXA255處理器的PC Card/CF卡控制器指出是否有CF卡插入,以及系統支持的CF卡的插槽數目。在有卡插入時,軟件必須將MECR的CIT比特位置1;所有的卡拔出時,則必須將之清零。

??? PXA255處理器PC Card/CF卡接口支持8、16位外圍設備,而且可以處理公共存儲器(Common Memory)、I/O和特性存儲器(Attribute Memory)三種方式的存取。每次訪問的時間取決于MCMEMx、MCATTx和MCIOx寄存器的設置。圖2給出了PXA255處理器16位PC Card/CF卡地址空間的存儲器映像。16位PC Card/CF卡存儲器映像空間分為8塊。每個插槽對應其中4塊,分別為公共存儲器、I/O、特性存儲器和保留空間。每個塊的大小為64M。

??? 每次訪問PC Card /CF卡對應的地址空間,PC Card/CF卡控制器將同時驅動信號SA_A25:0、nPREG和nPSKTSEL。(注:PXA255處理器的地址總線為SA_A25:0。)

??? 如果訪問公共存儲器和特性存儲器地址空間,PC Card/CF卡控制器驅動地址總線的時候,同時驅動nPCE1、nPCE2信號,并使用nPOE和nPWE信號作為讀寫控制信號。

??? 如果是訪問I/O空間,nPCE1、nPCE2的值取決于CF卡的信號輸出nIOIS16,而且在nIOIS16有效后,nPCE1、nPCE2將有效固定的一段時間。nIOIS16信號用來決定傳送的數據總線的寬度(8位或16位):nIOIS16=1,表明當前的數據總線為8位,nPCE1有效;nIOIS16=0表明當前的數據總線為16位,nPCE1、nPCE2同時有效。PXA255使用nPCE2向外部設備指出操作將使用數據總線的高8位,使用nPCE1向外部設備指出操作將使用數據總線的低8位。I/O地址空間的訪問使用nPIOW和nPIOR信號作為讀寫控制信號。

2. PXA255與CF卡硬件接口設計

圖3:硬件接口電路

??? 本設計僅采用一個CF卡插槽,使用Socket0的I/O地址空間,而且CF卡采用True IDE模式。則訪問地址空間為0x20000000-0x24000000時,PC Card/CF卡控制器將同時驅動信號SA_A25:0、nPREG和nPSKTSEL,并使用nPIOW和nPIOR信號作為讀寫控制信號。True IDE模式支持8位存取,也支持16位存取。

??? 在True IDE模式下,某些信號有特殊的含義,必須采用True IDE模式下特有的設置方法。如表1所示,nCE1是任務文件寄存器片選信號,低電平有效;nCE2是交替狀態(Alternate Status)寄存器和設備控制(Device Control)寄存器片選信號,也是低電平有效。因為實際操作中,極少使用交替狀態寄存器和設備控制寄存器,所以對CF卡的操作實際就是對任務文件寄存器的操作。因此,一般設置nCE1=0,nCE2=1。實現方法:在CPLD中設置nCE1=SA_A4,nCE2=not SA_A4。這樣設置是有根據的。表1是True IDE模式下I/O編碼表。主機操作CF卡時,系統僅使用地址總線A2:0,用于選擇組成任務文件寄存器的8個寄存器之一。而地址總線A10:3由主機接地。因此,nCE1=SA_A4即nCE1=0;nCE2=not SA_A4即nCE2=1。表1中,-CE1=0時,對應的8個寄存器統稱為任務文件寄存器。

??? 需要注意的是,在True IDE模式下,nOE不是讀使能信號,而是CF卡True IED模式的使能信號。CF卡上電時,若nOE(PIN9)為"0",則CF卡自動進入True IDE模式;若nOE="1"則進入PC Card 模式。當電源一直接通時,熱拔插CF卡將會使其從原來的True IDE模式重新配置成PC Card模式。因此,熱插拔過程中,為了使CF卡工作在True IDE模式,需要在CF卡加電啟動的時侯,同時將nOE信號接地。實現的方法:在CPLD中將nOE置0。True IDE模式下,nWE也不用作寫使能信號,而應該由主機將之接地。處理方法:在CPLD中將其只置為1。

??? 還有一點需要注意的是: Reset信號在True IDE 模式下低電平有效,而在其它模式下高電平有效。將Reset信號接到PXA255的系統復位信號Reset_SYS。

??? True IDE模式下,PXA255處理器與CF卡的硬件接口電路如圖3所示。

??? 在圖3中,D15:0為數據總線。RDnWR信號用來控制數據總線的方向(系統處于讀狀態時,RDnWR=1;系統處于寫狀態時,RDnWR=0)。nPSKTSEL信號用作數據總線的傳輸使能。SA_A10:0(CF_A10:0)為地址總線。在True IDE 模式下,CF卡的PSKTSEL引腳是主從(Master/Slave)選擇信號:當PSKTSEL懸空時,CF卡是Slave設備;當PSKTSEL=0時,CF卡是Master設備。設計僅采用一個CF卡插槽,所以將PSKTSEL接地。在TRUE IDE模式下,REG信號沒有用處,應該接電源VCC。IREQ是中斷請求信號。利用IREQ信號,PXA255處理器可以判斷CF卡是否處于讀寫忙狀態,對CF卡進行讀寫之前利用此引腳判斷CF卡是否空閑。nWAIT信號用于指示讀寫操作正在進行,請求處理器等待。

3. CF卡熱插拔、即插即用功能的實現

??? 在自身設計上,CF卡注重軟硬件兩方面的配合。軟硬件的協同設計可以實現CF卡熱插拔、即插即用的功能。

??? 一是硬件提供判斷條件。CF卡硬件電路提供了兩個用來檢測CF卡是否存在的引腳(nCD1和nCD2)。nCD1和nCD2的有效電平均為低電平,當主機檢測到與其相連的nCD1和nCD2引腳同時為低電平時,可判斷出CF卡與主機相連;當主機檢測到與其相連的nCD1和nCD2兩個引腳不同時為低電平,則可判斷出CF卡未與主機相連。

表1:True IDE模式I/O編碼

??? 二是軟件。首先定義全局變量(如:Cf_IsInsert),用于記錄CF卡是否與主機相連:當Cf_IsInsert為0時表示CF卡未與主機相連;當Cf_IsInsert為1時表示CF卡與主機相連。然后,在每次操作CF卡之前都先檢測CF卡的nCD1和nCD2引腳。當檢測到nCD1和nCD2引腳同時為低電平(有卡插入)且Cf_IsInsert為0時,復位CF卡,重新檢測CF卡的FAT表,統計還有多少剩余空間可以分配。檢測完畢后,置變量Cf_IsInsert為1,然后設置MECR寄存器CIT比特位。當檢測到nCD1和nCD2引腳同時為低電平,且Cf_IsInsert為1時,設置MECR寄存器CIT比特位,繼續CF卡的正常操作。當檢測到nCD1和nCD2引腳為高時(無卡插入),停止CF卡操作,清除MECR寄存器CIT比特位,置變量Cf_IsInsert為0。

讀/寫CF卡扇區程序的編寫方法

???? CF卡的讀寫是以一個扇區為基本單位的。在讀寫一個扇區之前必須先指明當前需要讀寫的柱面、頭和扇區或LBA地址,然后發送讀寫命令。一個扇區的512字節需要一次性連續讀出或者寫入。主機讀/寫CF卡上一個文件的過程是這樣的:

1.CF卡初始化。CF卡上電復位和統計剩余空間的大小。

2.CF卡內部控制器向CF卡某些寄存器填寫必要的信息。如向扇區號寄存器填寫讀寫數據的起始扇區號或LBA地址、向扇區數寄存器填寫讀寫數據所占的扇區個數、設置CF卡的扇區尋址方式等。

3.向CF卡的命令寄存器寫入操作CF卡的命令。如寫操作向CF卡的命令寄存器寫入30H,讀操作向CF卡的命令寄存器寫入20H。

4.CF卡有數據傳輸請求之后,主機讀寫CF卡的數據寄存器,從而實現從CF卡數據緩沖讀出數據或向CF卡數據緩沖寫入數據。

5.在執行以上操作的過程中,每執行一步,都應該檢測狀態寄存器,確定CF卡的當前狀態,從而確定下一步應該執行什么操作(參考狀態寄存器的BIT位的意義,編寫檢測代碼)。

本文小結

??? 前面詳細介紹了CF卡的工作原理、PXA255處理器的PC Card/CF卡控制器的特性,給出了基于PXA255處理器的嵌入式導航設備存儲系統的一種實現方案。目前,該設計已經在印刷電路板上實現,運行穩定可靠。

電子發燒友App

電子發燒友App

評論