一種實用的VXI總線接口設計

隨著計算機技術與超大規模集成電路技術的發展,對以計算機為主控機的自動測試系統的要求越來越高。在vme總線基礎上發展起來的vxi總線正適應了這種發展的要求和趨勢,它具有體積小、重量輕、速度快、電磁兼容性好、定時準確、可靠性高、軟件標準化程度高、操作靈活方便等很多優點,因此發展十分迅速。國外已大量應用并有許多商業產品問世,國內也在積極開發引進。我們在研制某新型飛機火控雷達系統的檢測設備的過程中,組建了vxi總線雷達自動檢測系統。在研制該系統過程中,我們開發了一種利用cpld和雙口ram設計的寄存器基vxi總線儀器接口電路,下面我們就這一接口電路做一介紹。

1 接口的功能

(2) 產生i/o讀寫信號和雙端口ram的片選信號eion*;

(3)產生vxi總線的數據傳輸應答信號dtack*、數據總線使能信號dben*和數據傳輸方向控制信號dir;

(4) 具有中斷請求功能。

2 電路設計

作為寄存器基的接口電路,它具有配置寄存器和相關寄存器,為a16\a24接口,執行d16功能。總線隔離電路比較簡單,可用雙向總線連接器74ls245實現,在這里不做詳細地介紹。vxi總線的接口譯碼電路利用一片xilinx公司的xc95108-pc84cpld完成,利用雙端口ram—idt7024來實現配置寄存器和器件相關寄存器。圖1為接口功能結構圖。

2.1 vxi總線接口譯碼電路

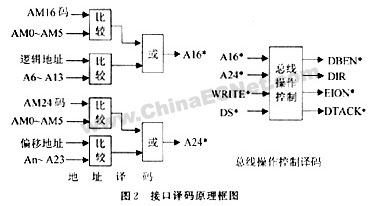

vcpld是可由用戶進行編程實現所需邏輯功能的數字集成電路,它具有高性能、高集成度、高度靈活適用等諸多優點。使用cpld,可簡化電路設計、縮小系統規模,提高電路可靠性,還能縮短開發周期。xc95108-pc84cpld是xilinx公司的第三代產品 ,它由快速連接開關矩陣連接的6個完全相同的功能模塊組成,具有108個宏單元,集成了2400個可用邏輯門,傳播延時為5 ns,用它編程信息不易丟失,可電擦除。圖2為接口譯碼原理框圖,該接口分為地址譯碼、總線操作控制譯碼兩部分,其中地址譯碼又分為a16地址選通和a24地址選通兩部分。它們都集成在一片xc95108-pc84cpld里。

vxi總線選擇使用16、24或32位3種地址接口,不同的地址范圍是短地址16位,標準地址24位以及擴展地址32位。地址寬度由地址修改碼am0~am5決定,本接口選用短地址和標準地址。短地址使用地址線a01~a15,地址修改碼為29h或2dh;標準地址使用地址線a01~a23,地址修改碼為39h、3ah、3dh、3eh。作為寄存器基的接口,數據傳輸操作過程如下:在iack*為高時,主模塊用地址選通線as*下降沿通知接口可獲取地址信息。當尋址到本接口時,則打開數據通道,并在數據選通線ds1*或ds0*的下降沿,根據讀寫信號線write*的狀態,進行數據的讀或寫;并且通過數據傳輸應答線dtack*為低有效作為應答信號。

作為a16\a24接口,它必須完成a16\a24接口的尋址要求。它包括vxi總線a16寄存器和a24寄存器尋址電路、vxi總線a16寄存器和a24寄存器、vxi總線a16\a24總線操作控制電路。在電路中,當am16碼符合a16器件的地址修改碼的要求并且邏輯地址與本器件的八位邏輯地址開關相符時,選中本接口為a16接口。當am24碼符合a24接口的地址修改碼的要求并且偏移地址也與本接口的偏移地址相符時,選中本接口為a24接口。

接口中a16選通信號a16*(上標*表示低電平有效)有效的條件是:

a16*=(not a15) or (not a14) or (a13 xor q7) or (a12 xor q6) or

(a11 xor q5) or (a10 xor q4) or (a9 xor q3) or (a8 xor q2)

or (a7 xor q1) or (a6 xor q0) or (not am0) or am1 or (not am3)

or am4 or am5 or (not iack*) or (not lword*)

其中q7~q0表示八位邏輯地址的狀態。

接口 中a24選通信號a24*有效的條件是:

a24*=(a23 xor b15) or (a22 xor b14) or … or (an xor bn-8)

其中b15~bn-8表示偏移地址的狀態。

總線操作控制電路隨時監視寄存器選通信號a16*,a24*和數據選通信號ds0*~ds1*,產生數據總線使能信號dben*、數據傳輸方向控制信號dir和總線數據傳輸應答信號dtack*。這些信號的譯碼方程為:

ds*=ds1 and ds0

eion*=(a16* or ds*) and (a24 or ds*)

dir=eion* or (not write*)

dtack*=eion*

這些邏輯表達式都很容易在cpld里實現。a16器件寄存器和a24寄存器均采用雙端口ram—idt7024來實現。雙端口ram的一邊接入vxi總線,另一邊則掛到本地cpu上,如此本地cpu就可通過這些寄存器與系統中的其他器件進行數據交換。

2.2 雙端口ram電路

雙端口ram—idt7024有兩套獨立的地址線、數據線、讀寫線、忙線和片選線,分別面向vxi總線及本地cpu,ram則是一套,有4 k×16個存儲單元。它允許2套同時讀寫不同的ram單元和同時讀同一ram單元;在其他情況下訪問同一ram單元時,將會引起沖突,無效的一方以忙線busy*為低,通知本方這次讀寫無效。對于面向vxi總線部分,采用a16寄存器的地址線a01~a05和a24寄存器的地址線a01~an-1在經過其相應的選通信號a16*和a24*使能的鎖存器后,并接到雙端口ram的地址線上。這樣可保證同一雙端口ram可既可作為a16寄存器,又可作為a24寄存器;但是最低的64個字節的寄存器地址是相同的,應分配給a16寄存器,高于此64字節的寄存器都可作為a24寄存器 。配置寄存器的內容由本地cpu上電初始化程序一次寫入,供vxi總線讀取。為了解決ram的沖突問題,面向本地cpu的忙線為cpu外部最高級中斷源,一旦發生沖突,將通過中斷服務設置標志,通知本地cpu重新讀寫。

器件具有64個字節的a16器件寄存器,按地址從低到高可分為2類:器件配置寄存器和器件相關寄存器。配置寄存器共4個,分別是識別/邏輯地址寄存器,器件類型寄存器,狀態/控制寄存器和偏移寄存器。讀出這些寄存器可了解器件的基本配置情況和狀態,向這些寄存器寫入可完成對器件的基本控制功能。器件在a24地址空間還有k字節的相關寄存器,相關寄存器的用法由用戶自己定義。所有這些寄存器均由雙端口ram來實現。接入總線需要有數據線d0~d15,片選線eion*及讀寫信號線write*。采用雙向緩沖器將器件板上的數據總線和vxi背板上的數據總線隔開,用數據傳輸方向控制信號dir控制雙向緩沖器的方向,用總線操作控制電路產生的一個數據總線使能信號dben*來使能該雙向緩沖器,使它在有別的器件對本器件進行讀寫操作時才打開而在其他時候關閉。

3 結論

采用cpld和雙端口ram后使vxi總線接口電路得到了極大的簡化,且a24寄存器的大小可由需要增加雙端口ram的片數而定,可以實現在系統編程進行修改,具有很大的靈活性。該接口經實用證明,性能可靠,使用方便,具有良好的通用性。

電子發燒友App

電子發燒友App

評論