C8051F310設(shè)計的UART擴(kuò)展實現(xiàn)

UART數(shù)據(jù)發(fā)送協(xié)議作為一種簡單的數(shù)據(jù)發(fā)送協(xié)議,被大量的使用在當(dāng)前各種數(shù)字外設(shè)的數(shù)據(jù)傳輸上。但是現(xiàn)在的PC機(jī)存在無UART接口或接口較少的問題,當(dāng)需要利用PC機(jī)對于多個數(shù)字設(shè)備同時處理問題時,就需要在PC機(jī)上進(jìn)行UART擴(kuò)展,這類問題在筆記本PC上尤為突出。

通常這種問題的解決方法有以下幾種方法:

(1)利用USB接口通過相應(yīng)的轉(zhuǎn)換設(shè)備進(jìn)行轉(zhuǎn)換。

(2)利用PCI總線轉(zhuǎn)換卡獲得多個UART接口的擴(kuò)展。前者優(yōu)點在于實現(xiàn)簡單設(shè)備,成本低。后者優(yōu)點在于可以實現(xiàn)多個接口擴(kuò)展且功能完善。但在實際使用中發(fā)現(xiàn)兩者都存在一個共同的問題,即利用擴(kuò)展獲得UART接口其工作性能不夠穩(wěn)定,且存在不能完全實現(xiàn)多個UART接口的實時通訊。

為解決上述硬件方法在工程實現(xiàn)存在的不足,本文針對項目實際需要提出了一種利用C8051F310單片機(jī)實現(xiàn)多UART接口擴(kuò)展方法。通過單片機(jī)作為數(shù)據(jù)收發(fā)的中繼器,實現(xiàn)對于多個UART采集的需要。

UART數(shù)據(jù)發(fā)送

8位UART數(shù)據(jù)傳輸主要利用RX,TX信號線實現(xiàn)數(shù)據(jù)的雙向傳輸(如圖1)。

當(dāng)數(shù)據(jù)接收時,數(shù)據(jù)線RX首先處于接收準(zhǔn)備狀態(tài)即RX呈高電平,根據(jù)UART數(shù)據(jù)發(fā)送協(xié)議,如果RX線有數(shù)據(jù)接收時,RX線被置為低電平,接收起始位,在起始位后是為數(shù)據(jù)位,當(dāng)最后一幀數(shù)據(jù)接收完畢后,產(chǎn)生終止,終止位的作用為將RX線電平置高,是RX線處于等待狀態(tài)。

發(fā)送通過對于TX線上信號電平的操作實現(xiàn)對于數(shù)據(jù)的發(fā)送,發(fā)送初始狀態(tài)下TX線處于高電平,當(dāng)啟動發(fā)送后將TX線電平置低產(chǎn)生起始位,在一個波特率時鐘周期后將開始發(fā)送數(shù)據(jù),數(shù)據(jù)發(fā)送完畢后重新將TX電平置高使發(fā)送機(jī)處于等待狀態(tài)。

單個UART實現(xiàn)方法

本文利用C8051F310單片機(jī)作為軟件UART實現(xiàn)的平臺,主要方法是通過單片機(jī)的定時器產(chǎn)生波特率,根據(jù)波特率確定的位時間定時讀取(或發(fā)送)位數(shù)據(jù)信號,從而模擬了硬件UART的工作過程。具體的實現(xiàn)方法如下所述。

(1)硬件連接

在UART的軟件實現(xiàn)中主要是利用單片機(jī)模擬硬件UART的發(fā)送過程,因此我們利用C8051F310單片機(jī)中定時器T0工作的雙八位定時模式用于產(chǎn)生波特率,PC機(jī)A0工作在邊沿捕捉狀態(tài)以捕捉SW_RX端口的電平變化產(chǎn)生,判斷數(shù)據(jù)接收的初始和終止。具體的硬件連接如圖2。

(2)軟件實現(xiàn)

發(fā)送狀態(tài)機(jī)軟件實現(xiàn):將數(shù)據(jù)進(jìn)入到發(fā)送緩沖寄存器,然后置SW_TX端口為低電平,啟動發(fā)送,裝載波特率源,此后每經(jīng)過1/2個位時間后通過移位操作將發(fā)送緩沖寄存器中的數(shù)據(jù)按位改變SW_TX數(shù)據(jù)線電平從而實現(xiàn)數(shù)據(jù)的發(fā)送。

接收狀態(tài)機(jī)軟件實現(xiàn):當(dāng)PCA0模塊捕捉到SW_RX下邊沿后為產(chǎn)生中斷,捕捉接收起始位,然后轉(zhuǎn)載波特率,此后每1/2個位時間讀取SW_RX線數(shù)據(jù)位,通過移位操作進(jìn)入接收緩存。在第九位是由PCA0捕捉停止位,完成接收。

多個UART的擴(kuò)展實現(xiàn)

由于軟件UART主要利用中斷來控制接收和發(fā)送的,因此,當(dāng)進(jìn)行多個UART擴(kuò)展是不可避免的遇到了由于中斷處理時間對于UART上發(fā)送數(shù)據(jù)和接收數(shù)據(jù)的位時間對準(zhǔn)問題。根據(jù)UART傳輸原理為了保證接收的準(zhǔn)確性一般采用在1/2個位時間處讀取和發(fā)送數(shù)據(jù)。因此無論進(jìn)行多少個UART擴(kuò)展其總的時間開銷應(yīng)小于1/2個位時間,因此當(dāng)配置多個UART擴(kuò)展時傳輸?shù)牟ㄌ芈适怯邢拗频摹M瑫r為了盡可能的多擴(kuò)展UART應(yīng)當(dāng)盡量采用較高的系統(tǒng)時鐘頻率。

在本設(shè)計中利用C8051F310實現(xiàn)了4路UART擴(kuò)展。分別利用定時器T0,定時器T2,定時器T3和PCA定時器作為波特率產(chǎn)生定時器。設(shè)定波特率為9600b/s。

考慮中斷處理時間,前文提到了總的中斷處理時間應(yīng)小于1/2個位時間,考慮了最差情況,即4路中斷同時并發(fā)的情況,一般而言此種情況是不常發(fā)生的,因此,認(rèn)為只要滿足下式:

即可滿足n個UART擴(kuò)展的要求,其中為平均中斷處理時間。

對于中斷時間的測定,可采用在中斷開始和中斷結(jié)束處設(shè)置斷點讀取定時器計數(shù)值方式獲得。

由此可以看出能否盡量多的擴(kuò)展一定波特率要求的UART,主要是控制中斷處理的時間采用盡量少的中斷處理完成讀取和發(fā)送的I/O端口控制,以及相應(yīng)的移位操作,一般接收狀態(tài)機(jī)中中斷時間較長,而中斷發(fā)送機(jī)時間較短。

多串口數(shù)據(jù)轉(zhuǎn)發(fā)協(xié)議

本設(shè)計中實現(xiàn)多串口軟件擴(kuò)展的目的是為了解決端口不足的問題,利用一個串口實現(xiàn)對于多個UART設(shè)備的通訊,同時克服硬件擴(kuò)展中信道占用問題,因此需要編制數(shù)據(jù)中繼轉(zhuǎn)發(fā)協(xié)議。

下行數(shù)據(jù)的讀取

UART設(shè)備的數(shù)據(jù)發(fā)送可以分為兩類:分為主從式和直發(fā)式,主從式數(shù)據(jù)的獲取需要先向設(shè)備發(fā)送指令,通過指令獲取相應(yīng)設(shè)備數(shù)據(jù)。直發(fā)式設(shè)備則無論處于何種狀態(tài),系統(tǒng)加電后按照預(yù)定數(shù)據(jù)協(xié)議向上發(fā)送數(shù)據(jù)。在本設(shè)計中同時存在這兩類設(shè)備。

對于直發(fā)式設(shè)備本設(shè)計采用直接利用一路軟件UART獲取數(shù)據(jù),將數(shù)據(jù)保存在單片機(jī)預(yù)先開辟好的一組存儲區(qū)域中,對于主從式設(shè)備本設(shè)計采用由單片機(jī)按照其最小工作周期連續(xù)采集數(shù)據(jù)進(jìn)行存儲的方式(即利用單片保持?jǐn)?shù)據(jù)的最小采集周期更新)。

采集的時序安排,由于下掛的各種設(shè)備數(shù)據(jù)采集周期不同,因此不可避免的存在各種數(shù)據(jù)采集的時序問題,由于采用中斷方式進(jìn)行采集,這種時序的安排體現(xiàn)在了中斷的優(yōu)先級安排上。為了最大限度的保持?jǐn)?shù)據(jù)采集的實時性,應(yīng)將數(shù)據(jù)周期較長的設(shè)備設(shè)定為高優(yōu)先級中斷,這樣在其設(shè)備采集設(shè)備的同時可以更新其他低速設(shè)備。

上行數(shù)據(jù)的轉(zhuǎn)發(fā)

上行數(shù)據(jù)轉(zhuǎn)發(fā)采用指令方式,即利用指令判斷從數(shù)據(jù)存儲區(qū)中獲取那些設(shè)備的數(shù)據(jù)。通過這種方式把原來兩類設(shè)備數(shù)據(jù)傳輸方式統(tǒng)一到了主從式上。上行器件命令的發(fā)送

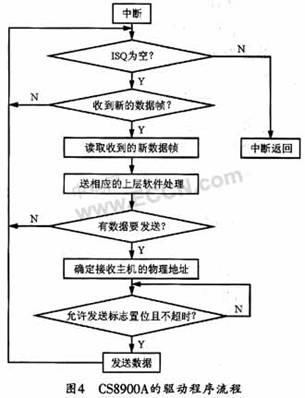

主要采用協(xié)議地址的方式判明指令針對的設(shè)備,需要在單片機(jī)中對于指令按照預(yù)先編制的指令協(xié)議進(jìn)行指令的解析,形成針對各自設(shè)備的指令碼向下轉(zhuǎn)發(fā)。具體的數(shù)據(jù)協(xié)議控制圖見圖3,多串口硬件見圖4。

實驗

(1)為了驗證單個軟件UART可用首先利用串口調(diào)試助手隨機(jī)發(fā)送數(shù)據(jù),選擇不同的自動發(fā)送周期,每個發(fā)送周期連續(xù)1000字節(jié)數(shù)據(jù)發(fā)送檢驗數(shù)據(jù)接收和發(fā)送錯誤率,實驗結(jié)果見表1。

通過以上數(shù)據(jù)我們可以看到軟件UART在發(fā)送和接收時間上存在延遲,因為利用中斷和單片機(jī)對于數(shù)據(jù)的轉(zhuǎn)發(fā)造成了數(shù)據(jù)傳輸?shù)难舆t,這是不可避免的,只要保證較高的單片機(jī)時鐘頻率,這種延時可以盡量的減小。其次當(dāng)發(fā)送周期較短時,擴(kuò)展串口的錯誤較高,但是延遲到50ms發(fā)送周期后這種錯誤基本解決。因此當(dāng)傳輸周期越長,數(shù)據(jù)錯誤率越低。(2)定波特率下,4UART同時工作的測試結(jié)果見表2。

波特率上升到115200b/s時,UART傳輸出現(xiàn)大幅錯誤,基本無正常數(shù)據(jù)。

(3)接入實際設(shè)備后輸出結(jié)果,發(fā)送指令碼:0xaa,取4設(shè)備數(shù)據(jù)。

由于設(shè)備1采集周期最長達(dá)到300ms,因此其優(yōu)先級最高。且設(shè)備1一直發(fā)送數(shù)據(jù)。

實驗中發(fā)現(xiàn)由于設(shè)備1,一直向上發(fā)送數(shù)據(jù),其他端口數(shù)據(jù)無法接收,當(dāng)設(shè)備一端口被關(guān)閉后其他端口才可接收已經(jīng)發(fā)送數(shù)據(jù)。表明此前其他端口設(shè)備數(shù)據(jù)被暫時保存在了硬件的緩存當(dāng)中。

結(jié)語

通過實驗表明在特定波特率條件下利用單片機(jī)實現(xiàn)的UART端口可以具有較好的穩(wěn)定性,且延遲時間可以被接收,同時利用協(xié)議方式可以有效地避免硬件擴(kuò)展串口存在的信道堵塞問題。對于一般PC擴(kuò)展而言是一種很好的選擇。但同時可以看到這種方法在通用性上同硬件擴(kuò)展有很大差距,必須根據(jù)特定設(shè)備編寫特定協(xié)議,并且利用編程模擬的UART接口對于波特率和數(shù)據(jù)傳輸時間上具有很高的要求,因此對于實時性要求較高的場合并不使用。

參考文獻(xiàn):

[1] 龔建偉. VC串口通訊與工程實踐[M]. 電子工業(yè)出版社, 2005

[2] AN015 UART應(yīng)用筆記.

[3] C8051F310技術(shù)手冊

[4] 蘇漪,譚潭. FPGA與DSP接口(UART)的設(shè)計實現(xiàn)與驗證[J]. 無線電工程,2009(10)

[5] 鄭寶華,程德福. 基于FPGA的UART模塊設(shè)計與實現(xiàn)[J]. 吉林化工學(xué)院學(xué)報,2009(4)

[6] TI. OMAP1611/12 Multimedia Processor Datasheet[S]. 2003(11):110-115

電子發(fā)燒友App

電子發(fā)燒友App

評論