嵌入式Internet是隨著嵌入式系統(tǒng)的廣泛應(yīng)用和計(jì)算機(jī)網(wǎng)絡(luò)技術(shù)的發(fā)展而產(chǎn)生的一種新概念和技術(shù),嵌入式系統(tǒng)以應(yīng)用為中心,以計(jì)算機(jī)技術(shù)為基礎(chǔ),且軟硬件可裁剪,現(xiàn)已贏得了巨大的市場(chǎng)。隨著Internet的發(fā)展,各種設(shè)備都產(chǎn)生了連接性的需求,從冰箱到電表,似乎所有電器需要連入互聯(lián)網(wǎng)。通過(guò)為現(xiàn)有嵌入式系統(tǒng)增加因特網(wǎng)接入能力來(lái)擴(kuò)展其功能,以Internet為介質(zhì)實(shí)現(xiàn)信息交互,從而產(chǎn)生了嵌入式Internet技術(shù),要實(shí)現(xiàn)嵌入式設(shè)備的網(wǎng)絡(luò)化,需要實(shí)現(xiàn)TCP/IP網(wǎng)絡(luò)協(xié)議棧,但由于Internet上各種通信協(xié)議對(duì)計(jì)算機(jī)存儲(chǔ)器、運(yùn)算速度等的要求比較高,使得嵌入式系統(tǒng)協(xié)議棧的開(kāi)發(fā)實(shí)現(xiàn)并不順利。

目前過(guò)兩個(gè)關(guān)鍵因素影響網(wǎng)絡(luò)協(xié)議棧的開(kāi)發(fā),一是性能和效率,二是開(kāi)發(fā)調(diào)試方便。傳統(tǒng)的操作系統(tǒng)一般只能顧及其中的一個(gè)方面。例如在Linux、FreeBSD中,網(wǎng)絡(luò)協(xié)議棧作為系統(tǒng)內(nèi)核的一部分實(shí)現(xiàn),通常具有較高的通信效率,但是不方便用戶添加實(shí)現(xiàn)新的用戶協(xié)議及根據(jù)特殊需要對(duì)協(xié)議的實(shí)現(xiàn)細(xì)節(jié)調(diào)整,同時(shí)對(duì)協(xié)議代碼的維護(hù)、調(diào)試和開(kāi)發(fā)也不方便,這個(gè)缺點(diǎn)在嵌入式領(lǐng)域表現(xiàn)的尤為突出。

由于嵌入式設(shè)備的多樣性和通信需求的多樣性,嵌入式領(lǐng)域的網(wǎng)絡(luò)協(xié)議棧的復(fù)用率非常低。本文將構(gòu)件技術(shù)引入網(wǎng)絡(luò)協(xié)議棧的開(kāi)發(fā),并在國(guó)產(chǎn)和欣操作系統(tǒng)上實(shí)現(xiàn)了一個(gè)構(gòu)件化的網(wǎng)絡(luò)協(xié)議棧,很好地解決了開(kāi)發(fā)與效率的問(wèn)題。

1 和欣嵌入式操作系統(tǒng)的CAR構(gòu)件技術(shù)

1.1 和欣嵌入式操作系統(tǒng)

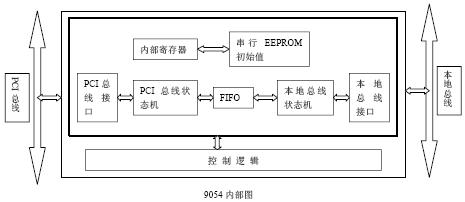

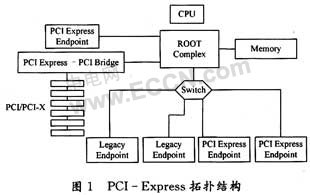

和欣操作系統(tǒng)基于微內(nèi)核,服務(wù)動(dòng)態(tài)加載。內(nèi)核包括硬件驅(qū)動(dòng)(串口、USB、以太網(wǎng)卡、無(wú)線通信模塊)、內(nèi)存管理等系統(tǒng)基本服務(wù),如圖1所示。TCP/IP協(xié)議棧完全由構(gòu)件實(shí)現(xiàn),是運(yùn)行在構(gòu)件平臺(tái)之上的一個(gè)服務(wù)構(gòu)件,底層網(wǎng)卡、串口等設(shè)備得到數(shù)據(jù)之后將數(shù)據(jù)交上層服務(wù)構(gòu)件處理。

和欣嵌入式操作系統(tǒng)是基于構(gòu)件化軟件模型,構(gòu)件化軟件設(shè)計(jì)思想貫穿了整個(gè)系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn),系統(tǒng)實(shí)現(xiàn)本身就是構(gòu)件模式,除內(nèi)核中最底層控制部分外,所有系統(tǒng)功能都以構(gòu)件接口形式提供。另外,操作系統(tǒng)對(duì)構(gòu)件化軟件模型提供了必要的運(yùn)行環(huán)境,來(lái)源不同的構(gòu)件可以在該環(huán)境上實(shí)現(xiàn)互操作,系統(tǒng)提供了構(gòu)件自動(dòng)尋址/自動(dòng)加載機(jī)制,用戶不必知道調(diào)用的構(gòu)件程序是本地的還是來(lái)自于網(wǎng)上,即構(gòu)件運(yùn)行環(huán)境對(duì)用戶透明。構(gòu)件化系統(tǒng)的實(shí)現(xiàn),使得操作系統(tǒng)本身具有高度的靈活性和擴(kuò)展性。和欣采用了CAR構(gòu)件技術(shù)。

1.2 CAR構(gòu)件技術(shù)

CAR構(gòu)件技術(shù)是在總結(jié)面向?qū)ο?a target="_blank">編程、面向構(gòu)件編程技術(shù)的發(fā)展歷史和經(jīng)驗(yàn)的基礎(chǔ)上,為更好地支持面向以Web服務(wù)為代表的下一帶網(wǎng)絡(luò)應(yīng)用軟件開(kāi)發(fā)而發(fā)明的。CAR(Component Assembly Runtime)構(gòu)件技術(shù)定義了一套網(wǎng)絡(luò)編程時(shí)代的構(gòu)件編程模型和編程規(guī)范,它規(guī)定了一組構(gòu)件間相互調(diào)用的標(biāo)準(zhǔn),使二進(jìn)制構(gòu)件可自描述并能夠在運(yùn)行時(shí)動(dòng)態(tài)鏈接。

CAR構(gòu)件技術(shù)通過(guò)二進(jìn)制的封裝及動(dòng)態(tài)鏈接技術(shù)解決軟件的動(dòng)態(tài)升級(jí)和軟件的動(dòng)態(tài)替換問(wèn)題,面向構(gòu)件技術(shù)對(duì)一組類的組合進(jìn)行封裝,并代表完成一個(gè)或多個(gè)功能的特定服務(wù),同時(shí)為用戶提供多個(gè)接口。整個(gè)構(gòu)件隱藏了具體的實(shí)現(xiàn),只用接口提供服務(wù)。這樣,在不同層次上,構(gòu)件均可以將底層多個(gè)邏輯組合成高層次上粒度更大的新構(gòu)件,構(gòu)件之間通過(guò)約定的接口進(jìn)行數(shù)據(jù)交換和信息傳遞,構(gòu)件的位置相互透明,可以在同一個(gè)或不同的用戶進(jìn)程空間、不同的機(jī)器設(shè)置不同的構(gòu)件上用不同的語(yǔ)言編寫,只要其符合事先約定的構(gòu)件規(guī)范。

2 和欣操作系統(tǒng)上的TCP/IP協(xié)議棧的特點(diǎn)與實(shí)現(xiàn)

2.1 和欣嵌入式操作系統(tǒng)上TCP/IP協(xié)議棧的特點(diǎn)

由于嵌入式系統(tǒng)在硬件資源的占有量以及處理器的處理能力等方面的限制,使得TCP/IP協(xié)議的嵌入式實(shí)現(xiàn)與其在通用操作系統(tǒng)中的實(shí)現(xiàn)有很大不同。首先,由于嵌入式處理器的時(shí)鐘頻率低,地址、數(shù)據(jù)總線窄,導(dǎo)致嵌入式系統(tǒng)對(duì)一個(gè)通用IP包的處理要花費(fèi)更多的處理機(jī)時(shí)間,從而影響其他任務(wù)的執(zhí)行,因此需要對(duì)龐大的復(fù)雜的TCP/IP協(xié)議棧進(jìn)行裁剪,使之具有簡(jiǎn)單、高效的特點(diǎn)同時(shí)在設(shè)計(jì)嵌入式TCP/IP協(xié)議棧時(shí)要合理控制中斷處理程序的大小,使得中斷處理程序的運(yùn)行時(shí)候盡可能短;同時(shí)把那些無(wú)實(shí)時(shí)性要求和費(fèi)時(shí)的工作移到主程序中執(zhí)行,從而保證協(xié)議的正確執(zhí)行,具體來(lái)說(shuō),就是把TCP/IP協(xié)議的處理工作放到主程序中對(duì)網(wǎng)絡(luò)接口的控制芯片采用循環(huán)查詢方式,在其他中斷任務(wù)的執(zhí)行間隙處理TCP/IP協(xié)議,以犧牲系統(tǒng)的響應(yīng)時(shí)間換取系統(tǒng)的可靠性,再者由于嵌入式的系統(tǒng)的存儲(chǔ)空間有限,一般情況下只能開(kāi)辟幾KB字節(jié)的緩存區(qū)接收數(shù)據(jù)包,并且其存儲(chǔ)空間固定,不是動(dòng)態(tài)分配的。因此,遇到大數(shù)據(jù)包時(shí)就會(huì)出現(xiàn)緩沖區(qū)溢出的錯(cuò)誤。通常,嵌入式系統(tǒng)接收的數(shù)據(jù)包類型僅為系統(tǒng)狀態(tài)配置包、控制動(dòng)作命令包、通信控制包等,這些包容量較小,由實(shí)時(shí)數(shù)據(jù)或網(wǎng)頁(yè)向網(wǎng)絡(luò)發(fā)送的數(shù)據(jù)包比較長(zhǎng),但可以通過(guò)設(shè)計(jì)格式加以控制。

和欣操作系統(tǒng)是基于微內(nèi)核的操作系統(tǒng), 其上的TCP/IP協(xié)議棧既可以運(yùn)行在用戶態(tài),也可以運(yùn)行在內(nèi)核態(tài)度,具有通用接口和方便的框架,方便用戶開(kāi)發(fā)適合自己領(lǐng)域或特殊需要的網(wǎng)絡(luò)協(xié)議棧,因?yàn)楹托啦僮飨到y(tǒng)提供了高效的進(jìn)程上下文切換功能和進(jìn)程間通信,所以整個(gè)網(wǎng)絡(luò)協(xié)議棧作為一個(gè)用戶態(tài)進(jìn)程提供服務(wù)。使用前先創(chuàng)建網(wǎng)絡(luò)構(gòu)件實(shí)例,然后向操作系統(tǒng)注冊(cè)服務(wù)。此后用戶就可以使用網(wǎng)絡(luò)編程接口了,如果用戶對(duì)網(wǎng)絡(luò)協(xié)議棧有更高的效率要求,則可以將該協(xié)議棧加載到內(nèi)核態(tài)。

2.2 和欣嵌入式操作系統(tǒng)TCP/IP的實(shí)現(xiàn)

根據(jù)和欣嵌入式TCP/IP協(xié)議堆棧的特點(diǎn),在實(shí)現(xiàn)嵌入式TCP/IP協(xié)議棧時(shí)只需要用到下述四個(gè)基本協(xié)議:TCP協(xié)議、ICMP協(xié)議、IP協(xié)議、ARP協(xié)議。其余的鏈路層協(xié)議如PPP協(xié)議需要在嵌入式TCP/IP協(xié)議棧下面的設(shè)備驅(qū)動(dòng)程序中實(shí)現(xiàn);而像HTTP、FTP這樣的應(yīng)用層協(xié)議則要在嵌入式TCP/IP協(xié)議棧上面的應(yīng)用層中實(shí)現(xiàn)。

2.2.1 地址轉(zhuǎn)化協(xié)議ARP

ARP協(xié)議為IP地址和以太網(wǎng)MAC地址建立一個(gè)映射表。這個(gè)協(xié)議對(duì)于以太網(wǎng)的TCP/IP協(xié)議的操作是必不可少的。為了節(jié)省空間,一個(gè)IP地址的ARP請(qǐng)求覆蓋即將發(fā)送的數(shù)據(jù)包,該ARP請(qǐng)求就是因?yàn)橐l(fā)送這個(gè)包而發(fā)送的。這種方法在假設(shè)上層會(huì)重發(fā)被覆蓋的數(shù)據(jù)時(shí)采用。每隔十秒鐘,表就會(huì)刷新一次,舊的記錄被丟棄,在嵌入式TCP/IP協(xié)議棧中,記錄的有效時(shí)間為1秒。

2.2.2 網(wǎng)絡(luò)協(xié)議IP

在嵌入式TCP/IP中,IP協(xié)議執(zhí)行兩項(xiàng)功能:(1)封裝來(lái)自上層的TCP數(shù)據(jù)包或ICMP數(shù)據(jù)包,計(jì)算IP數(shù)據(jù)包的檢驗(yàn)和;(2)解析IP緩存中的數(shù)據(jù)包,檢查數(shù)據(jù)包的協(xié)議字段,以判斷該數(shù)據(jù)包應(yīng)該交給ICMP協(xié)議還是TCP協(xié)議處理。基于嵌入式Web服務(wù)器與客戶端通信的信息量很小,數(shù)據(jù)包的大小不會(huì)超過(guò)鏈路層的MTU(最大傳輸單元),嵌入式IP沒(méi)有引入數(shù)據(jù)包分片和重組功能,標(biāo)準(zhǔn)的IP協(xié)議有選路功能,可以選擇較短路徑傳送數(shù)據(jù)包,嵌入式IP中為了減少代碼規(guī)模,未引入選路功能。

2.2.3 網(wǎng)際控制報(bào)文協(xié)議ICMP

在嵌入式TCP/IP協(xié)議棧中,只處理一種ICMP消息類型:ICMP回送消息。ICMP回復(fù)消息經(jīng)常被用來(lái)調(diào)用ping程序測(cè)試對(duì)方主機(jī)是否在線。在嵌入式TCP/IP協(xié)議棧中,ICMP回送消息用一種十分簡(jiǎn)單的方式實(shí)現(xiàn),即將ICMP類型的字段由“echo”類型改變?yōu)椤癳cho reply”類型。改變IP首部的IP地址,將數(shù)據(jù)包送回發(fā)送者。

2.2.4 傳輸控制協(xié)議TCP

TCP協(xié)議是面向連接的、端到端的可靠通信協(xié)議。它采用了許多機(jī)制保證傳輸可靠性,應(yīng)用于嵌入式系統(tǒng)顯得過(guò)于復(fù)雜。在嵌入式TCP/IP協(xié)議棧中,為了減少存儲(chǔ)空間的占用,沒(méi)有進(jìn)入發(fā)送和接收數(shù)據(jù)的可靠窗口機(jī)制;通常,嵌入式Web服務(wù)器處于被動(dòng)服務(wù)狀態(tài),所以可以將標(biāo)準(zhǔn)TCP有線狀態(tài)機(jī)的主動(dòng)創(chuàng)建連接的SYN SENT狀態(tài)、主動(dòng)關(guān)閉連接的FIN WAIT1、FIN WAIT2、CLOSING、TIME WAIT狀態(tài)裁剪。設(shè)計(jì)中還去掉了LISTENING狀態(tài),使它在CLOSED狀態(tài)下就處于偵聽(tīng)狀態(tài),監(jiān)聽(tīng)客戶端的鏈接請(qǐng)求,這樣避免了主動(dòng)或被動(dòng)打開(kāi)及關(guān)閉的操作,使嵌入式TCP/IP協(xié)議棧更精簡(jiǎn),嵌入式TCP/IP中到達(dá)TCP段的數(shù)據(jù)不被緩存,應(yīng)用程序必須立即處理它。當(dāng)然,這并不阻止應(yīng)用層緩存數(shù)據(jù)。每次連接在發(fā)送數(shù)據(jù)時(shí),無(wú)法同時(shí)處理多于一個(gè)的TCP段,TCP協(xié)議的實(shí)現(xiàn)原理比較復(fù)雜,在嵌入式TCP/IP協(xié)議中,實(shí)現(xiàn)TCP協(xié)議是一個(gè)最關(guān)鍵的問(wèn)題。

2.2.5 構(gòu)件化的協(xié)議棧

采用構(gòu)件化方法實(shí)現(xiàn)網(wǎng)絡(luò)協(xié)議棧的關(guān)鍵是:

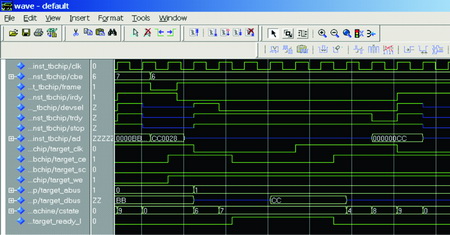

(1)如何劃分構(gòu)件的粒度。需要根據(jù)用戶的需要解決定,如果用戶是開(kāi)發(fā)一個(gè)新的協(xié)議棧,可以采用大粒度的構(gòu)件劃分方式(如圖2所示),即把整個(gè)網(wǎng)絡(luò)協(xié)議棧作為一個(gè)大的構(gòu)件,繼承預(yù)先定義的構(gòu)件。

(2)如何設(shè)計(jì)構(gòu)件接口。要實(shí)現(xiàn)(1)所提到的構(gòu)件的自由替換,必須設(shè)計(jì)良好的構(gòu)件接口。所有的構(gòu)件實(shí)現(xiàn)應(yīng)該繼承該接口。設(shè)計(jì)接口的原則是盡量保持接口的通用性和簡(jiǎn)潔性。當(dāng)有新的功能添加時(shí),可以通過(guò)繼承實(shí)現(xiàn)新的接口方便地加入原有的框架,從而實(shí)現(xiàn)軟件的無(wú)縫升級(jí)。

(3)提高網(wǎng)絡(luò)通信的效率。一個(gè)高效的通信協(xié)議需要滿足:1)上下文切換和定時(shí)器的輕型完成;2)多個(gè)協(xié)議具有統(tǒng)一的使用界面;3)在網(wǎng)絡(luò)設(shè)備,核心層和用戶層之間有高效的緩沖機(jī)制,避免不必要的拷貝。

如果操作系統(tǒng)提供了快捷的上下文切換及高效的進(jìn)程間的通信,則整個(gè)網(wǎng)絡(luò)協(xié)議棧便可以作為一個(gè)用戶態(tài)進(jìn)程對(duì)用戶進(jìn)程提供服務(wù),如果進(jìn)程上下文切換比較復(fù)雜,則整個(gè)網(wǎng)絡(luò)協(xié)議棧可以作為動(dòng)態(tài)鏈接庫(kù)鏈入用戶進(jìn)程地址空間,但需要對(duì)多進(jìn)程共享的數(shù)據(jù)加鎖,進(jìn)行同步訪問(wèn)控制。另外一種選擇是將網(wǎng)絡(luò)協(xié)議棧裝入內(nèi)核空間,也可以避免頻繁的進(jìn)程上下文切換帶來(lái)的系統(tǒng)開(kāi)銷。

因?yàn)椴捎昧送ㄓ玫腟OCKET編程接口作為最終提供給用戶使用的接口,從而使多個(gè)協(xié)議具有統(tǒng)一的使用界面。同時(shí),在采用細(xì)粒度構(gòu)件的網(wǎng)絡(luò)協(xié)議棧中,各層協(xié)議之間的接口也是精細(xì)構(gòu)造的統(tǒng)一接口,為了避免大量數(shù)據(jù)的拷貝,需要設(shè)計(jì)良好的數(shù)據(jù)結(jié)構(gòu),同時(shí)采取“共享內(nèi)存”的方法。網(wǎng)絡(luò)協(xié)議各層次間盡量以指針?lè)绞絺鬟f數(shù)據(jù)。

構(gòu)件化的網(wǎng)絡(luò)協(xié)議棧具有以下優(yōu)點(diǎn):

(1)針對(duì)不同網(wǎng)絡(luò)應(yīng)用的需求,能最大限度地利用領(lǐng)域相關(guān)知識(shí)進(jìn)行調(diào)整,提高了性能。

(2)底層構(gòu)件可以在不影響頂層使用的情況下進(jìn)行修改。

(3)方便用戶添加及開(kāi)發(fā)調(diào)試新的協(xié)議。

該文采用上海科泰公司的CAR構(gòu)件技術(shù)在和欣操作系統(tǒng)上實(shí)現(xiàn)了一個(gè)構(gòu)件化的網(wǎng)絡(luò)協(xié)議棧,該網(wǎng)絡(luò)協(xié)議構(gòu)件既可以加載在內(nèi)核態(tài),也可以加載到用戶態(tài),方便開(kāi)發(fā)調(diào)試,有利于開(kāi)發(fā)新網(wǎng)絡(luò)協(xié)議棧,其他開(kāi)發(fā)者采用構(gòu)件的方法開(kāi)發(fā)出了高效或者針對(duì)某特定領(lǐng)域的網(wǎng)絡(luò)協(xié)議棧,可以方便地替換和欣操作系統(tǒng)上原有的網(wǎng)絡(luò)協(xié)議棧。使用構(gòu)件化的方法開(kāi)發(fā)網(wǎng)絡(luò)協(xié)議棧也可以推廣到其他支持構(gòu)件的操作系統(tǒng)上。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論