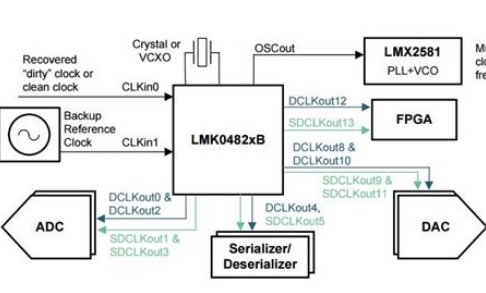

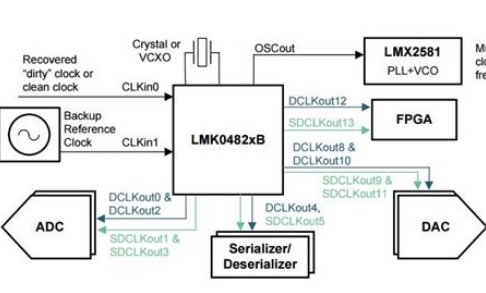

(SYSREF)模式,以及如何用它們來最大限度地提高JESD204B時鐘方案的性能。 LMK04821系列器件為該話題提供了很好的范例研究素材,因為它們是高性能的雙環路抖動清除器,可在具有器件和SYSREF時鐘的子類1時鐘方案里驅動多達七個JESD204B轉換器或邏輯器件。圖1是

2018-05-14 08:48:18 9730

9730

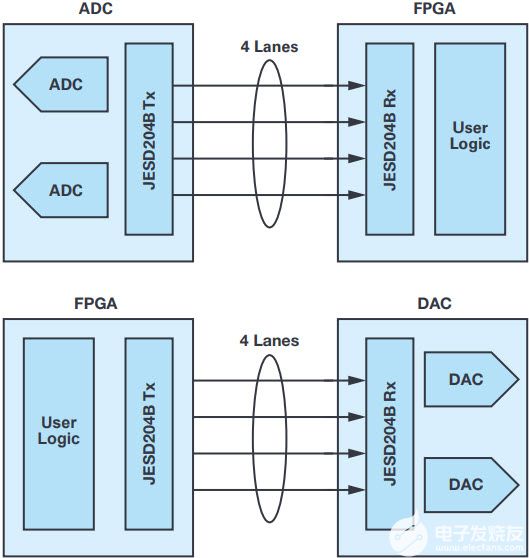

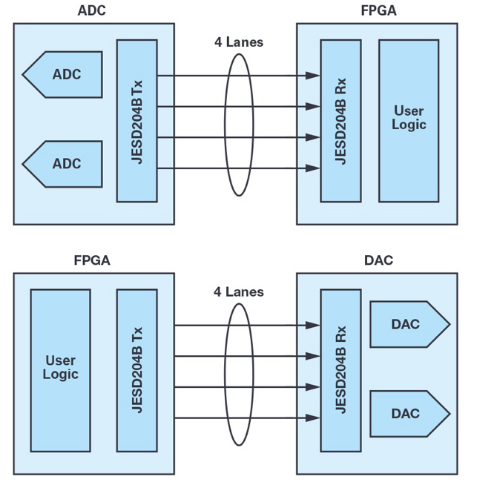

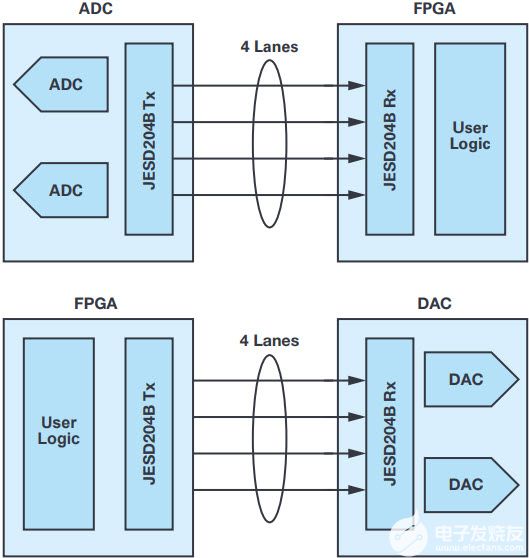

開發串行接口業界標準JESD204A/JESD204B的目的在于解決以高效省錢的方式互連最新寬帶數據轉換器與其他系統IC的問題。

2021-11-01 11:24:16 5783

5783

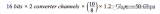

`描述采用均衡技術可以有效地補償數據轉換器的 JESD204B 高速串行接口中的信道損耗。此參考設計采用了 ADC16DX370 雙 16 位 370 MSPS 模數轉換器 (ADC),該轉換器利用

2015-05-11 10:40:44

處理模塊之間的任何延遲失配都會使性能下降。對 于交錯式處理而言,樣本對齊同樣是必需的;在交錯式處 理時,一個轉換器樣本后緊跟另一個樣本,且時間僅為一 個時鐘周期中的一小部分。JESD204B第三代高速串行

2018-10-15 10:40:45

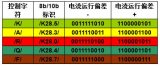

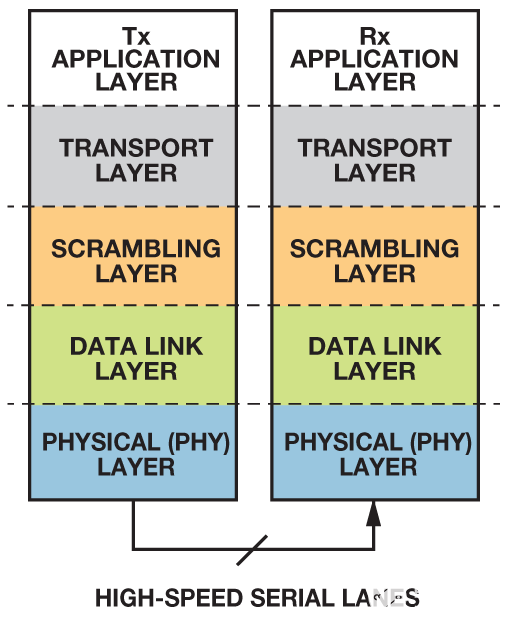

什么是8b/10b編碼,為什么JESD204B接口需使用這種編碼?怎么消除影響JESD204B鏈路傳輸的因素?JESD204B中的確定延遲到底是什么? 它是否就是轉換器的總延遲?JESD204B如何使用結束位?結束位存在的意義是什么?如何計算轉換器的通道速率?什么是應用層,它能做什么?

2021-04-13 06:39:06

摘要 隨著數模轉換器的轉換速率越來越高,JESD204B 串行接口已經越來越多地廣泛用在數模轉換器上,其對器件時鐘和同步時鐘之間的時序關系有著嚴格需求。本文就重點講解了JESD204B 數模轉換器

2019-06-19 05:00:06

在使用我們的最新模數轉換器 (ADC) 和數模轉換器 (DAC) 設計系統時,我已知道了很多有關 JESD204B 接口標準的信息,這些器件使用該協議與 FPGA 通信。此外,我還在 E2E 上的該

2022-11-21 07:02:17

在使用最新模數轉換器 (ADC) 和數模轉換器 (DAC) 設計系統時,我已知道了很多有關 JESD204B 接口標準的信息,這些器件使用該協議與 FPGA 通信。那么在解決 ADC 至 FPGA

2021-04-06 06:53:56

作者:Ken C在使用我們的最新模數轉換器 (ADC) 和數模轉換器 (DAC) 設計系統時,我已知道了很多有關 JESD204B 接口標準的信息,這些器件使用該協議與 FPGA 通信。此外,我還在

2018-09-13 14:21:49

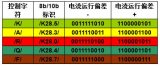

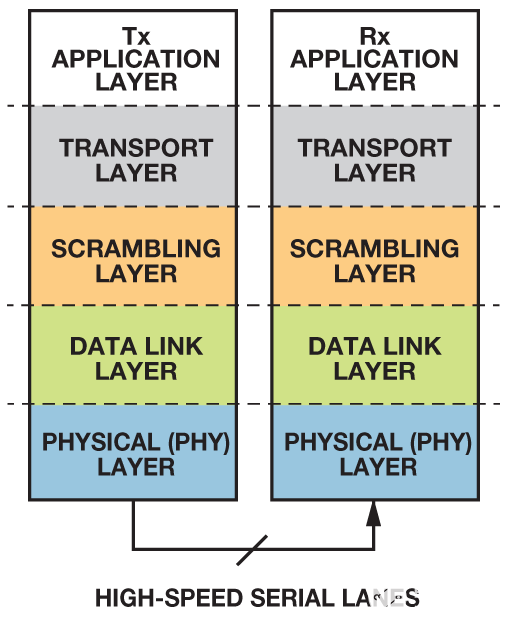

JESD204B的工作原理JESD204B的控制字符

2021-04-06 06:01:20

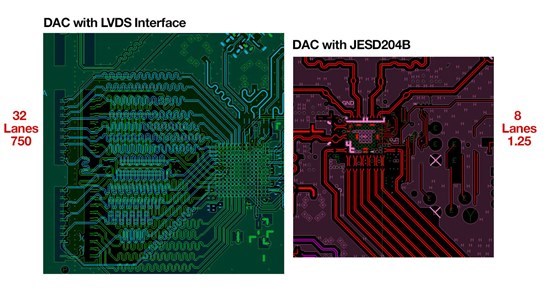

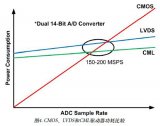

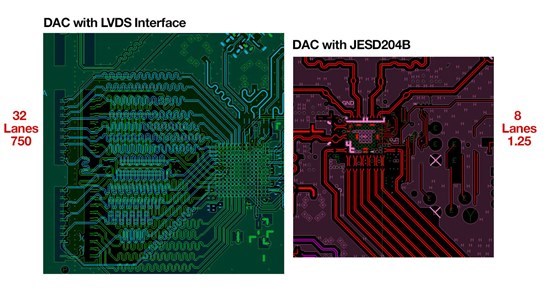

的是 JESD204B 接口將如何簡化設計流程。與 LVDS 及 CMOS 接口相比,JESD204B 數據轉換器串行接口標準可提供一些顯著的優勢,包括更簡單的布局以及更少的引腳數。因此它能獲得工程師

2022-11-23 06:35:43

的JESD204發布版中。

問:我為轉換器分配的JESD204B通道在系統板上無法順利路由至FPGA。交叉對太多,非常容易受串擾影響。能否重新映射JESD204B的通道分配,改善布局?

答:雖然轉換器

2024-01-03 06:35:04

JESD204B產品組合的更多詳情,其中包括 12 位、4GSPS ADC12J4000 模數轉換器 (ADC);16 位、雙通道、250MSPS ADS42JB69 ADC;16 位、4 通道、2.5GSPS DAC38J84 數模轉換器 (DAC) 以及 LMK04828 高性能時鐘抖動清除器。

2018-09-18 11:29:29

的時間內處理更多信息。相應地,對快速增長的高帶寬進行測試與分析便意味著需要使用速度更快、容量更大的電子測試設備。 對數據不斷增長的需求導致JEDEC固態技術協會需要引入新的 JESD204 標準,以實現

2021-01-01 07:44:26

。雖然最初的JESD204標準和修訂后的JESD204A標準在性能上都比老的接口標準要高,它們依然缺少一個關鍵因素:鏈路上串行數據的確定延遲。 該時序關系受模數轉換器的延遲影響,定義為輸入信號采樣邊沿

2019-05-29 05:00:03

支持多個轉換器下的多路、對齊的串行通道,以滿足轉換器日益增長的速度和分辨率。這種認識促成了2008年4月份JESD2004第一個修訂版的發布,即JESD204A。此修訂版增加了支持多個轉換器下的多路

2019-06-17 05:00:08

目前,我在設計中想使用ZYNQ 7015系列的FPGA,利用JESD204 IP核接收A/D轉換器AD9683轉換完成后的數據。但是JESD204 IP核的端口很多,我不知道應該如何將AD9683

2023-12-15 07:14:52

JESD204A和JESD204B參數對比如下圖所示:3、關鍵變量M:converters/device,轉換器(AD/DA)數量L:lanes/device(link),通道數量F:octets/frame

2019-12-04 10:11:26

不用再使用大量IO口,布線方便(高速串行解串器實現高吞吐量)d.多片IC同步方便JESD204A和JESD204B參數對比如下圖所示:3、關鍵變量M:converters/device,轉換器

2019-12-03 17:32:13

恩智浦半導體(NXP Semiconductors)近日宣布,其推出的支持JESD204A標準的CGV? 系列數據轉換器,與Xilinx? 高性能Virtex?-6 FPGA及低成本Spartan

2019-08-09 06:08:11

R_10002_JEDEC_JESD204A數據轉換器接口技術分析

2012-08-14 12:22:22

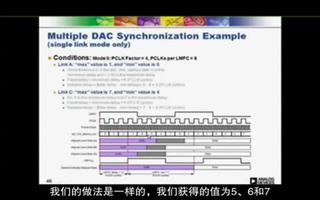

校正時序不匹配;另外一種使用通常稱為時間戳的方法。記住,這兩種方法都是AD9625設計部分的JESD204B子類1的特性。在本文中,時間戳方法將是重點,因為無需測量每個轉換器到每個FPGA的時間延遲

2018-09-03 14:48:59

了全面的產品路線圖。通過為客戶提供結合了我們先進數據轉換器技術以及集成JESD204A/B接口的產品,我們有望充分利用這項重大的接口技術突破,幫助客戶解決系統設計難題。 圖4 – JESD204具有高速串行I/O能力,解決系統PCB復雜化的挑戰。

2019-05-29 05:00:04

JESD204是什么?JESD204標準解析,為什么我們要重視它?

2021-04-13 06:14:53

JESD204B就顯得極其重要。下圖是典型的JESD204B系統的系統連接: Device Clock是器件工作的主時鐘,一般在數模轉換器里為其采樣時鐘或者整數倍頻的時鐘,其協議本身的幀和多幀的時鐘

2019-12-17 11:25:21

Haijiao Fan簡介JESD204是一種連接數據轉換器(ADC和DAC)和邏輯器件的高速串行接口,該標準的 B 修訂版支持高達 12.5 Gbps串行數據速率,并可確保 JESD204 鏈路

2018-10-16 06:02:44

描述JESD204B 鏈路是數據轉換器數字接口的最新趨勢。這些鏈路利用高速串行數字技術提供很大的益處(包括增大的信道密度)。此參考設計解決了其中一個采用新接口的挑戰:理解并設計鏈路延遲。一個示例實現

2018-11-21 16:51:43

JESD204B數模轉換器的時鐘規范是什么?JESD204B數模轉換器有哪些優勢?如何去實現JESD204B時鐘?

2021-05-18 06:06:10

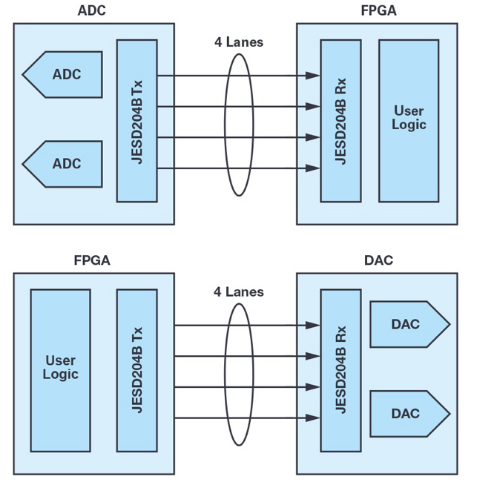

的模數轉換器(ADC)和數模轉換器(DAC)支持最新的JESD204B串行接口標準,出現了FPGA與這些模擬產品的最佳接口方式問題。FPGA一直支持千兆串行/解串(SERDES)收發器。然而在過去,大多數ADC

2021-04-06 09:46:23

LMK04821系列器件為該話題提供了很好的范例研究素材,因為它們是高性能的雙環路抖動清除器,可在具有器件和SYSREF時鐘的子類1時鐘方案里驅動多達七個JESD204B轉換器或邏輯器件。圖1是典型

2022-11-18 06:36:26

的創始成員,我們同時開發出了兼容的數據轉換器技術和工具,并推出了全面的產品路線圖。通過為客戶提供結合了我們先進數據轉換器技術以及集成JESD204A/JESD204B接口的產品,我們有望充分利用這項重大

2021-11-03 07:00:00

JESD204b接口已經在國內好幾年,但是幾乎沒有一篇文章和其實際應用相關。其實對于一個關于JESD204b接口ADC項目來講一共大致有5個部分:ADC內核,ADC的JESD接口,[color

2017-08-09 20:33:19

是高性能的雙環路抖動清除器,可在具有器件和SYSREF時鐘的子類1時鐘方案里驅動多達七個JESD204B轉換器或邏輯器件。圖1是典型JESD204B系統(以LMK04821系列器件作為時鐘解決方案)的高級

2018-09-06 15:10:52

的信號鏈頻率計劃確定 JESD204B 鏈路參數》。《轉換至 JESD204B 時您需要知道什么》(白皮書)《JESD204B:適合您嗎?》(博客文章)《高速數據轉換器中的 JESD204B 與 LVDS》(博客文章)閱讀更多 JESD204B 博客

2018-09-13 09:55:26

標準2008年4月,該標準第一版發布,稱為JESD204A。此修訂版增加了支持多個轉換器下的多路對齊串行通道的能力。此版本保留了最初版所支持的通道數據速率——即從312.5 Mbps至3.125

2018-12-25 09:27:33

in have a error in the desing block: [BD 41-967] AXI interface pin /jesd204_0/s_axis_tx

2019-04-19 13:06:30

。目前,我在設計中想使用ZYNQ 7015系列的FPGA,利用JESD204 IP核接收A/D轉換器AD9683轉換完成后的數據。但是JESD204 IP核的端口很多,我不知道應該如何將AD9683

2018-09-05 11:45:31

_0_phy_gt_i / gt0_jesd204_0_phy_gt_i / gtxe2_i:使用GTGREFCLK僅用于測試目的。這具有可用時鐘方法的最低性能,并且可能降低收發器性能。請注意,使用BUFG驅動REFCLK可能會導致GTGREFCLK的使用。

2020-08-11 10:37:54

探討如何同步多個帶JESD204B 接口的模數轉換器 (ADC) 以便確保從 ADC 采樣的數據在相位上一致。特性同步 2 個采樣頻率為 3.072GHz 的千兆采樣 ADC系統可擴展到超過 2 個

2022-09-19 07:58:07

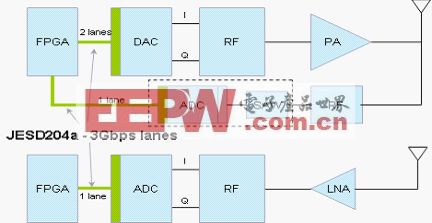

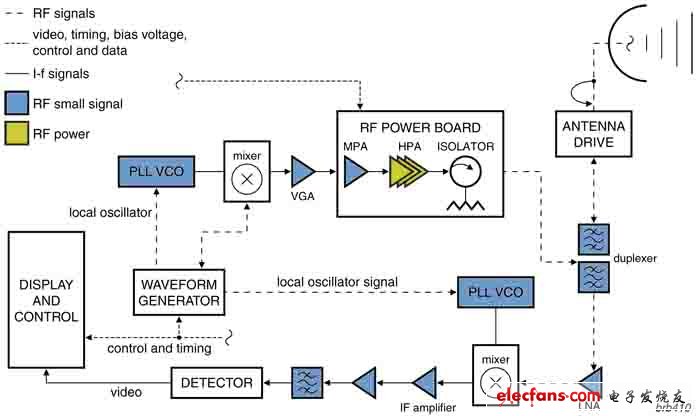

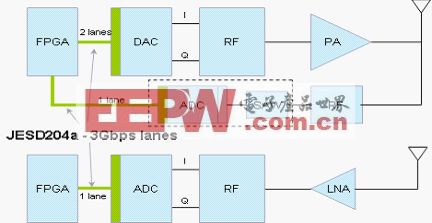

用于無線基礎設備中數據轉換器和低成本FPGA的JESD204A

引言

隨著人們訂購無線服務數量的激增、各種服務類型的多樣化,以及更低的

2010-05-27 10:18:33 689

689

- ADI 公司的 JESD204 數據轉換器產品陣容進一步擴大,14位模數轉換器能夠提高無線基礎設施和數據采集系統的信號保真度并簡化電路板布局

2010-08-03 16:03:09 851

851 Analog Devices, Inc. (ADI)推出一對支持 JESD204A 數據轉換器串行接口標準的低功耗、高速14位 ADC(模數轉換器)AD9644 和 AD9641。JESD204A 標準允許高速通信和數據采集系統的設計人員在延長傳

2010-08-06 09:29:06 916

916 DAC1408D750是一顆具有JESD204A串口的雙通道14位DAC,特性與DAC1405D750一致。創新的采用了JESD204A串口,大幅減少了數據線的數量,直接減少PCB層數,縮小面積。 另外因串口自身特性,布線設

2011-04-17 08:46:08 1058

1058

數據轉換器通常需要很少的來控制/ 狀態總線引腳來配置和監控 JEDEC JESD204A 接口的功能特性。控制和狀態寄存器接口的詳細信息被明確排除在 JEDEC 規范的范圍之外。JESD204A 的物理層定義

2011-08-04 16:22:12 56

56 IDT推出低功率雙通道16位具備JESD204B的數模轉換器,DAC165xD1G5HN是一款16位 1.5 Gsps雙通道 DAC,具備10Gbps JESD204B串行接口以及插值濾波器。

2012-11-25 22:50:28 1417

1417 JESD204 LogiCORE? IP和ADI AD9250模數高速數據轉換器之間的JESD204B實現互操作。實現邏輯和數據轉換器器件之間的JESD204B互操作性,是促進該新技術廣泛運用的一個重大里程碑。

2013-10-09 11:10:34 1956

1956 全球領先的高性能信號處理解決方案供應商ADI今天發布了一款基于FPGA的參考設計及配套軟件和HDL代碼,該參考設計可降低集成JESD204B兼容轉換器的高速系統的設計風險。該軟件為JESD204

2013-10-17 16:35:20 909

909 Altera公司今天宣布,開始提供多種JESD204B解決方案,設計用于在使用了最新JEDEC JESD204B標準的系統中簡化Altera FPGA和高速數據轉換器的集成。很多應用都使用了這一接口標準,包括雷達、無線射頻前端、醫療成像設備、軟件無線電,以及工業應用等。

2014-01-24 10:14:58 1536

1536 在使用我們的最新模數轉換器 (ADC) 和數模轉換器 (DAC) 設計系統時,我已知道了很多有關 JESD204B 接口標準的信息,這些器件使用該協議與 FPGA 通信。此外,我還在 E2E

2017-04-08 04:48:17 2131

2131

簡介 JESD204是一種連接數據轉換器(ADC和DAC)和邏輯器件的高速串行接口,該標準的 B 修訂版支持高達 12.5 Gbps串行數據速率,并可確保 JESD204 鏈路具有可重復的確定性延遲

2017-04-12 10:22:11 14645

14645

,因為它們是高性能的雙環路抖動清除器,可在具有器件和SYSREF時鐘的子類1時鐘方案里驅動多達七個JESD204B轉換器或邏輯器件。

2017-11-17 10:31:45 3009

3009

隨著轉換器分辨率和速度的提高,對于效率更高的接口的需求也隨之增長。一種新型轉換器接口——JESD204——誕生于幾年前,其作為轉換器接口經過幾次版本更新后越來越受矚目,效率也更高。如今,該接口

2017-11-18 02:36:14 3195

3195

在從事高速數據擷取設計時使用FPGA的人大概都聽過新JEDEC標準「JESD204B」的名號。近期許多工程師均聯絡德州儀器,希望進一步了解 JESD204B 接口,包括與FPGA如何互動、JESD204B如何讓他們的設計更容易執行等。本文介紹 JESD204B標準演進,以及對系統設計工程師有何影響。

2017-11-18 02:57:01 13942

13942 目前,將JESD204B作為高速數據轉換器首選數字接口的趨勢如火如荼。JESD204接口于2006年首次發布,2008年改版為JESD204A,2011年8月再改版為目前的JESD204

2017-11-18 06:07:01 13946

13946

開發串行接口業界標準JESD204A的目的在于解決以高效率且省錢的方式互連最新寬帶數據轉換器與其他系統IC的問題。其動機在于通過采用可調整高速串行接口,對接口進行標準化,降低數據轉換器與其他設備

2017-11-18 07:31:01 2111

2111

隨著數模轉換器的轉換速率越來越高,JESD204B 串行接口已經越來越多地廣泛用在數模轉換器上,其對器件時鐘和同步時鐘之間的時序關系有著嚴格需求。本文就重點講解了JESD204B 數模轉換器的時鐘

2017-11-18 08:00:01 1831

1831 JESD204B是最新的12.5 Gb/s高速、高分辨率數據轉換器串行接口標準。轉換器制造商的相關產品已進入市場,并且支持JESD204B標準的產品預計會在不久的將來大量面世。JESD204B接口

2017-11-18 18:57:16 2789

2789

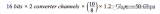

在此設置中,由于AD9250中沒有其他數字處理任務,所以JESD204B鏈路(JESD204B發射器)一目了然。對于JESD204B鏈路來說,通道A為轉換器“0”( M0 ),而通道B為轉換器“1”(M1),這就意味著“M”的值為2。此設置的總線路速率為

2018-08-24 11:47:52 4212

4212

來自ADI公司和Xilinx公司的專家齊聚一堂,共同展示兩種JESD204B A/D轉換器至FPGA設計,同時介紹其實現技巧。

2019-07-03 06:14:00 1959

1959 來自ADI公司和Xilinx公司的專家齊聚一堂,共同講解JESD204B介面標準的重要性,同時介紹它在A/D轉換器到FPGA設計中的作用。

2019-07-03 06:13:00 1291

1291 使用JESD204B兼容型AD9250 A/D轉換器進行快速原型開發。 這款器件隨FMC板提供,同時提供在線軟件和支持,是利用ADI的JESD204B數據轉換器連接Xilinx Kintex和Virtex FPGA的一種更快、更簡單的方式。

2019-06-25 06:16:00 2134

2134

來自ADI公司和Xilinx公司的專家共同展示兩種JESD204B A/D轉換器轉FPGA設置,同時介紹其實現技巧。

2019-06-21 06:01:00 2084

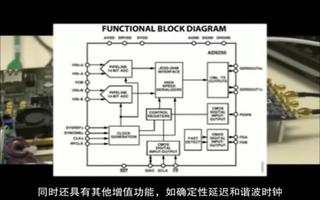

2084 ADI Jesd204B在線研討會系列第4講,討論確定性延遲和多芯片同步,以及在ADI轉換器產品中的實現方式。

2019-06-11 06:16:00 2259

2259

AD9644是一款低功耗、高速14位ADC,集成JESD204A數據轉換器串行接口,使設計人員可以擴展傳輸長度,同時還能改進信號完整性,簡化印刷電路板布局。

2019-08-12 06:20:00 2197

2197 真正的串行接口(稱作JESD204)。JESD204 接口被定義為一種單通道、高速串行鏈路,其使用高達3.125 Gbps 的數據速率把單個或者多個數據轉換器連接至數字邏輯器件。

2019-05-13 09:16:42 12563

12563

2006年4月,JESD204最初版本發布。該版本描述了轉換器和接收器(通常是FPGA或ASIC)之間數Gb的串行數據鏈路。在 JESD204的最初版本中,串行數據鏈路被定義為一個或多個轉換器和接收器之間的單串行通道。

2021-01-04 16:27:22 2596

2596

AD9656:四通道、16位、125 MSPS JESD204B 1.8 V模數轉換器(ADC)

2021-03-19 06:14:59 14

14 AD9683:14位、170 MSPS/250 MSPS、JESD204B模數轉換器

2021-03-19 09:16:10 9

9 AD9680: 14位、1000 MSPS JESD204B雙通道模數轉換器

2021-03-22 09:22:01 12

12 AD9083:16通道、125 MHz帶寬、JESD204B模數轉換器數據表

2021-03-22 16:33:38 13

13 AD9207:12位、6 GSPS、JESD204B/C雙模數轉換器初步數據表

2021-03-22 16:52:38 13

13 驗證ADI轉換器與Xilinx FPGA和JESD204B/C IP的互操作性

2021-04-09 14:37:51 13

13 AD9689:14位,2.0 GSPS/2.6 GSPS,JESD204B,雙模擬到數字轉換器數據Sheet

2021-04-21 19:01:52 17

17 AD9697:14位,1300 MSPS,JESD204B,模擬到數字轉換器數據Sheet

2021-05-13 09:18:42 5

5 AD9213:12位,6 GSPS/10.25 GSPS,JESD204B,RF模擬到數字轉換器數據Sheet

2021-05-17 19:23:17 6

6 AD9694:14位、500 MSPS、JESD204B、四路模數轉換器數據表

2021-05-23 20:37:17 12

12 AD9250:14位、170 MSPS/250 MSPS、JESD204B、雙模數轉換器數據表

2021-05-25 08:21:22 9

9 驗證ADI轉換器與Xilinx FPGA和JESD204BC IP的互操作性

2021-06-02 12:36:44 8

8 它如何同 FPGA 協作。他們特別感興趣的是 JESD204B 接口將如何簡化設計流程。

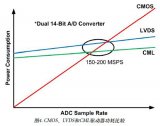

與 LVDS 及 CMOS 接口相比,JESD204B 數據轉換器串行接口標準可提供一些顯著的優勢,包括更簡單

2021-11-10 09:43:33 528

528

如何構建您的JESD204B 鏈路

2022-11-04 09:52:11 3

3 JESD204B:適合您嗎?

2022-11-07 08:07:23 0

0 JESD204A/JESD204B串行接口行業標準旨在解決以高效和節省成本的方式將最新的寬帶數據轉換器與其他系統IC互連的問題。其動機是標準化接口,通過使用可擴展的高速串行接口,減少數據轉換器與其他設備(如現場可編程門陣列(FGPA)和片上系統(SoC))設備)之間的數字輸入/輸出數量。

2022-12-21 14:44:20 966

966

JESD204是一款高速串行接口,用于將數據轉換器(ADC和DAC)連接到邏輯器件。該標準的修訂版B支持高達12.5 Gbps的串行數據速率,并確保JESD204鏈路上的可重復確定性延遲。隨著轉換器速度和分辨率的不斷提高,JESD204B接口在ADI公司的高速轉換器和集成RF收發器中變得越來越普遍。

2023-01-09 16:41:38 2968

2968

LMK04821系列器件為該話題提供了很好的范例研究素材,因為它們是高性能的雙環路抖動清除器,可在具有器件和SYSREF時鐘的子類1時鐘方案里驅動多達七個JESD204B轉換器或邏輯器件。圖1是典型JESD204B系統(以LMK04821系列器件作為時鐘解決方案)的高級方框圖。

2023-04-18 09:25:30 919

919

JESD204B規范是JEDEC標準發布的較新版本,適用于數據轉換器和邏輯器件。如果您正在使用FPGA進行高速數據采集設計,您會聽到新的流行詞“JESD204B”。與LVDS和CMOS接口相比,這一較新的版本具有顯著的優勢,因為它包括更簡單的布局和更少的引腳數。

2023-05-26 14:49:31 361

361

電子發燒友網為你提供ADI(ADI)AD9694S: 14-Bit, 500 MSPS, JESD 204B, 二次對數字轉換器數據表相關產品參數、數據手冊,更有AD9694S: 14-Bit

2023-10-08 16:48:36

電子發燒友網為你提供ADI(ADI)AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet相關產品參數、數據手冊,更有AD9207

2023-10-16 19:02:55

電子發燒友App

電子發燒友App

評論