由于FPGA技術(shù)和ARM技術(shù)應用越來越廣泛,通過設(shè)計并行總線接口來實現(xiàn)兩者之間的數(shù)據(jù)交換,可以較容易地解決快速傳輸數(shù)據(jù)的需求,因此設(shè)計滿足系統(tǒng)要求的FPGA并行總線顯得尤為重要。本文設(shè)計的FPGA的ARM外部并行總線接口,滿足了總線的時序要求,并在某航空機載雷達應答機中進行了應用.

2013-08-15 10:44:19 7204

7204

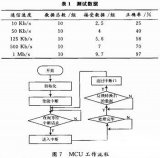

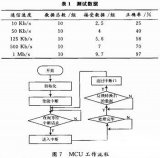

本文介紹了以FPGA為控制核心,以cypress的FX3系列CYUSB3014芯片為總線接口芯片,實現(xiàn)了對USB3.0總線技術(shù)的開發(fā)應用,實際測試的傳輸速度能夠達到1.43Gbps。##FPGA邏輯分析及接口模塊##測試結(jié)果及分析。

2014-03-25 13:57:02 21822

21822 在進行FPGA原型驗證的過程中,當要把大型的SoC進行FPGA原型驗證時,有時候會遇到一種情況,同樣的接口分兩組出去到不同的模塊,而這兩個模塊規(guī)模較大,又需要分割在兩片FPGA中,這時候就會像下圖一樣:

2023-04-25 11:15:20 1629

1629

必須被下游模塊實時處理。上圖就明白了:這一模式實際上是對AXI總線的簡化,很多場合下并不完全需要AXI總線強大的流控功能,特別是在AXI總線模塊的上下游均為可進行實時處理的FPGA邏輯電路的情況下

2018-08-13 09:27:32

為活動(已配置)狀態(tài)。FPGA包括許多配置接口選項,通常包括并行NOR總線和串行外設(shè)接口(SPI)總線。支持這些總線的存儲器在不同廠商的產(chǎn)品之間總是存在微小的不兼容性,增添了采購多款存儲器件的困難程度

2021-09-03 07:00:00

簡述CAN總線最近公司開發(fā)CAN總線項目,以前也學習了,沒有實際的用于項目制作,現(xiàn)在具體的總結(jié)一下,也是借鑒了很多大神的資料,站在巨人的肩膀之上寫下來這篇文章CAN 是 Controller

2021-08-19 09:00:26

I2C總線概述及時序,看完你就懂了

2021-05-24 06:42:06

IDDR與ODDR的簡述RGMII時序簡述千兆網(wǎng)輸入與輸出模塊的設(shè)計測試模塊的設(shè)計仿真測試結(jié)果總結(jié)

2021-01-22 06:09:37

1. SDIO 接口簡述SDIO 接口用于訪問 MMC 卡,SD 存儲卡或者 SDI/O 卡的接口標準。這里要做的是 Micro SDCard,也就是 TF Card(存儲卡)的操作。屬于第二種。本

2021-08-05 06:34:06

Simulink嵌入式自動代碼DSP F28335(3)ePWM模塊詳解及應用例程簡述1、模塊介紹1.1 General界面1.2 ePWMA界面1.3 ePWMB界面1.4 Counter

2021-12-15 06:56:41

`本節(jié)知識介紹:FPGA接口實現(xiàn)文本液晶顯示模塊文本液晶顯示模塊是基于廉價和易于使用微控制器或FPGA接口實現(xiàn)的。下面是一個1行×16字符模塊:要控制液晶顯示模塊,你需要11個IO引腳來驅(qū)動一個8

2012-03-14 11:11:15

和節(jié)省資源的。它能夠保證整個系統(tǒng)的可靠,穩(wěn)定和高效。FPGA 的邏輯模塊圖如圖3 所示。FPGA 內(nèi)部邏輯大致分為RESET 模塊,DS18B20 接口模塊,總線控制模塊,DSP 接口模塊,雙口RAM

2019-06-18 05:00:08

你好,我想和FPGA接口,想聽聽我有什么選擇。我正在查看數(shù)據(jù)表頁21中的外部存儲器接口部分5.6,我看到它有一個并行數(shù)據(jù)總線、并行地址總線和一些控制信號。我需要更多地了解這個問題,但是有人能告訴我

2018-11-15 14:08:43

一、模塊題目二、原理簡述串行接口作為51單片機的重要外設(shè),編程操作并不復雜,但在實際的項目應用中,由于數(shù)據(jù)結(jié)構(gòu)和通信規(guī)約的不同,其程序邏輯也有各種變化。一般情況下,上位機的命令可能不是一個字節(jié),而是

2022-01-11 07:10:36

等串行總線接口只能實現(xiàn)FPGA 和ARM 之間的低速通信 ;當傳輸?shù)臄?shù)據(jù)量較大.要求高速傳輸時,就需要用并行總線來進行兩者之間的高速數(shù)據(jù)傳輸.

2019-09-17 06:21:10

。因為工控機的總線為PC104,因此需要設(shè)計PC104與DSP之間的通信接口。系統(tǒng)中以Altera公司的一片FPGA芯片EPlK50來對該接口和數(shù)據(jù)采集過程中的邏輯控制與FIFO進行設(shè)計。下面主要闡述

2019-05-07 07:00:09

單片機與FPGA總線接口邏輯設(shè)計1、利用FPGA內(nèi)部RAM存儲256個字節(jié)數(shù)據(jù),并將數(shù)據(jù)發(fā)送到單片機并在串口調(diào)試工具顯示;2、通過串口調(diào)試工具經(jīng)單片機發(fā)送數(shù)據(jù)到FPGA,并通過LED顯示。

2012-03-04 13:09:58

功能描述及參數(shù)設(shè)置按照PCIE協(xié)議的要求,該FPGA的IP核也采用三層體系結(jié)構(gòu),即傳輸層、數(shù)據(jù)鏈路層和物理層。這三層功能模塊完成了PCIE的協(xié)議轉(zhuǎn)換,在傳輸層上給開發(fā)人員提供了非常豐富的接口。開發(fā)人員

2019-05-21 05:00:02

基于FPGA的PCI總線接口設(shè)計

2017-09-30 09:12:46

基于FPGA的PCI總線接口設(shè)計

2020-03-15 11:43:10

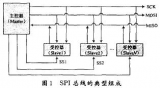

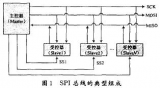

語言,他可以用來進行各種級別的邏輯設(shè)計,可以用來進行數(shù)字邏輯系統(tǒng)的仿真驗證、時序分析和邏輯綜合等,應用十分廣泛。本文使用Verilog設(shè)計 SPI接口模塊,實現(xiàn)可IP復用的通用結(jié)構(gòu)。根據(jù)SPI總線

2019-05-28 05:00:05

本文的應用背景為某一工業(yè)測控系統(tǒng),該系統(tǒng)采用FPGA實現(xiàn)測量數(shù)據(jù)的采集和控制信號的輸出,通過定制PCI接口IP實現(xiàn)一個32位目標設(shè)備的PCI總線接口轉(zhuǎn)換。PCI核選用AlteraPCI編譯器所包括

2018-12-04 10:35:21

基于USB的ARINC429總線接口模塊設(shè)計引言 ARINC429總線由美國航天無線電設(shè)備公司所資助,是廣泛應用于當前航空電子設(shè)備中的一種數(shù)據(jù)總線傳輸標準。與傳統(tǒng)的航空電子設(shè)備間

2008-10-14 20:50:02

。在我們設(shè)計的系統(tǒng)中,處理器是Openrisc1200,所用的FLASH是AMD與富士公司的Am29LV160D芯片。利用FPGA實現(xiàn)接口,由于Openrisc1200(OR1200)采用

2018-12-05 10:35:32

內(nèi)容簡介本書基于XILINX的嵌入式開發(fā)平臺,講解了嵌入式系統(tǒng)的基本概念、FPGA和MicroBlaze處理器以及最新的多端口內(nèi)存控制器(MPMC)的原理。[1]通過不同的總線和接口實驗,詳細講述了

2017-12-08 14:27:35

什么是DSP流水線協(xié)議?如何利用FPGA與ADSP TS201去設(shè)計總線接口?

2021-04-28 06:31:06

在雷達信號處理、數(shù)字圖像處理等領(lǐng)域中,信號處理的實時性至關(guān)重要。由于FPGA芯片在大數(shù)據(jù)量的底層算法處理上的優(yōu)勢及DSP芯片在復雜算法處理上的優(yōu)勢,DSP+FPGA的實時信號處理系統(tǒng)的應用越來越廣泛。那么,我們該怎么利用FPGA與ADSP TS201設(shè)計總線接口呢?

2019-08-09 06:56:11

PCI總線是什么?有什么特點?如何利用FPGA去設(shè)計PCI總線的接口電路?設(shè)計PCI總線接口時應注意哪些問題?

2021-05-31 06:37:24

本文將以嵌入式實時視頻數(shù)據(jù)存儲系統(tǒng)為例,說明如何利用FPGA作為嵌入式處理器的數(shù)據(jù)協(xié)處理器,利用CPLD進行主處理器與協(xié)處理器之間數(shù)據(jù)通信的方案來解決處理器接口總線速度對系統(tǒng)性能的影響。該方案對解決類似的問題具有一定的參考作用。

2021-05-10 06:30:18

什么是PCI總線?它有什么特點?如何利用FPGA設(shè)計PCI總線的接口電路?設(shè)計PCI總線接口時應注意哪些問題?

2021-04-29 06:10:31

總線的FPGA接口? FPGA必須插在服務(wù)器主板上嗎?它可以與普通的服務(wù)器主板連接嗎?我的問題是我只能在電路板底部表面的過孔處點擊QPI信號,并需要某種連接器來連接FPGA。謝謝!

2020-03-13 10:05:34

本文設(shè)計一款基于2.4G射頻的車栽CAN總線故障診斷儀,詳細介紹其工作原理及系統(tǒng)硬件電路,最后分別闡述接收端、發(fā)射端和PC端的軟件模塊。該方案采用自動跳頻的2.4G空中協(xié)議,經(jīng)測試統(tǒng)計誤碼率保持在

2021-05-13 06:49:39

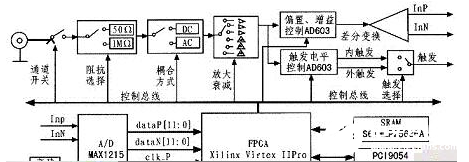

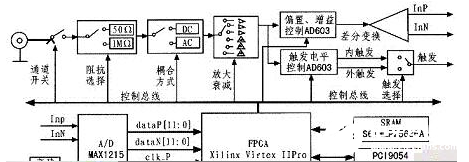

本文給出了基于PXI總線接口的高速數(shù)字化儀模塊的設(shè)計實現(xiàn)方法,介紹了高速數(shù)據(jù)采集系統(tǒng)中LVDS接口、LVPECL接口電路結(jié)構(gòu)及連接方式,并在所設(shè)計的數(shù)字化儀模塊中得到應用。

2021-04-14 06:18:38

受到限制。因此,我們采用ALTERA公司的FPGA器件設(shè)計SPI總線的通信接口,該總線接口具有高速、配置靈活等優(yōu)點,大大地縮短了系統(tǒng)的開發(fā)周期。

2019-08-09 08:14:34

求一個avalon總線和CY7C68013A的接口轉(zhuǎn)換模塊verilog代碼

2014-05-15 13:06:30

PCI總線特點及開發(fā)現(xiàn)狀PCI接口配置空間的實現(xiàn)求一款在PCI總線上利用FPGA技術(shù)設(shè)計PCI總線接口的設(shè)計方案

2021-04-15 06:17:20

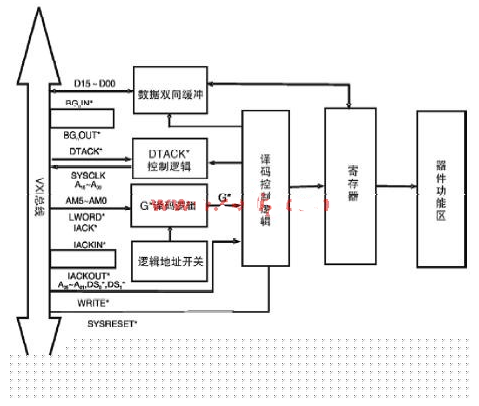

領(lǐng)域。本文基于雷達實時信號處理的需要,用FPGA實現(xiàn)了多DSP信號處理模板局部總線和基于標準VME總線的計算機進行通信的接口設(shè)計。 2 VME總線的功能特點VME總線系統(tǒng)的功能結(jié)構(gòu)可以分為4類:數(shù)據(jù)傳輸

2019-04-22 07:00:07

求一種基于USB總線的ARINC429總線接口模塊的設(shè)計方案。

2021-04-30 07:01:51

。智能無線電技術(shù)(1):軟件無線電和認知無線電的技術(shù)概述及應用圖1 軟件無線電體系框架 對于軟件無線電,人們關(guān)注最多的是它的組成結(jié)構(gòu)、硬件實現(xiàn)、技術(shù)可行性等,一開始很少有人關(guān)心軟件無線電的理論支撐,因此

2018-08-21 15:23:16

信號時序復雜等,用戶使用時往往覺得困難,另外,該IP核不是免費的。基于此,本文將提出一種新的基于FPGA的SPI接口設(shè)計方法。二、SPI總線原理SPI總線由四根線組成: 串行時鐘線(SCK),主機輸出

2019-05-05 09:29:34

和高效。FPGA的邏輯模塊圖如圖 3所示。FPGA內(nèi)部邏輯大致分為 RESET模塊,DS18B20接口模塊,總線控制模塊,DSP接口模塊,雙口 RAM模塊,232接口模塊和 DAC接口模塊等幾部分。(1

2020-08-19 09:29:48

核處理器NIOSⅡ作為系統(tǒng)的主控制器,結(jié)合ARINC429專用器件和其他外圍設(shè)備實現(xiàn)數(shù)據(jù)的收發(fā)功能。 ARI NC429接口板由數(shù)據(jù)收發(fā)、存儲器擴展、監(jiān)控、PCI總線接口等模塊組成。NIOSⅡ控制

2019-04-26 07:00:08

3.1 總線與接口概述 3.1.1 總線和接口及其標準的概念 總線:是在模塊和模塊之間或設(shè)備與設(shè)備之間的一組進行互連和傳輸信息的信號線,信息包括指令、數(shù)據(jù)和地址。

2009-03-25 13:28:07 31

31 總線型低壓差分信號(BLVDS)是一種性能優(yōu)良的物理層接口標準。本文介紹一種基于總線型LVDS 的通信系統(tǒng)方案,以及利用FPGA 芯片實現(xiàn)系統(tǒng)核心模塊的設(shè)計方法。該方案可廣泛使用

2009-04-16 10:14:12 20

20 總線型低壓差分信號(BLVDS)是一種性能優(yōu)良的物理層接口標準。本文介紹一種基于總線型LVDS 的通信系統(tǒng)方案,以及利用FPGA 芯片實現(xiàn)系統(tǒng)核心模塊的設(shè)計方法。該方案可廣泛

2009-05-31 15:43:09 17

17 基于FPGA的PCI總線接口設(shè)計::PCI是一種高性能的局部總線規(guī)范,可實現(xiàn)各種功能標準的PCI總線卡。本文簡要介紹了PCI總線的特點、信號與命令,提出了一種利用高速FPGA實現(xiàn)PCI總線接

2009-06-25 08:17:18 48

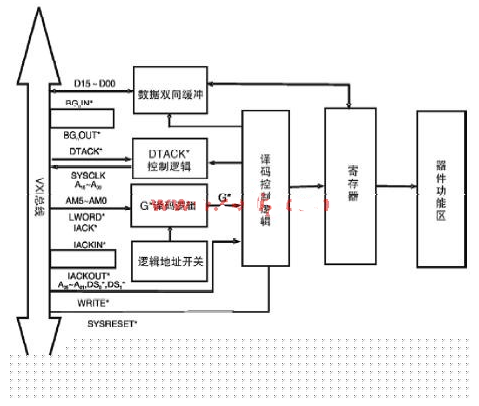

48 基于VXI總線的射頻多路轉(zhuǎn)接器在測控系統(tǒng)中有廣泛的應用。按照VXI總線PnP規(guī)范,采用FPGA+RELAYS的方法實現(xiàn)該模塊的設(shè)計。該模塊是一種單槽、C尺寸、寄存器基器件。用一塊FPGA實現(xiàn)VX

2009-07-06 16:30:21 21

21 回顧了測量與控制領(lǐng)域的接口總線技術(shù)發(fā)展,分析了進入IT時代接口總線技術(shù)面臨的特點,簡述了中間件對策,安全對策,自治化對策三個方面的發(fā)展思路。進入21世紀,人類來到

2009-07-15 10:10:38 10

10 簡述了I2C總線的特點;介紹了開發(fā)FPGA時I2C總線模塊的設(shè)計思想;給出并解釋了用Verilog HDL實現(xiàn)部分I2C總線功能的程序,以及I2C總線主從模式下的仿真時序圖。

2009-10-19 10:49:16 104

104 本實驗是基于EasyFPGA030的I2C總線接口模塊設(shè)計,用EasyFPGA030開發(fā)套件通過I2C協(xié)議實現(xiàn)對二線制I2C串行EEPROM的讀寫操作,先把數(shù)據(jù)寫入EEPROM,然后再讀取出來顯示在數(shù)碼管上

2009-11-02 17:01:45 41

41 本實驗是基于EasyFPGA030的I2C總線接口模塊設(shè)計,用EasyFPGA030開發(fā)套件通過I2C協(xié)議實現(xiàn)對二線制I2C串行EEPROM的讀寫操作,先把數(shù)據(jù)寫入EEPROM,然后再讀取出來顯示在數(shù)碼管上。

2010-03-11 15:37:32 29

29 本文介紹了一種FPGA和IPX2805之間的SPI4.2接口模塊設(shè)計的方法,對硬件設(shè)計進行了說明,著重闡述了FPGA內(nèi)部SPI4.2接口模塊設(shè)計。該設(shè)計簡單、高效,解決了商用芯片不能滿足高速轉(zhuǎn)發(fā)的系

2010-07-28 16:56:32 33

33 摘 要 :PCI是一種高性能的局部總線規(guī)范,可實現(xiàn)各種功能標準的PCI總線卡。本文簡要介紹了PCI總線的特點、信號與命令,提出了一種利用高速FPGA實現(xiàn)PCI總線接口的

2009-06-20 13:13:28 936

936

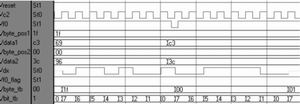

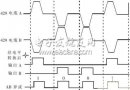

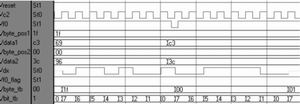

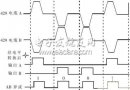

摘要: 簡述了I2C總線的特點;介紹了開發(fā)FPGA時I2C總線模塊的設(shè)計思想;給出并解釋了用Verilog HDL實現(xiàn)部分I2C總線功能的程序,以及I2C總線主從模式下的仿真時序圖

2009-06-20 13:17:08 6620

6620

摘要:總線型低壓差分信號(BLVDS)是一種性能優(yōu)良的物理層接口標準。本文介紹一種基于總線型LVDS的通信系統(tǒng)方案,以及利用FPGA芯片實現(xiàn)系統(tǒng)核心模塊的設(shè)計方

2009-06-20 13:48:12 5850

5850

ST-BUS總線接口模塊的Verilog HDL設(shè)計

ST-BUS是廣泛應用于E1通信設(shè)備內(nèi)部的一種模塊間通信總線。結(jié)合某專用通信系統(tǒng)E1接口轉(zhuǎn)換板的設(shè)計,本文對ST-BUS

2009-09-26 18:01:13 2241

2241

FPGA與ADSP TS201的總線接口設(shè)計

在雷達信號處理、數(shù)字圖像處理等領(lǐng)域中,信號處理的實時性至關(guān)重要。由于FPGA芯片在大數(shù)據(jù)量的底層算法處理上的優(yōu)勢及DSP芯片在復雜

2009-12-11 10:13:29 2356

2356 LED的內(nèi)量子效率與電-光效率簡述及計算

摘要:在LED的PN結(jié)上施加正向電壓時,PN結(jié)會有電流流過。電子和空穴在PN結(jié)過渡層中復合會產(chǎn)生光子,然

2010-05-11 08:57:51 4801

4801 為解決1394b 光纖總線在軍用車輛領(lǐng)域應用過程中的設(shè)備兼容性問題,基于1394b 異步傳輸機制,采用FPGA 作為中心處理器完成1394b 接口設(shè)計。并以實現(xiàn)PC 機1394b 接口與PC 機串口之間通信為

2011-05-12 17:56:34 94

94 SPI 串行總線是一種常用的標準接口,其使用簡單方便而且占用系統(tǒng)資源少,應用相當廣泛。本文將介紹一種新的通用的SPI 總線的FPGA 實現(xiàn)方法。

2011-09-09 11:58:27 67

67 在深入研究1553B 總線標準的基礎(chǔ)上, 介紹了一種基于FPGA 的總線接口通信模塊的芯片設(shè)計方法。給出了總體設(shè)計方案,從模擬和數(shù)字兩方面分析了各功能模塊。最后在Xilinx 軟件中用VHD

2011-09-20 17:09:50 3227

3227

ARINC429總線接口板的研制,實現(xiàn)多通道 ARINC429總線 數(shù)據(jù)的接收和發(fā)送,成為目前對飛機機載總線接口研究的重點。 1 ARINC429總線簡介 在現(xiàn)代民用飛機上,系統(tǒng)與系統(tǒng)之間、系統(tǒng)與部件之

2011-10-05 16:07:15 1955

1955

關(guān)于WiFi網(wǎng)絡(luò)的簡述及構(gòu)建講解

2011-11-08 17:40:32 202

202 CAN總線是較為流行的技術(shù),介紹了CAN總線的主要特性,簡述了SJAl000和PCA82C250的結(jié)構(gòu)和工作原理,并基于此設(shè)計了CAN總線接口,給出了系統(tǒng)硬件電路設(shè)計和SJAl000的初始化、接收、發(fā)送報

2011-11-17 17:21:28 439

439 介紹了基于硬件描述語言Verilog HDL設(shè)計的SDX總線與Wishbone總線接口轉(zhuǎn)化的設(shè)計與實現(xiàn),并通過Modelsim進行功能仿真,在QuartusⅡ軟件平臺上綜合,最終在Altera公司的CycloneⅢ系列FPGA上調(diào)試。實驗

2012-01-11 10:21:21 25

25 本文設(shè)計一個通信接口模塊,通過光纖接口與中心機連接,實現(xiàn)對前端受控模塊的遠程控制和狀態(tài)監(jiān)測。

2012-09-03 15:59:18 4808

4808

簡述FPGA_和DSP的優(yōu)缺點及使用場合,實用版

2016-02-16 17:07:02 14

14 Xilinx FPGA工程例子源碼:用FPGA模擬VGA時序PS_2總線的鍵盤接口VHDL源代碼

2016-06-07 15:11:20 32

32 SPI 接口應用十分廣泛,在很多情況下,人們會用軟件模擬的方法來產(chǎn)生SPI 時序或是采用帶SPI 功能模塊的MCU。但隨著可編程邏輯技術(shù)的發(fā)展,人們往往需要自己設(shè)計簡單的SPI 發(fā)送模塊。本文介紹

2017-10-19 10:33:01 18

18 基于FPGA的高速DSP與液晶模塊接口的實現(xiàn)

2017-10-19 13:46:23 3

3 基于FPGA的VME總線與DSP通信接口設(shè)計

2017-10-19 13:49:30 26

26 和在PCM-5825上驗證接口設(shè)計的X86匯編語言程序。 關(guān)鍵詞 DSP HPI PC104總線 FPGA VHDL源代碼 在一款嵌入式數(shù)據(jù)采集系統(tǒng)的設(shè)計中,采用TMS320VC54

2017-11-06 14:30:42 3

3 為降低成本,提高設(shè)計靈活性,提出一種基于FPGA的1553B總線接口方案;采用自頂向下的設(shè)計方法,在分析1553B總線接口工作原理和響應流程的基礎(chǔ)上,完成了接口方案各FPGA功能模塊設(shè)計;對關(guān)鍵模塊

2017-11-17 13:47:25 19841

19841 NI VeriStand是一款用于配置實時測試系統(tǒng)應用的軟件環(huán)境,如硬件在環(huán)(HIL)測試系統(tǒng)等。當向NI VeriStand添加實時I/O接口時,用戶能夠快速配置多種標準模擬、數(shù)字和通信總線接口

2017-11-18 07:47:35 8845

8845

在基于FPGA芯片的工程實踐中,經(jīng)常需要FPGA與上位機或其他處理器進行通信,為此設(shè)計了用于短距離通信的UART接口模塊。該模塊的程序采用VHDL語言編寫,模塊的核心發(fā)送和接收子模塊均采用有限狀態(tài)機

2017-11-18 11:33:01 5152

5152 為了擴展VME總線和CAN總線的應用范圍,充分利用兩種總線的不同傳輸特點,采用了模塊設(shè)計方法,提出一種基于FPGA和MCU的總線轉(zhuǎn)換方案。該方案給出了FPGA與上位VME總線部分的VME總線接口

2018-07-17 10:11:00 3239

3239

資源,使其有機結(jié)合,縮短開發(fā)周期,適應市場需要。基于這種需求,設(shè)計了MCS51單片機與FPGA/CPLD的總線接口邏輯電路,實現(xiàn)了單片機與FPGA/CPLD數(shù)據(jù)與控制信息的可靠通信,使FPGA/CPLD與單片機優(yōu)勢互補,組成靈活的、軟硬件都可現(xiàn)場編程的控制系統(tǒng)。

2017-11-23 09:37:14 3407

3407 FPGA 動態(tài)局部可重構(gòu)技術(shù)通常將系統(tǒng)劃分為固定模塊和可重構(gòu)模塊,可重構(gòu)模塊與其他模塊之間的通信都是通過使用特殊的總線宏實現(xiàn)的。總線宏的正確設(shè)計是實現(xiàn)FPGA 動態(tài)局部可重構(gòu)技術(shù)的關(guān)鍵。在研究

2018-12-14 14:27:35 3

3 等串行總線接口只能實現(xiàn)FPGA 和ARM 之間的低速通信 ;當傳輸?shù)臄?shù)據(jù)量較大.要求高速傳輸時,就需要用并行總線來進行兩者之間的高速數(shù)據(jù)傳輸.

2019-08-08 15:37:50 5863

5863

針對OLED模塊應用中8位數(shù)據(jù)并行接口占用單片機I/O管腳較多的問題,本文介紹了SPI總線接口在OLED模塊中的應用,并以VGG12864L-S002顯示模塊為例,進行了相應的硬件、軟件設(shè)計。在實際應用中,采用SPI方式達到了并行接口方式的效果,同時簡化了電路設(shè)計,節(jié)約了I/O管腳。

2019-11-21 16:39:56 7

7 PXI總線是NI公司在計算機外設(shè)總線PCI的基礎(chǔ)上實現(xiàn)的新一代儀器總線,已經(jīng)成為業(yè)界開放式總線的標準,基于PXI總線的數(shù)字化儀模塊是現(xiàn)代測 試系統(tǒng)中重要的一種數(shù)據(jù)記錄與處理設(shè)備。設(shè)計一個雙通道12

2020-03-15 16:45:00 1832

1832

采用;另一種是利用中、小規(guī)模電路基PAL、GAL、CPLD和FPGA實現(xiàn)。通過利用FPGA實現(xiàn)模塊與VXI總線接口的設(shè)計過程中,總結(jié)出一些通用的設(shè)計思路。

2020-07-27 18:11:22 789

789

FPGA完成ARINC429總線數(shù)據(jù)的接收。重點介紹接口電路設(shè)計和FPGA中的軟件開發(fā),與傳統(tǒng)的ARINC429總線數(shù)據(jù)接收系統(tǒng)相比,具有接口電路簡單、具備一定的抗干擾能力、不受協(xié)議芯片速率限制等優(yōu)點.此方法已成功應用于產(chǎn)品中。并對其他串行總線數(shù)據(jù)接收具有借鑒意義。

2021-02-03 15:53:00 38

38 本文首先介紹了箭載測試系統(tǒng)的總體設(shè)計方案,包括 F C AE 1553 總線的基本特性、層次模型、 拓撲結(jié)構(gòu) 、 協(xié)議各層功能 分析 等 ,以及總線接口模塊的設(shè)計方案和功能組成等 。

2021-04-09 17:18:17 6

6 機器視覺檢測系統(tǒng)簡述及系統(tǒng)構(gòu)成說明。

2021-04-19 15:26:58 11

11 麥可科技研發(fā)的CAN總線接口模塊、擁有2/4路獨立CAN通道。 板載的120歐姆終端電阻,用戶可以根據(jù)使用情況,用跳線選擇,當節(jié)點為端節(jié)點時應連接該電阻。

2021-04-20 10:32:55 20

20 設(shè)計了一種基于CPCI總線標準的PMC接口載板。載板以FPGA為核心,集成了CPCI接口模塊和DPRAM(雙口RAM)模塊,CPCI接口模

2021-05-05 16:56:00 3055

3055

簡 介: 集成電路設(shè)計越來越向系統(tǒng)級的方向發(fā)展,并且越來越強調(diào)模塊化的設(shè)計。SPI(Serial Peripheral Bus)總線是Motorola公司提出的一個同步串行外設(shè)接口,容許CPU

2021-05-29 10:16:26 4456

4456

基于FPGA嵌入式硬核的PCIExpress總線接口設(shè)計與驗證(嵌入式開發(fā)架構(gòu))-該文檔為基于FPGA嵌入式硬核的PCIExpress總線接口設(shè)計與驗證講解文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 15:23:37 7

7 虹科多總線接口電流監(jiān)測模塊提供8通道20位電流監(jiān)測通道,可實現(xiàn)電壓,電流,功率,電能和電量的同時測量,模塊提供多種通訊接口,包括RS485,CAN和USB,可以方便地實現(xiàn)數(shù)據(jù)通訊。

2023-03-22 10:33:17 608

608

電子發(fā)燒友App

電子發(fā)燒友App

評論